# *University of Pennsylvania* Department of Electrical Engineering

# A VLSI COMPUTATIONAL SENSOR FOR THE DETECTION OF IMAGE FEATURES

Masatoshi Nishimura

A PH.D DISSERTATION

in Electrical Engineering

Philadelphia, PA 19104

## A VLSI COMPUTATIONAL SENSOR FOR THE DETECTION OF IMAGE FEATURES

Masatoshi Nishimura

### A DISSERTATION

in

**Electrical Engineering**

Presented to the Faculties of the University of Pennsylvania in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

2001

Jan Van der Spiegel Supervisor of Dissertation

Kenneth R. Laker Graduate Group Chairperson Copyright

Masatoshi Nishimura

2001

Dedicated to Kazuko, Taku, and Mizuki

### ACKNOWLEDGEMENT

It has been a long journey. I would really like to thank everyone who helped me reach this stage.

My first thanks go to my advisor, Professor Van der Spiegel. He gave me the opportunity to work on this research project and guided me over the years to the point where I am now. I learned a lot from his vast knowledge and intellectual insight. His encouragement and support were invaluable for me. I would also like to thank the other members of the committee: Professors Farhat, Laker, Mueller, and Santiago-Aviles for carefully reading my thesis and giving me suggestive questions and advice. I wish Professor Ketterer were still alive, from whom I learned the unique style of thinking. My colleagues, Ralph, Chris, and Pervez, are thanked for their help in almost every aspect during my stay at Penn. Special thanks to Ralph. You are a good friend. Thanks for the staff members of the EE department, especially Renee and Lois.

Many people at Sankyo are greatly appreciated. Especially Dr. Saito, for whom I cannot find words to express my gratitude. He inspired and motivated me to become a good researcher. I would also like to express my gratitude to Dr. Baba, Dr. Iwata, and Dr. Koike, who gave me the opportunity to study in the States, and Dr. Nakamura and Dr. Haruyama, who allowed me to continue and complete my research while staying at Sankyo. I would also like to thank the members of the medical engineering group and the bioinformatics team. Especially Mr. Sekiya, Mr. Takahashi, Dr. Nakatsubo, Mr. Niwayama, Mr. Sunamura, Mr. Mizukami, and Dr. Rajniak.

My final thanks go to my family. My wife, Kazuko, has been instrumental for the completion of my thesis. Without her love, understanding, and constant support, it would have been impossible for me to reach this point. Also, my two children, Taku and Mizuki, who have always been a great source of energy for me. I feel like I have completed this thesis with my family altogether.

### ABSTRACT

#### A VLSI computational sensor for the detection of image features

#### Masatoshi Nishimura

#### Jan Van der Spiegel

A new type of VLSI computational sensor for the detection of image features is presented. The purpose of the proposed sensor is to overcome some of the limitations of pattern recognition systems, which is due to the inherent separation of image capture and analysis. It takes a fairly long time to transfer a huge amount of image data from an image sensor to a host CPU, which makes it difficult for the system to be used in real time applications requiring high speed. The proposed sensor detects important image features such as corners, junctions (T-type, X-type, Y-type) and linestops in a discriminative fashion. The on-chip detection of these features significantly reduces the data amount and hence facilitates the subsequent processing of pattern recognition.

The thesis deals specifically with: (1) development of an algorithm for the feature detection based on template matching; (2) implementation of the algorithm onto VLSI hardware; (3) investigation of a systematic design procedure based on transistor mismatch. The proposed algorithm is inspired by hierarchical integration of features found in the biological vision system. The algorithm first decomposes an input image into a set of line segments in four orientations, and then detects the features based on the interaction between these decomposed line segments. The algorithm is realized in the form of a CMOS sensor. An analog/digital mixed-mode approach is employed to achieve both compact implementation of neighborhood interaction in the analog domain and design flexibility in the digital domain. Experimental results demonstrate the sensor operates at fairly high speed. The circuit design is performed systematically using the proposed procedure to satisfy both accuracy and speed requirement.

### TABLE OF CONTENTS

| Chap | ter 1 Introduction                                         | 1  |

|------|------------------------------------------------------------|----|

| 1.1  | Research background and motivation                         | 1  |

| 1.2  | Contribution of the thesis                                 | 5  |

| Chap | ter 2 Algorithm for feature detection                      | 8  |

| 2.1  | Problem definition                                         | 8  |

| 2.2  | Feature detection and pattern recognition in biology       | 10 |

| 2.3  | Survey of the algorithms for corner and junction detection | 17 |

| 2.4  | Proposed approach                                          | 20 |

| 2.5  | Description of the template matching algorithm             | 24 |

| 2.5. | 1 Basic framework                                          | 24 |

| 2.5. | 2 Relationship with other image processing methods         | 31 |

| 2.5. | 3 Implementation considerations                            | 37 |

| 2.6  | Outline of the processing flow                             | 39 |

| 2.6. | 1 Overall processing flow                                  | 39 |

| 2.6. | 2 Thinning                                                 | 40 |

| 2.6. | 3 Orientation decomposition                                | 42 |

| 2.6. | 4 Line completion                                          | 44 |

| 2.6. | 5 Elimination of isolated points                           | 48 |

| 2.6. | 6 Line inhibition                                          | 50 |

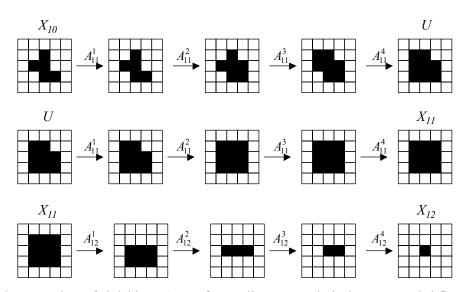

| 2.6. | 7 Line elongation and line thickening                      | 52 |

| 2.6. | 8 Linestop detection                                       | 54 |

| 2.6. | 9 Detection of higher level features                       | 55 |

| 2.6  | .10 Key points of the algorithm                                | 61  |  |

|------|----------------------------------------------------------------|-----|--|

| 2.7  | Evaluation of the algorithm                                    | 62  |  |

| 2.7  | .1 Printed characters                                          | 63  |  |

| 2.7  | .2 Handwritten characters                                      | 70  |  |

| 2.7  | .3 Patterns                                                    | 71  |  |

| 2.7  | .4 Discussion                                                  | 72  |  |

| 2.8  | Summary                                                        | 74  |  |

| 2.9  | References                                                     | 75  |  |

| Chap | oter 3 Architectural design of the sensor                      | 78  |  |

| 3.1  | Overview of related research                                   | 78  |  |

| 3.1  | .1 Phototransduction                                           | 80  |  |

| 3.1  | .2 Processing circuit – analog implementation                  | 85  |  |

| 3.1  | .3 Processing circuit – digital implementation                 | 93  |  |

| 3.1  | .4 Processing circuit – CNN implementation                     | 96  |  |

| 3.1  | .5 The selected architecture                                   | 97  |  |

| 3.2  | Pixel architecture                                             | 99  |  |

| 3.2  | .1 Overall architecture                                        |     |  |

| 3.2  | .2 Phototransistor and thresholding circuit                    | 101 |  |

| 3.2  | .3 Processing circuit                                          |     |  |

| 3.3  | Summary                                                        | 107 |  |

| 3.4  | References                                                     | 107 |  |

| Chap | Chapter 4 Circuit design based on transistor mismatch analysis |     |  |

| 4.1  | Problem definition                                             | 112 |  |

| 4.2  | Transistor mismatch                                            |     |  |

| 113                                                                |

|--------------------------------------------------------------------|

| 117                                                                |

| 122                                                                |

| 126                                                                |

| 132                                                                |

| 132                                                                |

| 134                                                                |

| 142                                                                |

| 148                                                                |

| 153                                                                |

| 155                                                                |

|                                                                    |

| 156                                                                |

| 156<br>157                                                         |

|                                                                    |

| 157                                                                |

| 157<br>158                                                         |

| 157<br>158<br>. <b> 159</b>                                        |

| 157<br>158<br><b>159</b><br>159                                    |

| 157<br>158<br><b> 159</b><br>159<br>163                            |

| 157<br>158<br><b> 159</b><br>159<br>163                            |

| 157<br>158<br><b> 159</b><br>163<br>163<br>167                     |

| 157<br>158<br><b>159</b><br>163<br>163<br>167<br>170               |

| 157<br>158<br><b> 159</b><br>163<br>163<br>167<br>170<br>171       |

| 157<br>158<br>159<br>159<br>163<br>163<br>167<br>170<br>171<br>172 |

|                                                                    |

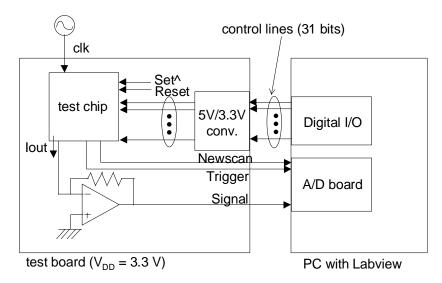

| 5.5. | 1 Testing environment                           | . 178 |

|------|-------------------------------------------------|-------|

| 5.5. | 2 Phototransduction                             | . 179 |

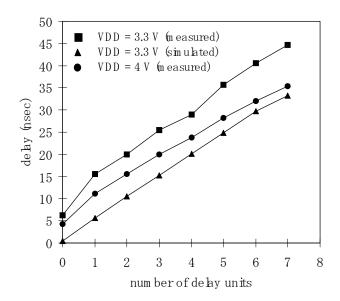

| 5.5. | 3 Programmable delay module                     | . 180 |

| 5.5. | 4 Scanner module                                | . 181 |

| 5.5. | 5 Problems associated with memory configuration | . 181 |

| 5.5. | 6 Pattern generation                            | . 183 |

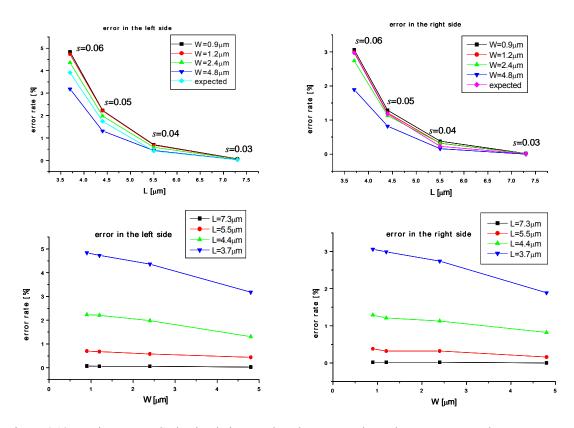

| 5.5. | 7 Mismatch measurement                          | . 185 |

| 5.5. | 8 Speed measurement                             | . 190 |

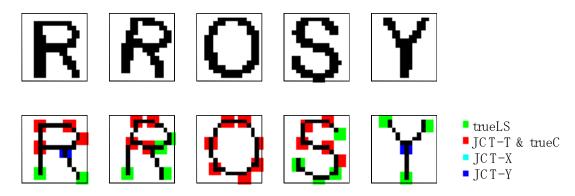

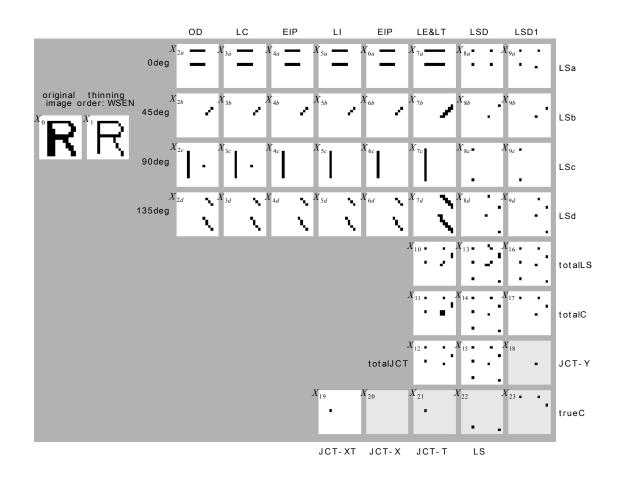

| 5.5. | 9 Responses to letter images                    | . 194 |

| 5.5. | 10 Discussion                                   | . 197 |

| 5.6  | Summary                                         | . 199 |

| 5.7  | References                                      | . 200 |

| Chap | ter 6 Conclusion                                | 201   |

### LIST OF TABLES

| Table 4.1 | Matching proportionality constants for difference processes.                              | 116 |

|-----------|-------------------------------------------------------------------------------------------|-----|

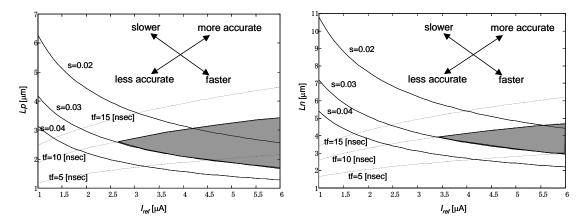

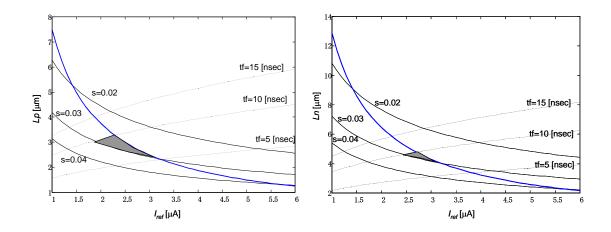

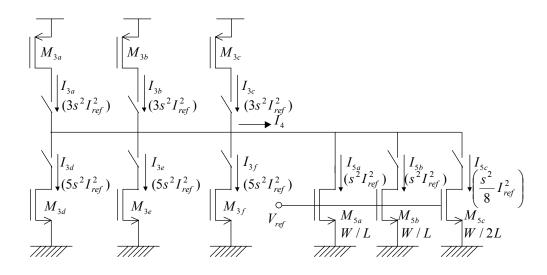

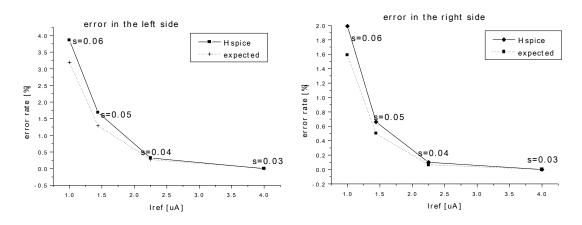

| Table 4.2 | Error rate (%) for $45^{\circ}$ detection as a function of the relative current variation | 138 |

| Table 4.3 | Channel lengths to satisfy the specified accuracy $s$ for different values of $I_{ref.}$  | 140 |

| Table 5.1 | Expected and measured error rate for different values of <i>I<sub>ref</sub></i>           | 188 |

| Table 5.2 | Execution time required for each operation                                                | 195 |

| Table 5.3 | Specifications of the prototype chip                                                      | 199 |

### LIST OF FIGURES

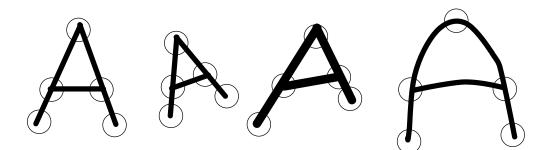

| Figure 1.1  | Various shapes of letter "A".                                                         | 3  |

|-------------|---------------------------------------------------------------------------------------|----|

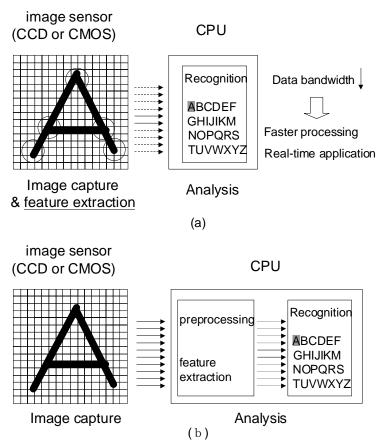

| Figure 1.2  | Two types of pattern recognition systems                                              | 4  |

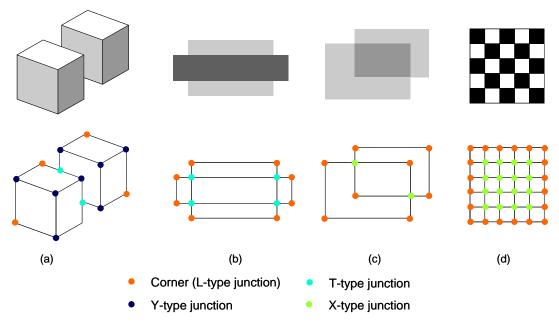

| Figure 2.1  | Schematic explaining how different types of junctions are generated in different      |    |

| config      | gurations of objects                                                                  | 9  |

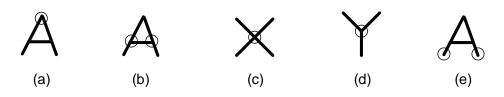

| Figure 2.2  | Features of interest                                                                  | 10 |

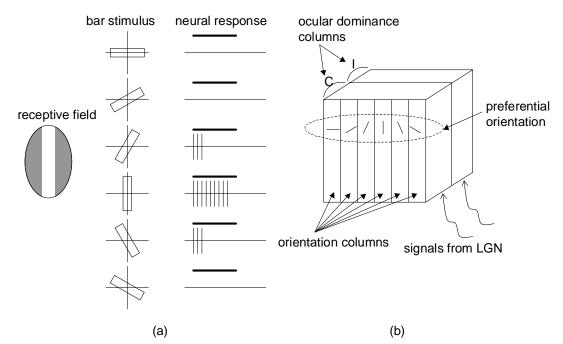

| Figure 2.3  | Orientation selectivity of the cell response.                                         | 12 |

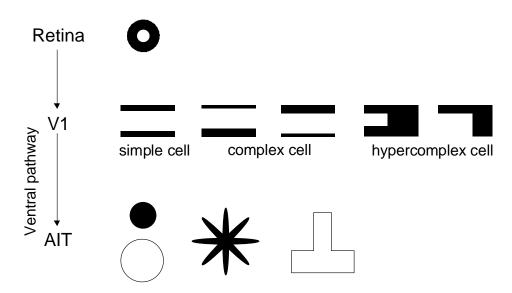

| Figure 2.4  | Shape of stimulus which excites the cell at each stage along the visual pathway       | 14 |

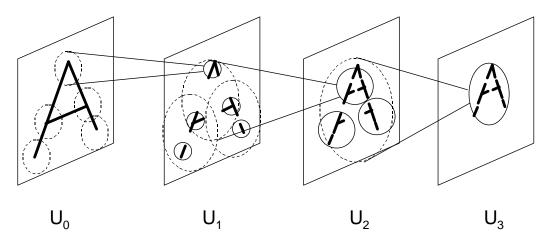

| Figure 2.5  | Neocognitron model of pattern recognition                                             | 16 |

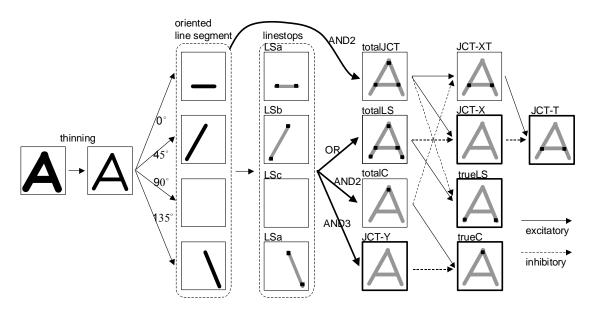

| Figure 2.6  | Algorithm for feature detection at a conceptual level                                 | 21 |

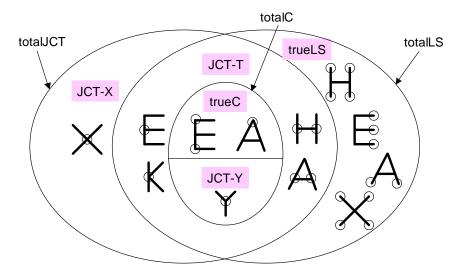

| Figure 2.7  | Venn diagram showing the relationship between the five features detected by the       |    |

| propo       | sed algorithm.                                                                        | 23 |

| Figure 2.8  | Example of template matching.                                                         | 26 |

| Figure 2.9  | Orientation detection using template matching.                                        | 27 |

| Figure 2.10 | ) Linestop detection based on template matching.                                      | 28 |

| Figure 2.11 | Schematic explaining the difficulty of corner detection using a $3 \times 3$ template | 30 |

| Figure 2.12 | 2 Example of dilation and erosion.                                                    | 33 |

| Figure 2.13 | 3 Implementation of a convolution kernel.                                             | 38 |

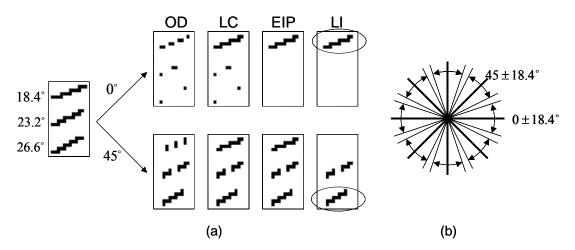

| Figure 2.14 | • Overall processing flow of the feature detection algorithm                          | 39 |

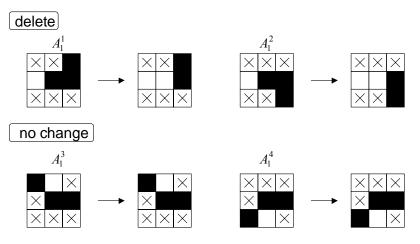

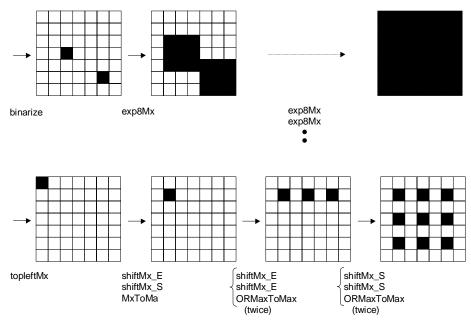

| Figure 2.15 | 5 Algorithm for thinning                                                              | 40 |

| Figure 2.16 | 5 Example of thinning (one cycle)                                                     | 41 |

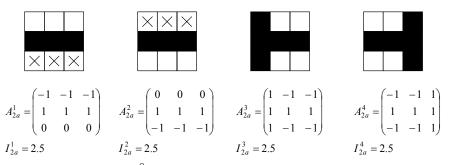

| Figure 2.17 | Patterns categorized as $0^{\circ}$ with its corresponding template and threshold     | 42 |

| Figure 2.18 | B Patterns categorized as $45^{\circ}$ with its corresponding template and threshold  | 43 |

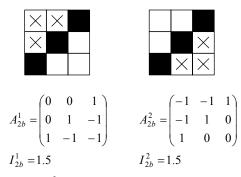

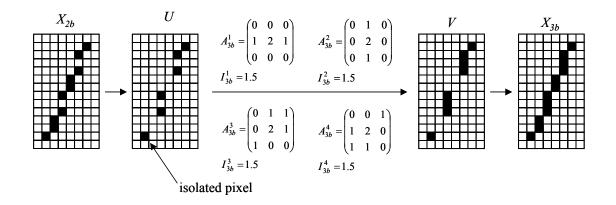

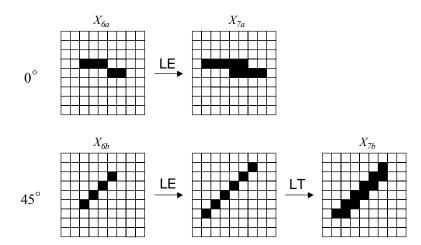

| Figure 2.19     | Procedure of <i>line completion</i> operation in $0^{\circ}$ orientation.                         | 45  |

|-----------------|---------------------------------------------------------------------------------------------------|-----|

| Figure 2.20     | Procedure of <i>line completion</i> operation in $45^{\circ}$ orientation                         | 47  |

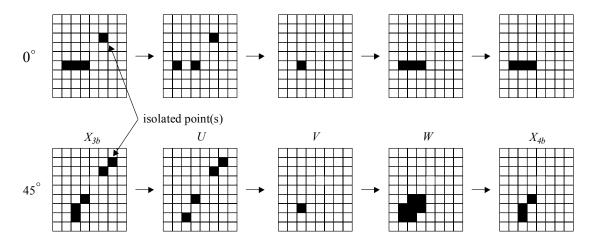

| Figure 2.21     | Procedure of <i>elimination of isolated points</i> operation in $0^{\circ}$ orientation (top) and | lin |

| $45^{\circ}$ or | ientation (bottom).                                                                               | 49  |

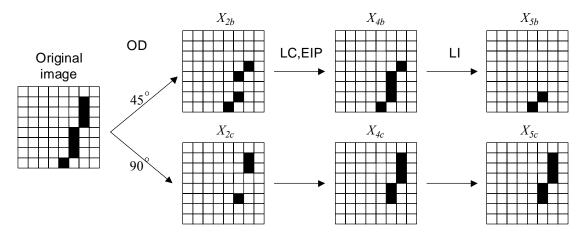

| Figure 2.22     | Procedure of <i>line inhibition</i> operation.                                                    | 50  |

| Figure 2.23     | Schematic explaining the orientation tolerance of the proposed algorithm                          | 51  |

| Figure 2.24     | Line elongation operation and line thickening operation explained for $0^{\circ}$ and 43          | 5°  |

| orienta         | tions                                                                                             | 54  |

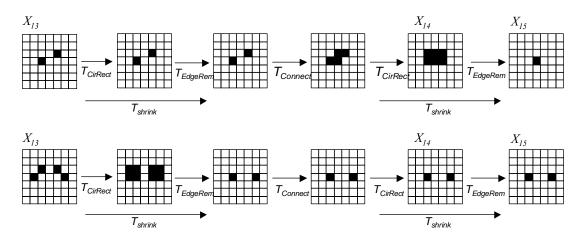

| Figure 2.25     | Procedure of shrinking                                                                            | 57  |

| Figure 2.26     | Merging of linestops which originally belong to different orientation planes                      | 60  |

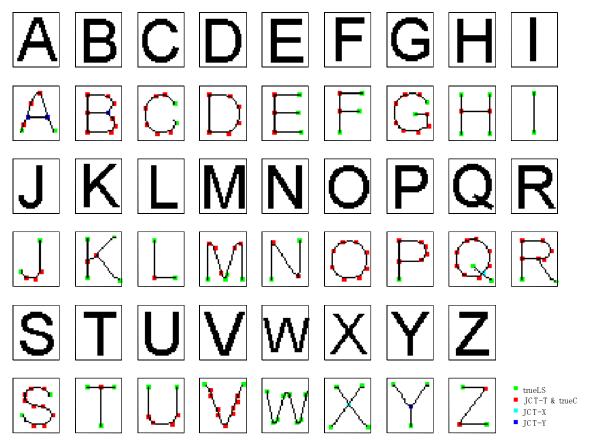

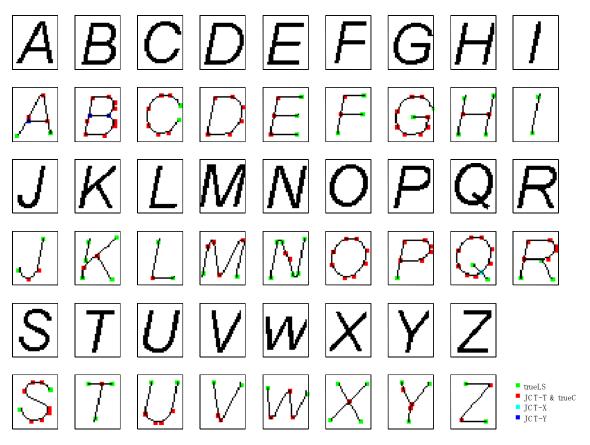

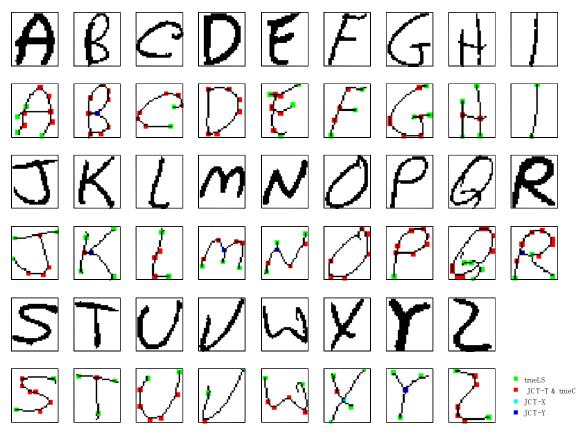

| Figure 2.27     | Features detected by the proposed algorithm for alphabetical characters                           | 63  |

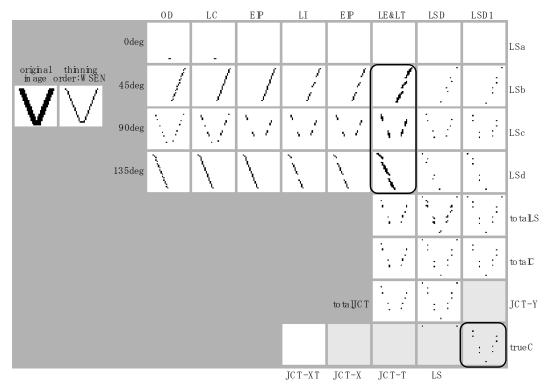

| Figure 2.28     | Simulation result for letter "V"                                                                  | 64  |

| Figure 2.29     | Simulation result for letter "W"                                                                  | 65  |

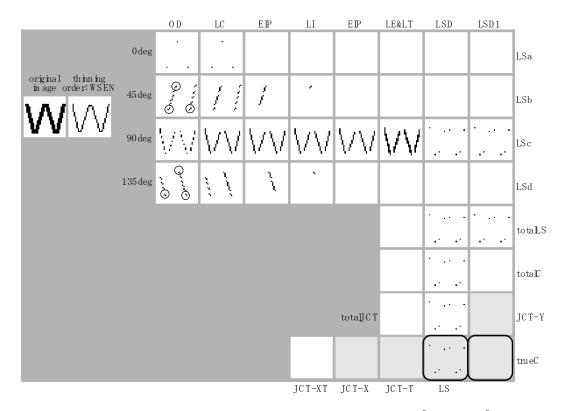

| Figure 2.30     | Features detected by the proposed algorithm for <i>italic</i> alphabetical characters             | 67  |

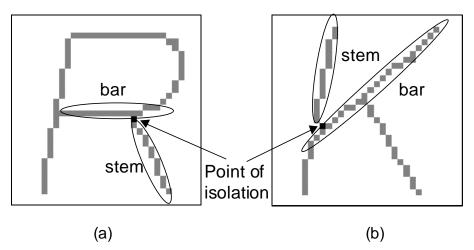

| Figure 2.31     | Pixel point where the stem is separated from the bar of the T-type junction for tw                | wo  |

| letters         | "R" and "K"                                                                                       | 68  |

| Figure 2.32     | Simulation results for slanted letter "X"                                                         | 69  |

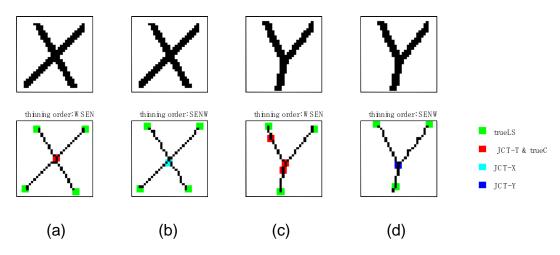

| Figure 2.33     | Effect of thinning order on the feature detection.                                                | 70  |

| Figure 2.34     | Features detected by the proposed algorithm for handwritten characters                            | 71  |

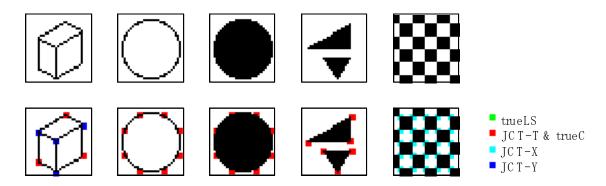

| Figure 2.35     | Features detected for various patterns                                                            | 72  |

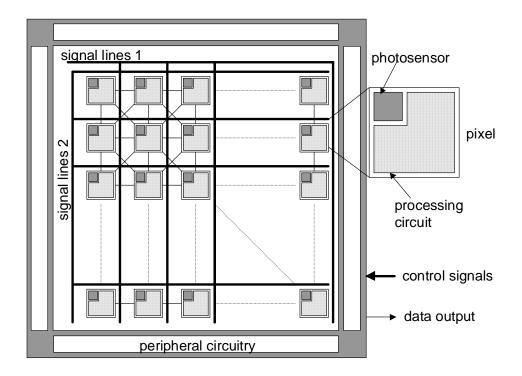

| Figure 3.1      | General architecture of vision sensors.                                                           | 79  |

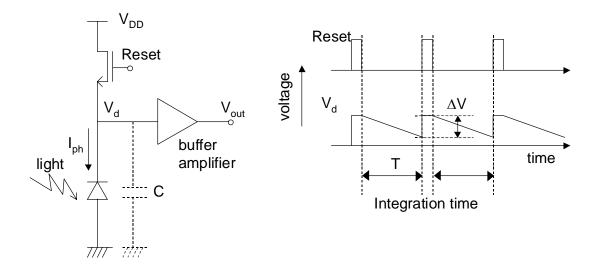

| Figure 3.2      | Schematic explaining the process of phototransduction.                                            | 81  |

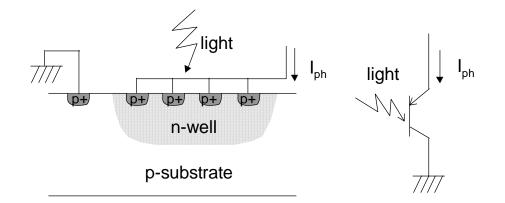

| Figure 3.3      | Structure of the phototransistor                                                                  | 83  |

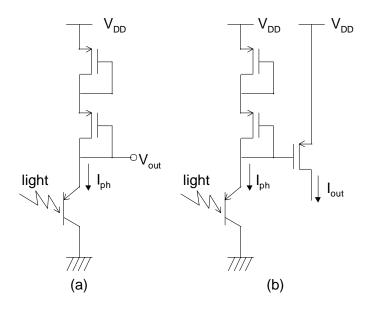

| Figure 3.4 1    | Logarithmic compression circuit.                                                                  | 84  |

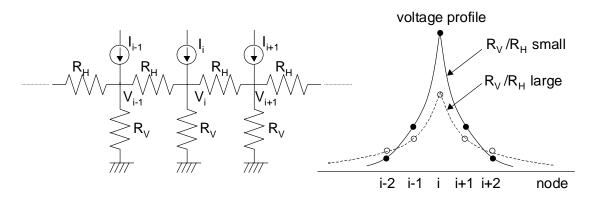

| Figure 3.5 Resistive grid (left) and its impulse response (right)                                  |

|----------------------------------------------------------------------------------------------------|

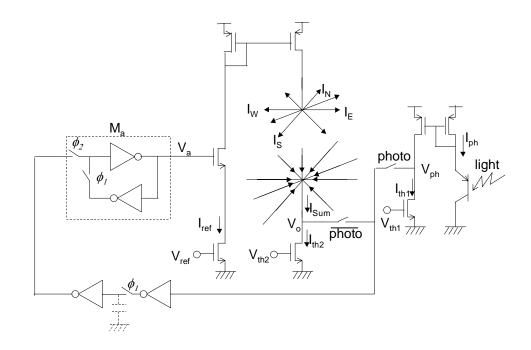

| Figure 3.6 Conceptual architecture of the pixel circuit                                            |

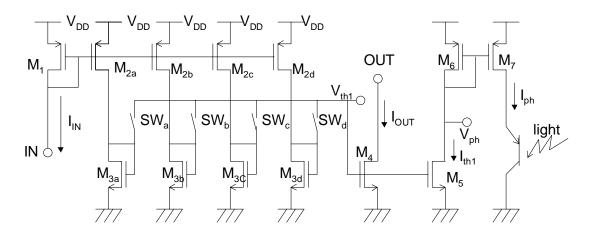

| Figure 3.7 Schematic of image digitization circuit with an adjustable threshold current 101        |

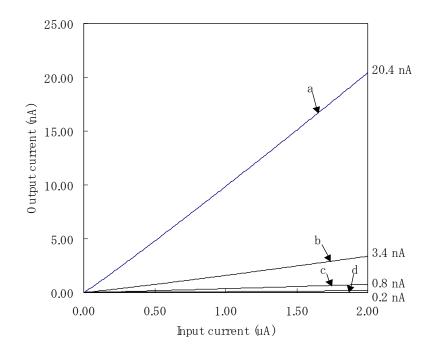

| Figure 3.8 Relationship between the input current and the output current for different switch      |

| settings for the circuit shown in Figure 3.7                                                       |

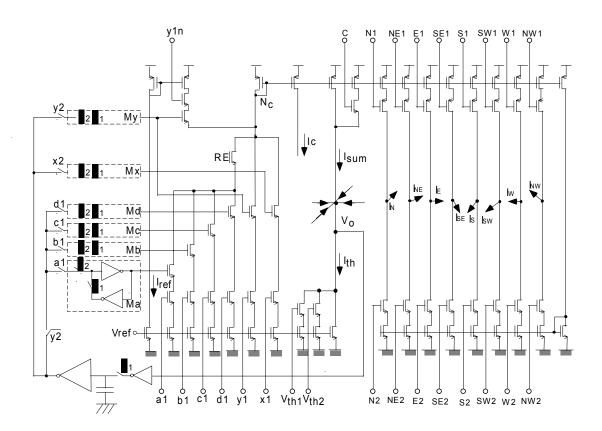

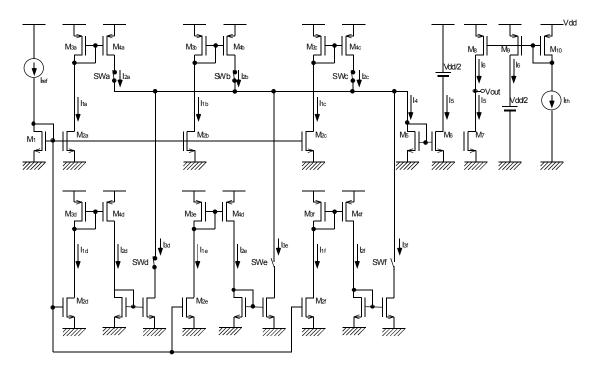

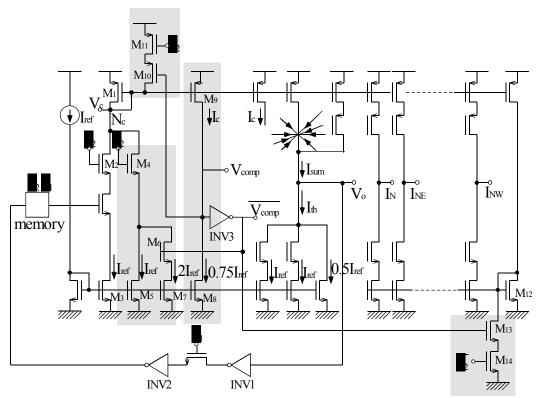

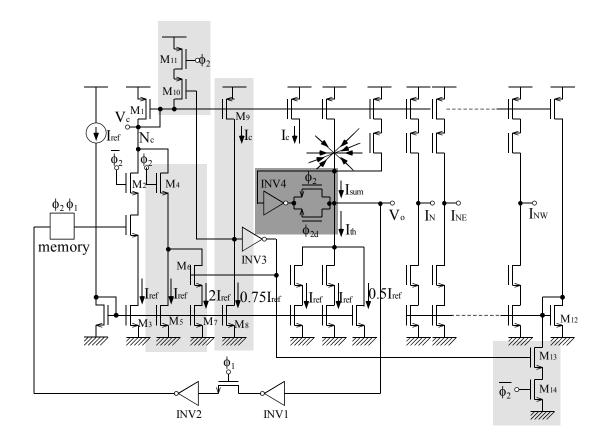

| Figure 3.9 Schematic of the processing circuit                                                     |

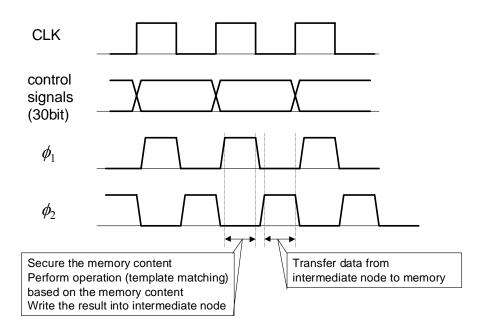

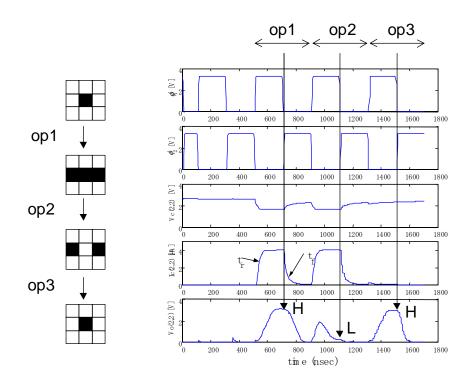

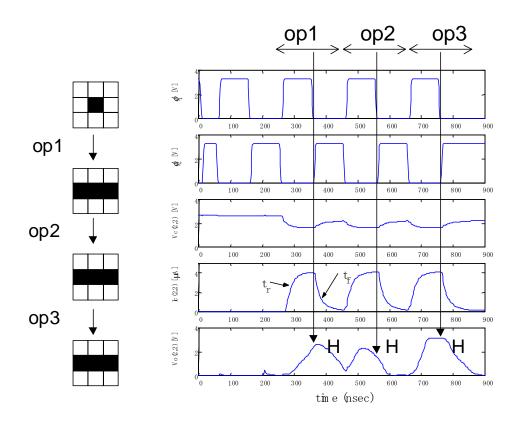

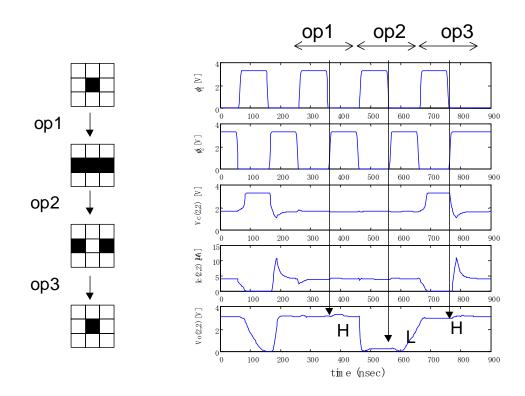

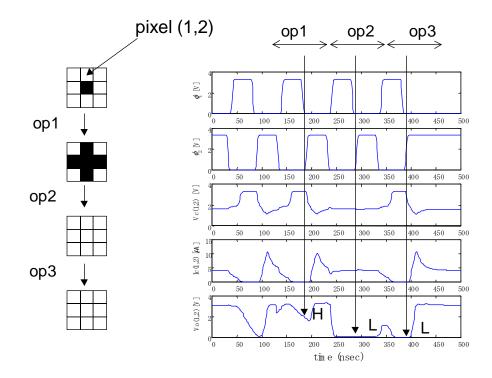

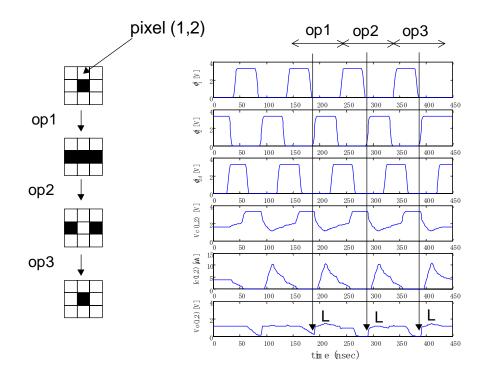

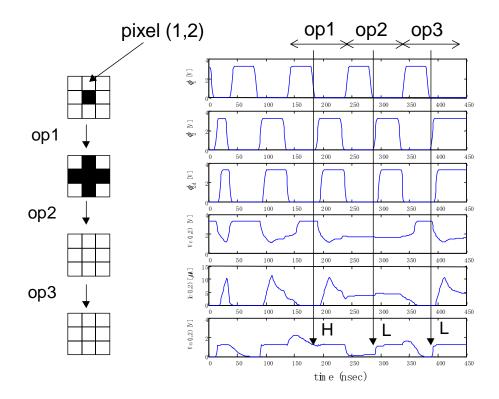

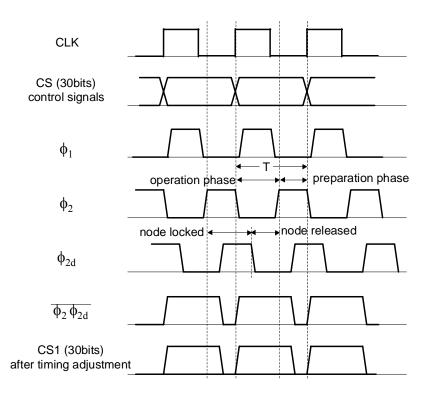

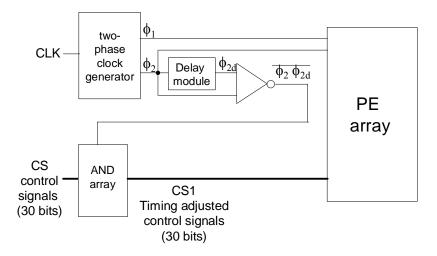

| Figure 3.10 Timing diagram for chip operation                                                      |

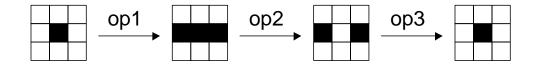

| Figure 3.11 Example of an operational sequence                                                     |

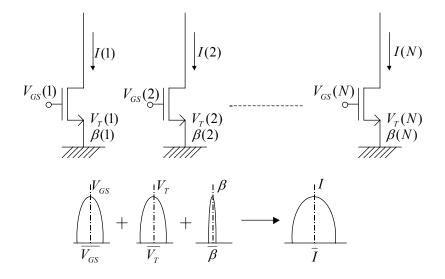

| Figure 4.1 Current output from a set of transistors that has the common gate voltage               |

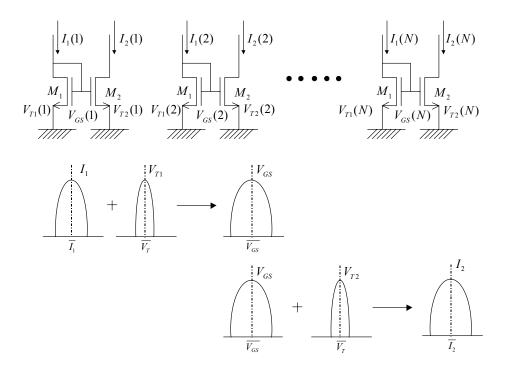

| Figure 4.2 Variation of the output currents from a set of transistors with different gate voltages |

| and process parameters                                                                             |

| Figure 4.3 Schematic showing the increase of the current variation by current mirror operation.    |

|                                                                                                    |

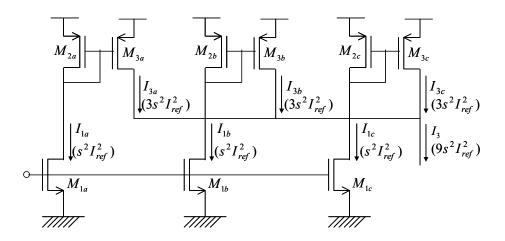

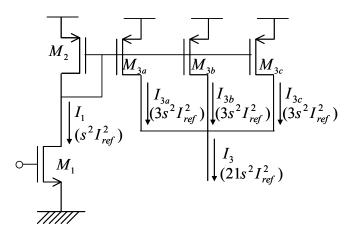

| Figure 4.4 Current summation circuit                                                               |

| Figure 4.5 The other type of current summation circuit                                             |

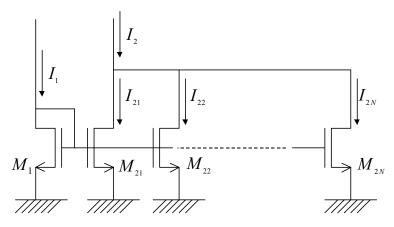

| Figure 4.6 Generalized current summation circuit                                                   |

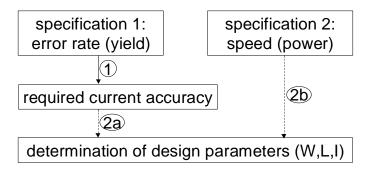

| Figure 4.7 Schematic explaining the design flow of the systematic circuit design                   |

| Figure 4.8 Current thresholding circuit as an example to demonstrate the design procedure.         |

|                                                                                                    |

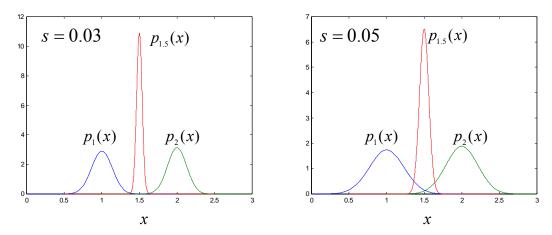

| Figure 4.9 Probability distributin function of the output current and the threshold current for    |

| different relative current variations (left: <i>s</i> =0.03; right: <i>s</i> =0.05)                |

| Figure 4.10 Hspice Monte-Carlo simulation result                                                   |

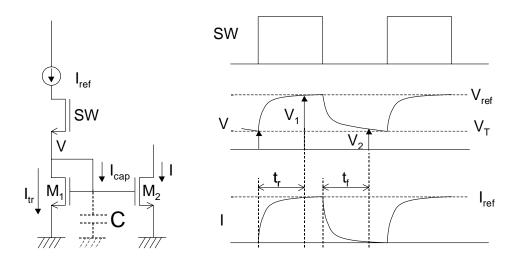

| Figure 4.11 Schematic to explain the charging and discharging of the capacitance associated        |

| with the gate                                                                                      |

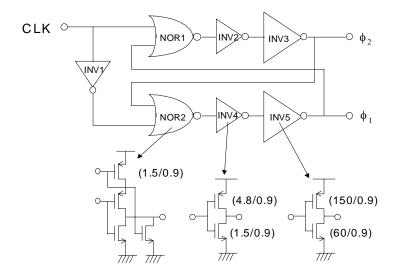

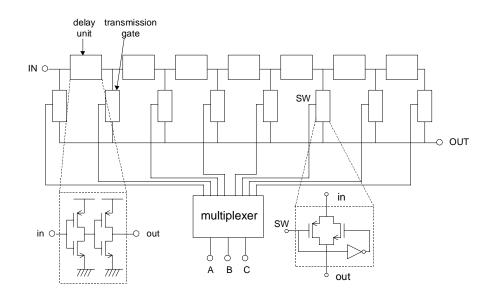

| Figure 5.12 Schematic of the two-phase clock generator                                                   | 172  |

|----------------------------------------------------------------------------------------------------------|------|

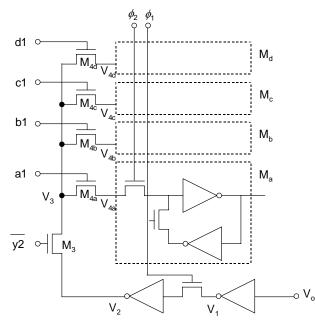

| Figure 5.13 Circuit diagram of the programmable delay generator.                                         | 173  |

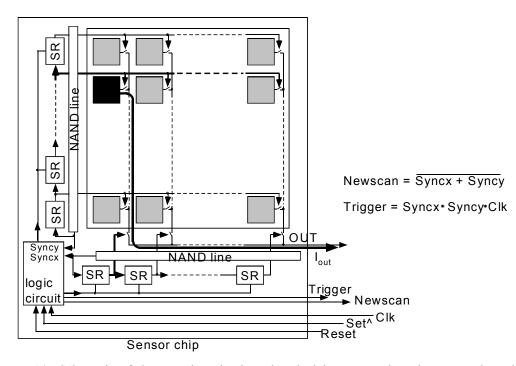

| Figure 5.14 Schematic of the scanning circuit.                                                           | 174  |

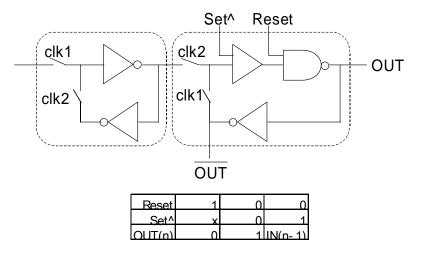

| Figure 5.15 Schematic of the shift register. clk1 and clk2 are non-overlapping two phase                 |      |

| clocks                                                                                                   | 175  |

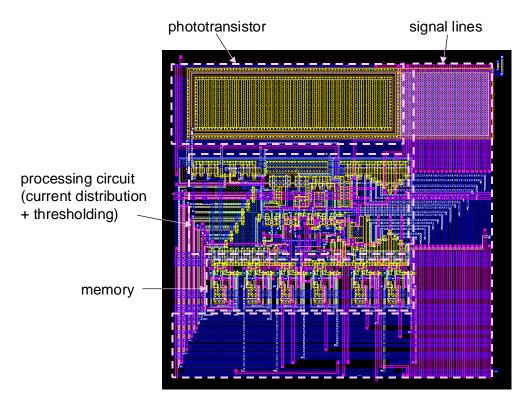

| Figure 5.16 Layout of the pixel.                                                                         | 177  |

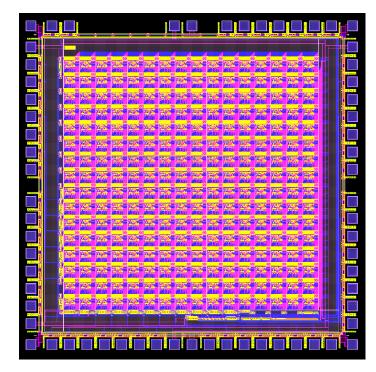

| Figure 5.17 Layout of the entire chip.                                                                   | 178  |

| Figure 5.18 Schematic of the connection between the test board which contains the test chi               | ip   |

| and the PC equipped with a digital I/O board and an A/D converter.                                       | 179  |

| Figure 5.19 Measurement result of the delay of $\phi_{2d}$ with respect to $\phi_2$ for two power supply | 1    |

| voltages ( $V_{DD} = 4 \text{ V}$ and $V_{DD} = 3.3 \text{ V}$ ).                                        | 180  |

| Figure 5.20 Schematic showing the signal transfer from the thresholding node to the memo                 | ory. |

|                                                                                                          | 182  |

| Figure 5.21 Method of generating a grid pattern                                                          | 184  |

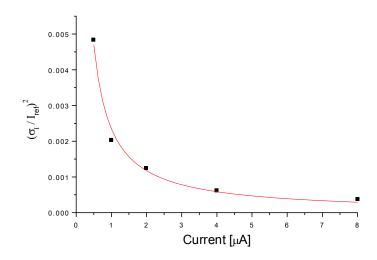

| Figure 5.22 Relative variation of the current as a function of the reference current                     | 186  |

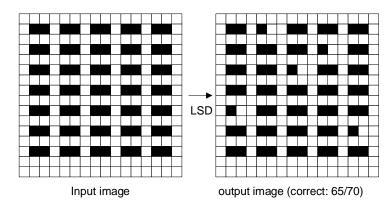

| Figure 5.23 Schematic explaining the detection error for the linestop detection (LSD)                    |      |

| operation                                                                                                | 187  |

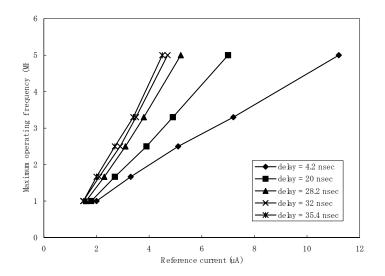

| Figure 5.24 Maximum operating frequency as a function of the reference current for differ                | ent  |

| settings of internal delay between $\phi_2$ and $\phi_{2d}$                                              | 190  |

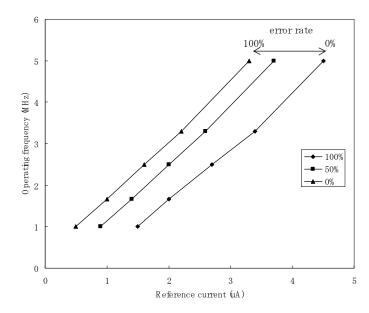

| Figure 5.25 Variation of the operating frequency for different error rates                               | 191  |

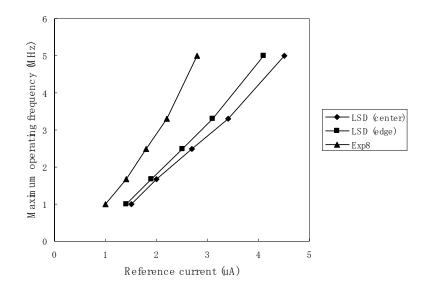

| Figure 5.26 Maximum operating frequency for three types of operations                                    | 192  |

| Figure 5.27 Sensor responses to various letter images                                                    | 194  |

| Figure 5.28 Detail of the processing flow for the letter "R"                                             | 196  |

## **Chapter 1** Introduction

### **1.1 Research background and motivation**

Vision provides us invaluable information in every part of our life. The information obtained from an eye is much more direct and appealing than the information obtained from other sensory organs. This appealing nature is a natural consequence of the tremendous amount of information obtained as a result of the number of photoreceptors in the retina. There are two types of photoreceptors, the rods and the cones. The number of rods is 100 million while the number of cones is 5 million. It is surprising that such a huge amount of information is processed almost instantaneously to understand the scene surroundings us. It is the researcher's dream to build a machine that captures and instantaneously recognizes the image in order to solve real-world problems.

The goal of building such a machine has been approached from two separate sides: development of a high quality image sensor and investigation of an algorithm for pattern recognition. This is just the result of the extreme simplification of treating the retina as an input device and treating the brain as a processing device. The image sensor, which consists of an array of photoreceptors, performs phototransduction at each pixel to capture an image. The number of pixels is increasing year by year, reaching several millions these days, which is almost comparable to the number of cones. The obtained visual information is then passed onto a processing system, where various vision algorithms can be performed for pattern recognition.

The above conventional approach for pattern recognition, which consists of image capture and analysis, has two time consuming steps: the time required for image transfer and the time required for analysis. The former is determined by the video rate (1/33 msec); the latter is determined by the amount of data and the algorithm employed. These two time-consuming

steps make it difficult for the conventional approach to be used for real-time pattern recognition such as high-speed product inspection on an assembly line and autonomous navigation. The problem is the inherent separation between image capture and analysis. It is instructive to look at the visual information processing system in biology, where the captured information is processed in an efficient way to recognize the image. A better understanding of the visual system should be investigated to extract the essence of processing so that it can be mapped onto hardware in some form.

The essence of the biological vision system is hierarchical integration of features. Along the visual pathway from the retina to the cortical area, cells in each layer in the hierarchy function as a detector for a certain image feature. One of the examples is the simple cell and the complex cell present in the visual cortex. These cells have orientation selectivity and respond to lines and edges aligned in a particular orientation. There are other cells known to respond to linestops, corners, and junctions. Features detected in a lower level are integrated in the nexthigher level to represent a more complicated feature. An object is represented as a set of these features in the final recognition layer. This model of pattern recognition based on hierarchical feature integration has the following advantages: (1) significant amount of data reduction is possible, (2) processing is fast due to massive parallelism, (3) recognition is robust to image deformation.

The above observations lead to new type of image sensors which incorporate some processing element at each pixel. They can be roughly divided into two categories, analog and digital, from the point of the type of implementation. The analog implementation is usually dedicated for a particular purpose while the digital implementation is more general purpose oriented. What is common for both implementations is the exploitation of parallelism, which is realized by placing a processing element in each pixel. The on-chip function realized by the additional processing element extracts relevant information for subsequent processing of pattern

Figure 1.1 Various shapes of letter "A". Even though the shape is different, all these letter are categorized as "A".

recognition, resulting in a reduced amount of data.

The features detected by the analog implementation are primarily edges and orientations. These are relatively low level features corresponding to those detected at early stages in the visual pathway. Although the features that can be detected in the digital implementation depend on the architecture and the programming flexibility, no attempt has been made so far to detect higher level features such as corners and junctions. Existing software algorithms for these features are too complicated to be mapped on these digital implementations.

It should be mentioned at this point that while all those implementations incorporate parallel processing capability, the concept of hierarchical processing, which is another important characteristic in the biological vision system, is not taken into account. The realization of the hierarchy in some form may lead to a new type of sensor for the detection of higher level features. This is the motivation of the research presented in the thesis. *The thesis proposes a new type of computational sensor for the detection of the following features: corners, T-type junctions, X-type junctions, Y-type junctions, and linestops.* These are considered very important set of features characterizing an object. For example, think about various shapes of letter "A" shown in Figure 1.1. These four letters are all considered "A" despite its variation in shape. What is common for these letters is the presence of the corner pointing upward at the top, T-type junctions on both sides, and two linestops of the vertical line segments at the bottom.

Figure 1.2 Two types of pattern recognition systems. (a) Newly proposed pattern recognition system using the feature detection sensor as a front-end. (b) Conventional pattern recognition system. Note that the feature extraction carried out in a CPU in (b) is incorporated inside the sensor in (a).

Such a characterization is not possible simply by using lower level features consisting of edges and orientations. Therefore, detection of these features is important for the recognition of an object.

The configuration of the possible pattern recognition system using the proposed sensor is shown in Figure 1.2 (a). The sensor extracts the above-described features of an input image on chip using some form of hierarchical processing. Only extracted features are transferred to the host CPU, where the input image is classified as "A" based on the extracted features. The advantage of this approach is illustrated when compared to the conventional system shown in Figure 1.2 (b), where all the pixel information is transferred to the CPU. The CPU first performs feature extraction for the subsequent recognition task. The difference between (a) and (b) is where preprocessing of feature detection is performed. Feature detection on chip is much faster than the preprocessing on the CPU since the processing is carried out in a hardware level in a parallel fashion. Feature detection reduces the data amount, which results in faster data transfer and facilitates the final recognition task.

Although the above example is specifically for the application of character recognition, it can be extended for various applications. Think about the case of autonomous navigation. An autonomous vehicle always has to detect where the road is in front of the vehicle. For this purpose, the vehicle probably has to detect both sides of the road as well as the centerline, which are important guidelines for navigation. The vehicle usually keeps following the centerline. When the vehicle approaches an intersection, it detects the corner on one of the two sides of the road and makes a turn based on the angle of the corner. For safe navigation, detection of the centerline with its orientation as well as the corner has to be carried out at high speed. The proposed sensor will best suit this type of applications. It also has the potential to have a significant impact on other applications that require high-speed pattern recognition.

#### **1.2** Contribution of the thesis

The thesis examines several aspects concerning the design and implementation of an image sensor for the detection of the image features. The primary contributions of the thesis are: (1) development of an algorithm for the feature detection based on template matching; (2) implementation of the algorithm onto VLSI hardware, (3) investigation of a systematic design procedure based on transistor mismatch. Each of these contributions is briefly summarized below.

(1) An algorithm for the detection of image features for a binary image is proposed. The

detected features are corners, T-type junctions, X-type junctions, Y-type junctions, and linestops. No algorithm has been presented which extracts these features in a discriminative fashion. The proposed algorithm is inspired by the hierarchical integration of features found in biology. The algorithm first decomposes an input image into a set of line segments in four orientations, and then detects the features based on the interaction between these decomposed line segments. With final hardware implementation in mind, the algorithm performs a  $3 \times 3$  template-matching operation in an iterative fashion.

(2) The algorithm is implemented in the form of a CMOS optical sensor. The sensor contains an array of  $16 \times 16$  pixels, each measuring  $150 \ \mu m \times 150 \ \mu m$ , in a chip area of  $3.2 \ mm \times 3.2 \ mm$ . The analog/digital mixed-mode architecture is employed to achieve both compact implementation of  $3 \times 3$  neighborhood interaction in the analog domain and design flexibility in the digital domain. The internal operation within a  $3 \times 3$  neighborhood is carried out by the current distribution and thresholding operation. To speed up the operation of the sensor, a high speed charging/discharging mechanism and another mechanism for node-locking were implemented. The sensor is able to detect the image features on chip in about 50 µsec.

(3) For the determination of the transistor dimension and the reference current, a systematic design procedure for current-mode circuits is proposed. The proposed procedure converts the requirement for accuracy, speed, and the operating region to the specifications for the transistor dimensions and the reference current. The design parameters are chosen to satisfy all these three requirements. This procedure is based on the formulation of the current variation due to transistor mismatch.

The organization of the thesis is as follows. Chapter 2 describes the algorithm for the feature detection. This chapter includes the survey of biological findings, the mathematical formulation of the algorithm, and the evaluation of the algorithm. Chapter 3 presents the

architectural design of the sensor. Based on the past surveys, an analog/digital mixed mode architecture is selected. Chapter 4 presents the systematic design procedure for current-mode processing circuits. Transistor mismatch is analyzed and modeled for the formulation of the design procedure. Chapter 5 shows implementation details and experimental results obtained using the prototype sensor to characterize the sensor performance. Finally, Chapter 6 concludes the thesis.

## **Chapter 2** Algorithm for feature detection

In this chapter, an algorithm for feature detection is described. First, the objective of the algorithm is defined as the discriminative detection of corners and three types of junctions (T-type, X-type, Y-type). Then biological findings concerning the visual pathway are surveyed to confirm the presence of feature detectors and to understand the mechanism of hierarchical integration for pattern recognition. Existing algorithms for feature detection are also reviewed. From these observations, the algorithm for feature detection is proposed at a conceptual level. Then the mathematical framework of template matching in a  $3 \times 3$  neighborhood is presented to formulate the algorithm. The relationship between template matching and other image processing methods is also discussed. Based on the framework of template matching, the detail of the algorithm is described as a sequence of processing flow. The proposed algorithm is applied to printed and handwritten characters, as well as several patterns, to demonstrate its performance. Finally, pros and cons of the algorithm are discussed to conclude this chapter.

### 2.1 Problem definition

It is well known that corners and junctions carry rich information about the structure of an object [1]. This is obvious in the example shown in Figure 1.1, where a set of these geometrical features, together with linestops, characterizes the letter "A". Another example demonstrating the significance of these geometrical features for pattern recognition is shown in Figure 2.1. The three-dimensional view of the two cubes shown in (a) contains corners and junctions of the Y-type and T-type. Corners and Y-type junctions always exist in the image of a solid body viewed from a certain angle. The presence of T-type junctions indicates the occlusion between multiple objects: the rear cube is occluded by the front one. The occlusion is

Figure 2.1 Schematic explaining how different types of junctions are generated in different configurations of objects. For each image, junctions are superimposed on an edge-extracted image shown below the corresponding original image. (a) Three-dimensional view of two cubes. The front one occludes the rear one. (b) Two sheets in which an opaque one is placed on top of the other. (c) Two sheets in which a transparent one is placed on top of the other. (d) Checkerboard pattern.

also found in (b) where the top sheet occludes the bottom one. The image shown in (c) also contains two sheets. However, the top one is transparent and hence X-type junctions are generated. T-type junctions and X-type junctions are important cues for occlusion and transparency, respectively. These junctions are not only found in images including several objects but also found in textures. For example, the checkerboard pattern in (d) produces X-type junctions. These examples demonstrate the usefulness of these features for object understanding and pattern recognition.

The detection of these features is very important from a practical point of view. They are robust with respect to changes in perspective or small distortions. In addition, they are zerodimensional and do not cause an aperture problem. Therefore, they can be used to make correspondence between multiple images obtained from different perspectives (see ref. [2], for

Figure 2.2 Features of interest. (a) Corner. (b) T-type junction. (c) X-type junction. (d) Y-type junction. (e) Linestop.

example). Although corner detection in real-world problems should deal with a gray image, once edges are properly extracted in a preprocessing stage, the problem can be simplified as the detection of these features for an edge extracted image. Then the situation becomes somewhat similar to that shown in Figure 1.1, where the features are detected for characters, which are basically line drawings. For this reason, the thesis focuses on binary images, i.e, black and white images, especially characters, which are considered good examples of line drawings. Characters are also suitable to test the performance of the algorithm since there are many variations and deformations. The features we would like to identify are listed in Figure 2.2. Note that linestops are included in this feature set. It is important to be able to detect these features for line drawings with any line width.

To summarize, the objective of the algorithm is to detect and locate these features (corners, T-type, X-type, and Y-type junctions, linestops) in a discriminative fashion for a binary image. It is also important for the algorithm to be relatively simple so that it can be eventually implemented in hardware.

### 2.2 Feature detection and pattern recognition in biology

Since our primary objective is the detection of corners and junctions, it should be helpful and suggestive to investigate if there are detectors for these features in biological vision system. If that is the case, how is an object recognized based on these features? In the following, several biological findings are described to introduce different levels of feature detectors present in the visual pathway and their possible role in pattern recognition.

The visual information processing starts at the retina where the intensity of an incoming light is converted to an electrical signal. Phototransduction is carried out by two types of photoreceptor cells, the cone and the rod. The cone is responsible for day vision while the rod is responsible for night vision. The number of the cone is 5 million while the number of the rod is 100 million [3]. In addition to these two cells, there are four other types of cells in the retina: the horizontal cell, the bipolar cell, the amacrine cell, and the ganglion cell. These cells belong to one of the two layers, inner plexiform layer and outer plexiform layer, depending on their physical location. The outer plexiform layer consists of the photoreceptors (rods and cones), the horizontal cells, and the bipolar cells, while the inner plexiform layer consists of the amacrine cells and the ganglion cells.

In the outer plexiform layer, the cones and the rods are connected to the horizontal cells as well as to the bipolar cells. The horizontal cells, which are mutually connected in a lateral direction, spread the input signal from the photoreceptors and hence produce a spatially smoothed version of the incoming signal. The bipolar cell receives excitatory inputs from the photoreceptors and inhibitory inputs from the horizontal cells, and thus produces an output that is equal to the difference between the photoreceptor signal and the horizontal cell signal. This results in a concentric ON-center type receptive field<sup>1</sup>. The ON-center receptive field indicates that the light that falls onto the center area of the receptive field excites the bipolar cell while the light that falls onto the periphery inhibits the bipolar cell. Already at this level in the visual information pathway, a preliminary level of feature detection is performed: the bipolar cell responds to edges of an object where intensity changes sharply, while it responds poorly to uniform illumination [4].

<sup>&</sup>lt;sup>1</sup> The receptive field of a neuron is defined as the area on the retina that affects the signaling of the neuron.

Figure 2.3 Orientation selectivity of the cell response. (a) Response of the simple cell to stimuli of different orientations. (b) Hypercolumn structure.

Further signal modification and integration are carried out in the inner plexiform layer to produce an output at the ganglion cell, which serves as the final station of the retinal processing. The activity of the ganglion cell seems to be made up by the total contribution of the other four cell types. The receptive field of the ganglion cell takes an ON-center shape, which is almost similar to that of the bipolar cell. The difference is that the output is represented by the firing frequency at the ganglion cell while the output is represented simply by the level of the potential at the bipolar cell.

From the ganglion cells runs the optic nerve through lateral geniculate nucleus (LGN) to the cortical area V1, where three types of cells, the simple cell, the complex cell, and the hypercomplex cell, exist. The simple cell responds to a bar of light aligned in a certain orientation as shown in Figure 2.3 (a). For a receptive field that is vertically oriented, the bar stimulus in the vertical orientation elicits a largest number of pulse sequences. As the bar is rotated from this preferential orientation, the response decreases quickly. This is quite different from the response of the ganglion cell, which does not have any orientation selectivity. The complex cell, like the simple cell, also responds to stimulus aligned in a certain orientation. However, the demand for precise positioning found in the simple cell is relaxed in the complex cell. As long as a properly oriented stimulus falls within the boundary of the receptive field, the complex cell responds. The third type of cell, the hypercomplex cell, needs more refined shape of stimulus for excitation. They require that the stimulus have discontinuity. The simple line stimulus, even if it is aligned in the preferential orientation, does not excite the cell completely. Consequently the best stimulus results in linestops and corners (they are also called the endstopped cell for this reason). This is one of the feature detectors that is interest to us.

The receptive fields of these cells in area V1 are not arranged in a random order: there is a clear retinotopic mapping present such that adjacent cells have adjacent receptive field positions in the retina. Orientation selectivity also has a nonrandom arrangement: there are vertical columns through the thickness of the cortical sheet containing cells with similar orientation preferences. Each column is about 30-100  $\mu$ m wide and 2 mm deep. The preferential orientation shifts from one column to the next column by about 10°. A set of these columns, which covers the entire orientation, is termed *hypercolumn* by its discoverer Hubel and Wiesel [5] (see Figure 2.3 (b)). Each local area in the retinotopic map has a corresponding hypercolumn. It should be also noted that the cortical cells in area V1 do not respond to uniform illumination. Therefore, in area V1, these cortical cells extract edges or contour of an object and represent it as a set of line segments in different orientations.

The extracted information is further transferred from area V1 to V4, thereafter to the posterior part of inferotemporal cortex (PIT), and finally to the anterior part of inferotemporal cortex (AIT) through the ventral pathway, which is believed to be responsible for object

Figure 2.4 Shape of stimulus which excites the cell at each stage along the visual pathway.

recognition. The complexity of the stimulus necessary for cell excitation increases along this pathway. At the AIT, cells which respond to T-type junctions were reported by Fujita et al. [16]. This is another type of feature detector of interest. Actually the typical pattern for the cell excitation ranges from relatively simple features such as T-type junctions or star-shaped stimulus, to a rather complicated one defined by a combination of several objects such as dark circular area above a slightly larger white circular region.

Like in area V1, columnar organization is also found in this area. Cells belonging to one column, whose size is about 400  $\mu$ m, respond to similar patterns, while cells belonging to different columns respond to totally different pattern [6]. However, there is variation in the cell response even in the same column. The following case was reported. Two cells belonging to the same column respond to a vertical bar protruding from the base structure. The response is different between these two cells for different intersection angles. Cell 1 responded best to right angles and maintained 50-60 % of the maximum activation to other angles, while cell 2 responded only to right angles. As this example indicates, the clustering of cells with overlapping but slightly different selectivity works as a buffer to absorb the small variation of

the input pattern [7]. These observations lead to the following hypothesis: an object is probably represented in the AIT by a set of activated columns, each corresponding to different patterns, with some variations allowed within each column.

As explained above, the complexity of the stimulus for cell excitation increases toward the higher levels in the hierarchy, which is schematically shown in Figure 2.4. The size of the receptive field also increases as the complexity of the stimulus increases. The increase in the complexity is achieved by combining the output form several cells having different selectivity at earlier stages in the visual pathway. For example, the orientation selectivity of the simple cell can be obtained by combining the output of the ganglion cell aligned in a certain orientation. The response of the complex cell can be obtained as the combination of the simple cells having the same orientation selectivity but with different spatial positions. During the process of feature integration, the position of a particular feature necessary to excite the cell in the next layer is allowed to shift to some extent. The positional tolerance at each level in the hierarchy leads to a large variation in the input pattern for cell excitation in the final recognition stage. This is how the cell in the AIT achieves shift invariance. The response of the cell is essentially constant throughout its receptive field, which is much larger than that in the earlier stages in the visual pathway.

The above idea of hierarchical feature integration is clearly explained in Fukushima's paper where he proposed *neocognitron* model for pattern recognition [8]. Figure 2.5 shows the idea of pattern recognition taking letter "A" as an example. Suppose that there are three processing layers. The input image in layer  $U_0$  is first mapped onto layer  $U_1$ . The cell in layer  $U_1$  has a corresponding receptive field in layer  $U_0$  and fires when the stimulus pattern that falls onto its receptive field resembles the reference pattern. The cell shown at the top responds to the presence of a  $^-$ -shaped corner. Another cell specifically responds to slanted T-type junctions while the other cell responds to vertical line segments that stop within its receptive field. These

Figure 2.5 Neocognitron model of pattern recognition (adapted from Fukushima [8] and slightly modified).

features are further integrated in layer  $U_2$ . The cell at the top responds to the stimulus which has a combination of a  $\wedge$ -shaped corner at the top and two slanted T-type junctions with opposite directions at the bottom. Likewise, there exist cells in layer  $U_2$ , which detect a combination of slanted T-shape junction and a linestop of the vertical line. In the final recognition layer  $U_3$ , features are further integrated to generate a cell that is excited by the presence of all three features in the preceding layer  $U_2$ . The resultant requirement to excite the cell in layer  $U_3$  is that there is a  $\wedge$ -shaped corner at the top, two slanted T-type junctions on both sides, and two linestops of a vertical line segments at the bottom, which extracts the essence of letter "A". In other words, the letter "A" is characterized by a set of these features.

Representation of an object by a set of features results in a significant amount of data compression. In addition, by allowing some positional tolerance for a feature at each level in the hierarchy, the final layer is able to recognize deformed letters "A". It should be also noted that the whole processing is carried out in a massively parallel fashion, resulting in an enormous amount of computational power even it is performed by slowly operating neurons.

To summarize this section, the biological vision system is characterized by hierarchical

integration of features. Detectors for corners and junctions do exist in this hierarchy. These features are formed from lower level features such as edges or linestops in different orientations, and they are further integrated to higher level features to finally represent an object as a set of these higher level features. These observations not only confirm the importance of the detection of corners and junctions for pattern recognition, but also give some clue for the implementation of these features.

### **2.3** Survey of the algorithms for corner and junction detection

Having understood the importance of corners and junctions in pattern recognition and the presence of detectors for these features, we are ready to implement these feature detectors borrowing some ideas from biology. Before going into detail, however, several algorithms for detection of these features, some of which are biology based and some of which are not, are briefly discussed below.

Fukushima *implicitly* implemented detectors for corners and junctions in his later work [9], where he applied the neocognitron concept to the character recognition problem in the form of a five-layered neural network. To form the receptive field of different complexities in different layers, appropriate patterns are used to train each layer. The second layer is trained to respond to line segments in eight orientations ( $0^{\circ}$ ,  $22.5^{\circ}$ ,  $45^{\circ}$ , ...,  $157.5^{\circ}$ ). The third layer is trained to respond to different combinations of the line segments detected in the second layer, which represents corners with different angles and junctions of different types (T-type, X-type, Y-type). The trained network was able to correctly classify input patterns even with its position shifted or with its shape deformed. Although this work demonstrates the excellent example of the neural network architecture for pattern recognition, these types of feature detectors do not explicitly detect and locate the position of features and do not fit our interest.

Actually within the framework of the neural network, explicit implementation of feature detectors other than oriented line segments and linestops have not been reported (for example, see refs. [10], [11], [12]). This is because the direct detection of corners and junctions is not as simple as it first looks, which is explained in Section 2.5.

Heitger et al. have proposed an "endstopped operator", which mimics the function of the endstopped cell in the visual system [13]. They first convolved an input image with even and odd symmetrical orientation selective filters and combined the output of these two filters to compute a local energy measure. The output image corresponds to the output of the complex cell, where edges and lines are enhanced in a preferential orientation. Then the differentiation (the first derivative and the second derivative) of this output image is calculated along the preferential orientation. The local maxima of combined endstopped operators for all orientations indicate the position of what they call "key-points". The simulation result showed that the endstopped operator was able to detect linestops, corners, and T-type junctions. The detector would be able to detect Y-type junctions with less specificity. However, it would be difficult to detect X-type junctions because they do not produce a local maximum at these points.

Freeman also applied the similar approach for the detection of corners, T-type junctions and X-type junctions [14]. His method computes the local energy along multiple orientations to find two dominant orientations along which edges are represented. Then the stopped-ness is calculated as the derivative along these two orientations. If stopped-ness is high in two orientations, the junction is detected as the corner. If stopped-ness is low in one of the two orientations, it is classified as the T-type junction. If stopped-ness is not low in both orientations, the junction is classified as the X-type junction. In other words, this method keeps the orientation information and defines the type of junctions based on how the components in two orientations interact with each other. The only restriction for this method is that the number of dominant orientations is limited to two, which would make it difficult to find Y-type junctions.

Dobbins et al. have modeled the output of the hypercomplex (endstopped) cell as the difference of two simple cells with a different size of the receptive field. This operation results in the receptive field that has the excitatory center zone and the inhibitory zone at both ends, which is similar to the result of the second derivative along the preferential orientation. The modeled endstopped cell showed the curvature dependent response [15] [16]. Manjunath et al. have proposed an almost similar approach and applied their method for practical applications such as face recognition, image registration, and motion estimation [2].

Apart from these biology-based approaches, there are two popular methods for corner detection. One is what is known as Plessey detector proposed by Harris and Stephens [17] while the other is known as SUSAN detector proposed by Smith and Brady [18]. The Plessey detector calculates the derivative of image intensities and defines the average squared gradient matrix. The feature is detected as the point where a certain measure computed from the average squared gradient matrix takes a local maximum in the image plane. Although this algorithm can detect corners and three types of junctions (T-type, X-type, Y-type), the detected point does not exactly coincide with the true location of these features. The performance of the SUSAN detector is superior in this sense. The SUSAN algorithm defines a circular area for each point with the center of the circle located on that point and counts the number of pixels within the circle which has the same intensity as the center. Note that no derivative is computed in this algorithm, which gives superior noise immunity [18]. The counted number takes a maximum value in the uniform region and decreases to its half at straight edge points and decreases even more at corners and junctions. Thus, these features are detected by finding local minima of the counted number. One of the possible problems of this method is that it does not seem to work for binary edge images. Also, note that no orientation information is attached to the detected

feature points. Consequently, the determination of the junction type is difficult.

All the methods so far described perform computation locally. For line drawings, there are other methods proposed which need searching neighborhood pixels along the line segment. See refs. [19], [20], and [21], for example. These methods require lots of computation but still cannot detect junctions very well.

### 2.4 Proposed approach

Each algorithm surveyed in the previous section has its advantages and disadvantages. The only method to partly satisfy the demand of discriminative identification of corners and junctions is Freeman's method despite its expected difficulty for the detection of Y-type junctions. The other methods cannot discriminate corners and junctions. Freeman's method is biology based in the sense that orientation decomposition with simultaneous edge extraction is performed as preprocessing.

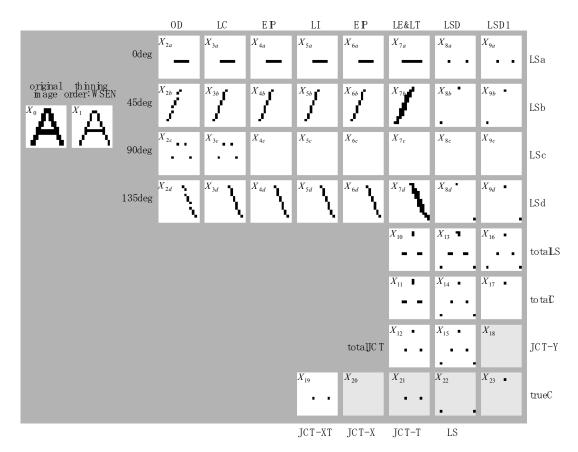

Having a look at Figure 2.2 again, it is obvious that these five features are defined as a result of interaction between line segments and linestops of different orientations. The corner is defined as the point where two line segments of different orientations meet at its linestop. The T-type junction is defined as the point where the linestop of a line segment meets another line segment of different orientation. The X-type junction is defined as the point where at least two line segments of different orientations meet. The Y-type junction is defined as the point where at least two line segments of different orientations meet. The Y-type junction is defined as the point where at least three line segments of different orientations meet at its linestop. This simple definition of these features leads to the conceptual processing flow of the proposed algorithm, which is shown in Figure 2.6. The algorithm finally produces the five features, which are shown in the boxes with a thick boundary line, after several steps of hierarchical processing based on orientation decomposition.

The first processing is the thinning of an input image. Thinning is a process of reducing

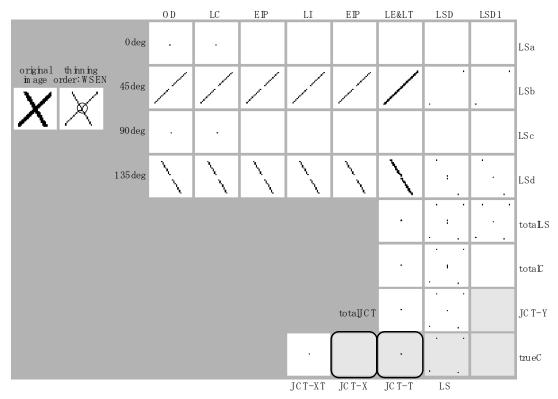

Figure 2.6 Algorithm for feature detection at a conceptual level. The definition of each feature is as follows. totalJCT: the point where at least two line segments in different orientations are present; totalLS: the point where at least one linestop in any orientation is present; totalC: the point where at least two linestops in different orientation planes are present; JCT-Y (Y-type junction): the point where at least three linestops in different orientations are present; JCT-XT: the point which belongs to totalJCT and does not belong to totalC; JCT-X (X-type junction): the point which belongs to totalJCT and does not belong to totalLS; trueLS (linestops): the point which belongs to totalLS and does not belong to totalJCT; trueC (corner): the point which belongs to totalC and does not belong to JCT-Y; JCT-T (T-type junction): the point which belongs to JCT-XT and does not belong to the features shown in the boxes with a thick boundary, trueC, JCT-T, JCT-X, JCT-Y, trueLS, correspond to the features listed in Figure 2.2.

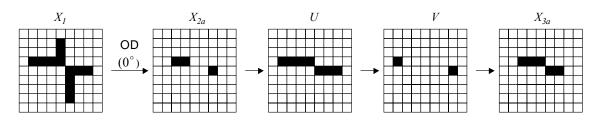

the line width to a single pixel to represent a structural shape of an object. This process can be skipped when dealing directly with a binary edge map, where the line has a single pixel width. However, for dealing with line drawings such as characters, thinning is necessary as preprocessing to normalize the line width to a single pixel so that the subsequent algorithm for feature detection is not influenced by the original line width. Note that the process of thinning is introduced from a purely engineering point of view: there is no evidence that thinning is performed in the biological visual processing. The thinned pattern is decomposed into four orientation planes, i.e.,  $0^{\circ}$ ,  $45^{\circ}$ ,  $90^{\circ}$ , and  $135^{\circ}$  orientation planes, each of which contains line segments of the designated orientation. For example, letter "A" is decomposed into three line segments of different orientations,  $0^{\circ}$ ,  $45^{\circ}$ , and  $135^{\circ}$  orientations. Note that there is orientation tolerance to some degree: each line segment is classified into one of the four orientations that is closest to its orientation. The orientation decomposition can be considered a simplified realization of the processing which takes place at the hypercolumn in the brain, although the resolution of orientation decomposition is  $45^{\circ}$ , which is much lower than that found in the hypercolumn.

The next processing after orientation decomposition is the detection of linestops for each line segment. This processing corresponds to that of the hypercomplex cell (endstopped cell) in biology. Then based on the oriented line segments and linestops, higher level features are computed as described below. totalJCT is defined as the point where at least two line segments in different orientations are present. The operation for this detection is designated as AND2 in the figure: AND2 operation sets the pixel value to 1 where at least two pixels whose value is 1 are present among the four orientations. For letter "A", totalJCT includes two junctions on both sides and the corner at the top. In contrast to totalJCT, which are derived from oriented line segments, the other three features, totalLS, totalC, and JCT-Y, are detected from linestops. totalLS is detected as the point where at least one linestop in any orientation plane is present, which is obtained by OR operation for four linestop images (LSa, LSb, LSc, LSd) as shown in the figure. Likewise, totalC is defined as the point where at least two linestops in different orientations are present, which is obtained by AND2 operation. JCT-Y is defined as the point where at least three linestops in different orientations are present, which is obtained by AND3 operation. JCT-Y is one of those finally detected five features (Y-type junction). Note that totalLS includes totalC as its subset, which further includes JCT-Y as its subset.

Figure 2.7 Venn diagram showing the relationship between the five features detected by the proposed algorithm.

From these features, trueC is detected as the point belonging to totalC but not belonging to JCT-Y. This operation is shown in the figure as receiving the excitatory input from totalC and the inhibitory input from JCT-Y to generate trueC. The X-type junction (JCT-X) is then detected as the point that belongs to totalJCT and does not belong to totalLS. Likewise, true linestops (trueLS) is detected as the point that belongs to totalLS but does not belong to totalJCT. Note that these features are detected as a result of excitatory and inhibitory interactions between several features. These interactions result in the increased level of selectivity for each of these resultant features, which is analogous to the formation of the receptive field of a cell from the receptive field of cells at lower levels. The T-type junction (JCT-T) is detected as a result of the excitatory input from JCT-XT, which is an intermediate result obtained by the excitatory input from totalJCT and the inhibitory input from totalC, and the inhibitory input from JCT-X. Thus the final five features shown in Figure 2.2, trueC, JCT-T, JCT-X, JCT-Y, and trueLS, are produced. The relationship between these features is represented in Figure 2.7 in the form of Venn diagram.

be associated with the excitatory and inhibitory arrows shown in Figure 2.6.

# 2.5 Description of the template matching algorithm

In the previous section, an algorithm for feature detection is described at a conceptual level. To formulate the algorithm, the mathematical framework of template matching is given in this section.

# 2.5.1 Basic framework

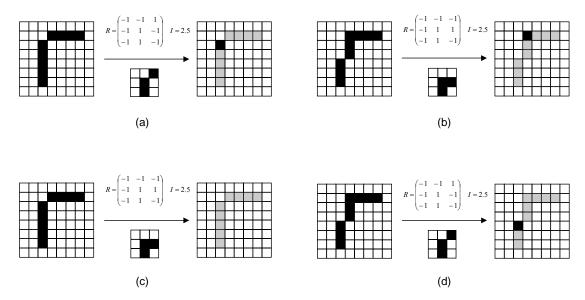

The mathematical framework employed in the thesis to formulate the algorithm is template matching in a  $3 \times 3$  window. For a given input image, the updated image is computed as follows. For every pixel in the input image, the updated status is set to 1 if its  $3 \times 3$  neighbors match the given template with some specified tolerance, and is otherwise set to 0. This procedure is mathematically represented as

$$x_{ij}(n+1) = f(\sum_{l=-1}^{1} \sum_{m=-1}^{1} x_{i+l,j+m}(n) r_{lm}; I)$$

(2.1)

where  $x_{ij}(n)$  is the binary status of the pixel at the position (i,j) at a discrete instant *n*,  $r_{ij}$  is the element of the template, *f* is the function to generate a binary output using the threshold *I* given in the form below:

$$f(x;I) = \begin{cases} 1 & \text{for } x \ge I \\ 0 & \text{for } x < I. \end{cases}$$

(2.2)

The template is represented as

$$R = \begin{pmatrix} r_{-1-1} & r_{-10} & r_{-11} \\ r_{0-1} & r_{00} & r_{0-1} \\ r_{1-1} & r_{10} & r_{11} \end{pmatrix}.$$

(2.3)

Each element of the template takes one of the following three values: -1, 0, or 1. Value of 1 imposes that the pixel value at the corresponding position should be 1; Value of -1 imposes

that the pixel value at the corresponding position should be 0; Value of 0 does not impose any restriction for the corresponding pixel position ("don't care"). For simplicity, let us denote the template matching using the template R and the threshold I as

$$X(n+1) = T_{RI}(X(n))$$

(2.4)

where X(n) represents the whole image plane, i.e., a whole set of  $x_{ij}(n)$ , at instant *n*.

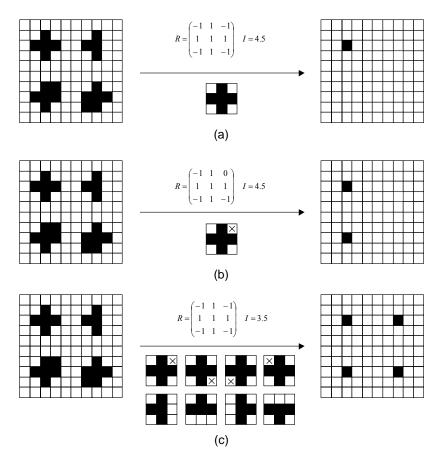

The implication of the above computation is briefly explained below. Template matching is nothing but the calculation of correlation. First, at any position in the image plane, the correlation between its  $3 \times 3$  neighbors and the template is calculated: each element is multiplied by the correspondong coefficient in the template *R* and the result is accumulated. Then the accumulated result is compared to the threshold *I* to digitize the output. Depending on how to construct the template and the threshold value, the strictness of the template matching can be controlled as shown in Figure 2.8.

The first example shown in (a) demonstrates the case of exact matching: the template does not contain 0 and the threshold is 4.5, which is smaller than the number of pixels whose value is 1 by one half. Only the center of the cross on the top left corner in the image plane is kept in the updated image, since the correlation result is 5 and is greater than the threshold only at this point. Any other point in the image plane is not selected. The only possible pattern to satisfy the criteria for selection is the template itself with its -1 element interpreted as 0.

The incorporation of 0 in the template gives "don't care" condition to the pixel value at the corresponding position as shown in Figure 2.8 (b). This is the first level of stringency control in template matching. Since the pixel value at the "don't care" position does not contribute to the correlation computation, the bottom left pattern in the image plane, is selected in the updated image. The second level of stringency control in template matching is realized by the decrease in the threshold value as shown in Figure 2.8 (c), where the threshold is set to

Figure 2.8 Example of template matching. The input image containing four patterns on the left is processed by the template and the threshold shown above the arrow to produce the image on the right. Patterns to be selected are shown below the arrow. A black pixel corresponds to 1 while a white pixel corresponds to 0; " $\times$ " mark indicates "don't care". (a) A pattern that exactly matches the template is selected. (b) The presence of 0 at the top right corner in the template gives tolerance for this position to select the left bottom pattern in the image plane. (c) The decreased threshold value gives even more tolerance to select all the four patterns.

3.5, smaller than 4.5 used above for exact matching. The lowered threshold value increases the number of allowable patterns from one to eight, which are shown below the arrow. Hence, the top right pattern in the image plane in which one of the elements constituting the cross is missing, is selected as well as the other two patterns at the bottom in which an additional pixel of 1 is included, since all these patterns produce the correlation value of 4.

It is worthwhile at this point to investigate if template matching can be really used for the

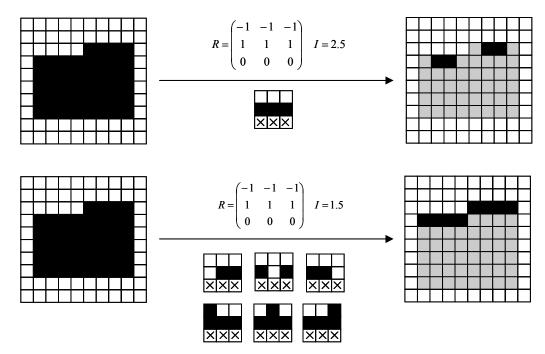

Figure 2.9 Orientation detection using template matching. The rectangular input pattern is used instead of line drawing patterns to demonstrate the selectivity of the template for the top edge and the bottom edge.

three important operations shown in Figure 2.6. These operations include orientation decomposition, linestop detection, and processing based on interaction between several features. Figure 2.9 shows the example of orientation detection. The pattern defined in the template has directional selectivity for horizontal direction. It extracts the top edge of the rectangular input pattern and does not respond to uniform illumination as well as to the bottom edge. The template pattern is similar to the receptive field of the simple cell shown in Figure 2.3 although the pattern in the template corresponds to only half of the receptive field: the template does not extract the bottom  $0^{\circ}$  edge for this reason. The receptive field similar to that of the simple cell is possible to implement by using the following template:

$$R = \begin{pmatrix} -1 & -1 & -1 \\ 2 & 2 & 2 \\ -1 & -1 & -1 \end{pmatrix}$$

(2.5)

Figure 2.10 Linestop detection based on template matching. The combination of the template and the threshold shown above the arrow is equivalent to the combination of the template and the threshold shown below the arrow.

if the value of 2 is allowed for elements in the template. For dealing with the four orientations, it is necessary to allow the value of 2 for all elements in the template, which complicates the template construction in hardware. Therefore, the template corresponding to the top edge and the bottom edge is separately realized. Figure 2.9 also shows the effect of the threshold. All the points along the top edge are not selected with a threshold of 2.5 while all these points are selected with a threshold of 1.5.

The second operation important for the feature detection is the detection of linestops. Figure 2.10 shows the application of template matching for this purpose. By using the template for which the value of 2 is allowed at the center with the threshold value of 0.5 enables the detection of linestops regardless of the orientation of line segments. The template selects pixels that have only one neighbor in either horizontal or vertical direction as linestops. Pixels located in the middle of the line, which has two neighbors, are deleted by the negative contribution from two neighbors. Note that the threshold value of 0.5, which indicates lowered stringency, makes the implementation of feature detection scheme simple: a set of different templates can be represented by only one template.

The third operation important for the detection of higher level features is the realization of excitatory and inhibitory interaction between multiple input images. The three operations shown in Figure 2.6, OR, AND2, and AND3, are defined as the operation to set the pixel value to 1 where at least one, at least two, and at least three line segments are present in different orientation planes, respectively. These operations are naturally represented as the special case of template matching as

$$X(n+1) = T_{E,I}(X_a(n) + X_b(n) + X_c(n) + X_d(n))$$

(2.6)

with

$$E = \begin{pmatrix} 0 & 0 & 0 \\ 0 & 1 & 0 \\ 0 & 0 & 0 \end{pmatrix},$$

(2.7)

$$I = \begin{cases} 0.5 & \text{for OR operation} \\ 1.5 & \text{for AND2 operation} \\ 2.5 & \text{for AND3 operation.} \end{cases}$$

(2.8)

where  $X_a$ ,  $X_b$ ,  $X_c$ , and  $X_d$  designate the 0°, 45°, 90°, and 135° orientation plane, respectively, and *E* is the special template focusing only the present pixel. The plus sign which appears in eqn. (2.6) represents the numerical summation instead of logical OR.

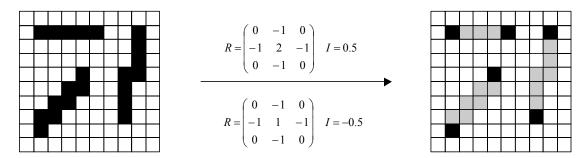

As demonstrated above, the three important operations for the algorithm for feature detection were found possible to implement based on the framework of template matching. Next, let us consider the possibility of direct detection of corners. Figure 2.11 shows the difficulty of corner detection using a  $3 \times 3$  template. No unique mask exists for the inverted L-type corner. In cases (a) and (b), the corner is correctly detected with different templates. However, when the combination of the pattern and the template is changed, no corner is detected in case (c) while a spurious corner is detected in (d). This is due to the small window size of  $3 \times 3$ . The only way to circumvent this problem is the increase of the template size to cover all possible types of corners. However, an interaction area larger than  $3 \times 3$  is not practically feasible from an implementation point of view. These observations again justify the

Figure 2.11 Schematic explaining the difficulty of corner detection using a  $3 \times 3$  template. In (a) and (b), the corner is correctly detected with different templates. When the combination of the pattern and the template is changed as shown in (c) and (d), no corner is detected in (c) and misclassification occurs in (d).

approach of the proposed algorithm where the corner is defined as the intersection of linestops of lines in different orientations.

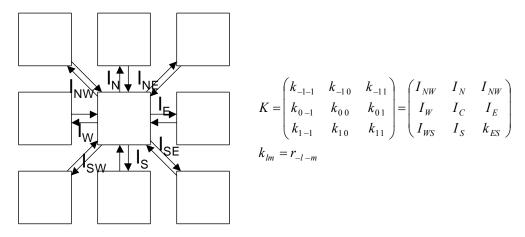

Before going into the detail of the algorithm, it is useful to mention the relationship between the template matching and the convolution operation. Eqn. (2.1) can be rewritten as

$$x_{ij}(n+1) = f(\sum_{l=-1}^{1} \sum_{m=-1}^{1} x_{i-l,j-m}(n) k_{lm})$$

(2.9)

where

$$k_{lm} = r_{-l-m} \,. \tag{2.10}$$

Eqn. (2.9) represents the convolution operation for image X(n) with the kernel K, which is the flipped version of the template R in both horizontal and vertical directions. In this representation, the kernel K is better understood as an operator, or a filtering element, rather than as a template: the original image X(n) is processed with the operator K. The operator

exicites neighborhood pixels where element  $k_{lm}$  is positive while it inhibits neighborhood pixels where element  $k_{lm}$  is negative. It should be noted that the template matching and the convolution is the two sides of the same coin, stating the same thing from different perspectives. However, the different viewpoints are sometimes useful as described in the next subsection.

# 2.5.2 Relationship with other image processing methods

There are several image processing methods that have a close relationship with the template matching scheme. These methods include mathematical morphology and discrete time cellular neural network. A brief survey of these two methods is given below to provide a unified and clear viewpoint for understanding template matching scheme.

Mathematical morphology performs image processing operations based on set theory [22]. Morphological operations nonlinearly transform an image by locally modifying the geometric features in an image using the set relationship between the input image and the so-called "structuring element". Before describing the morphological operation, some basic definitions on the set operations are described below. Let *A* and *B* be sets in  $Z^2$  with components  $a = (a_1, a_2)$  and  $b = (b_1, b_2)$ , respectively<sup>2</sup>.

The translation of A by  $x = (x_1, x_2)$ , denoted  $(A)_x$ , is defined as

$$(A)_x = \{c | c = a + x, \text{ for } a \in A\}.$$

(2.11)

The reflection of *B*, denoted  $\hat{B}$ , is defined as

$$\hat{B} = \{x | x = -b, \text{ for } b \in B\}.$$

(2.12)

The complement of set A, denoted  $A^c$  is

$$A^{c} = \{x | x \notin A\}.$$

(2.13)

The union of two sets A and B, denoted  $A \cup B$  is defined as

<sup>&</sup>lt;sup>2</sup>Each element of a set is a 2-D vector which represents the row and the column position of a black (by convention) pixel in the image.

$$A \cup B = \{x \mid x \in A \quad \text{or} \quad x \in B\}.$$

$$(2.14)$$

The intersection of two sets A and B, denoted  $A \cap B$ , is defined as

$$A \cap B = \{x \mid x \in A \quad \text{and} \quad x \in B\}.$$

(2.15)

Finally, the difference of two sets A and B, denoted A - B, is defined as

$$A - B = \{x | x \in A, x \notin B\} = A \cap B^{c}.$$

(2.16)

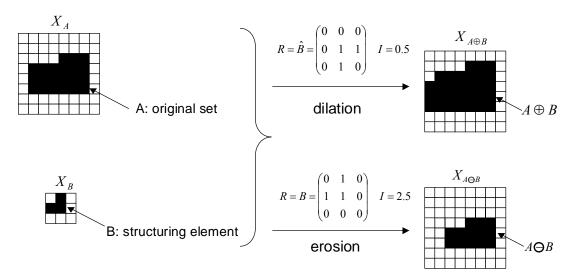

Using the above notation, dilation of set A by the structuring element B, denoted  $A \oplus B$ , is defined as

$$A \oplus B = \{x \mid (\hat{B})_x \cap A \neq \emptyset\}.$$

(2.17)