Reminder:

- $R_0$  equivalent resistance of minimum size (W = L = 1) NMOS transistor

- $I_0$  equivalent  $I_{ds}$  current of minimum size (W = L = 1) NMOS transistor

- $C_0$  gate capacitance of minimum size transistor

- $\tau = R_0 C_0$  or maybe  $C_0/I_0$  technology dependent delay term

R, I, and C in terms of  $R_0$ ,  $I_0$ , and  $C_0$  for a transistor with width W:

| $R_{drive}$ | $\frac{R_0}{W}$ |

|-------------|-----------------|

| $I_{drive}$ | $I_0W$          |

| $C_{gate}$  | $W \cdot C_0$   |

We will evaluate two cases today.

- 1. Extreme velocity saturation where  $R_{p0} = R_{n0}$  (i.e.  $I_{ds}$  at rails is same for equally sized N and P devices—simplifying assumption we made for examples from last class)

- 2.  $R_{p0} = 2R_{n0}$  (i.e.  $I_{ds}$  PMOS at rails is half  $I_{ds}$  of NMOS)

| for the two cases above: <i>C<sub>a</sub></i> is the capacita | $\begin{array}{c} R_{p0} = R_{n0} \\ W_p \mid W_n \mid C_a \end{array}$ |       |        | $R_{p0} = 2R_{n0}$ |       |          |

|---------------------------------------------------------------|-------------------------------------------------------------------------|-------|--------|--------------------|-------|----------|

|                                                               | $W_p$                                                                   | $W_n$ | $C_a$  | $W_p$              | $W_n$ | $C_a$    |

|                                                               |                                                                         |       |        |                    |       |          |

|                                                               | 2                                                                       | 2     | $4C_0$ | 4                  | 2     | $6C_{0}$ |

|                                                               |                                                                         |       |        |                    |       |          |

| A $C$ $T$                                                     |                                                                         |       |        |                    |       |          |

1. How can you size for equal, worst-case rise/fall times assuming targeting  $R_{drive} = \frac{R_0}{2}$  for the two cases above?  $C_a$  is the capacitance of the A input.

2. For a k-input NAND gate, sized for equal, worst-case rise/fall times and targeting  $R_{drive} = \frac{R_0}{2}$ :

$$R_{p0} = R_{n0} \quad R_{p0} = 2R_{n0}$$

What is  $C_{in}$  as a function of  $k$ ?

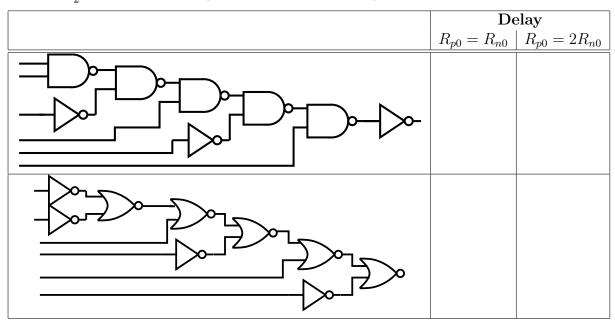

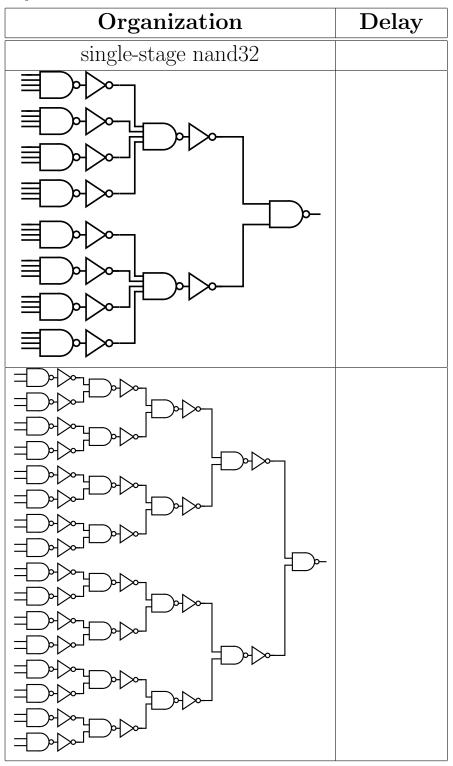

3. Assuming sized for  $\frac{R_0}{2}$  drive as above, and input also driven by  $R_{drive} = \frac{R_0}{2}$ , compare the delay of the following three nand32 implementations for the  $R_{p0} = R_{n0}$  case. Include the delay of driving the input and assume each implementation has an output load of  $4C_0$ .

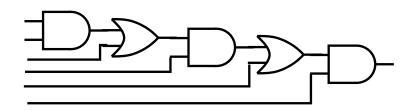

4. What is the delay for each of the two implementations below for this logical computation:

Assume  $R_{drive} = \frac{R_0}{2}$  sizing of gates from previous page, and input also driven by  $R_{drive} = \frac{R_0}{2}$ . Assume each implementation has an output load of  $2C_0$ .