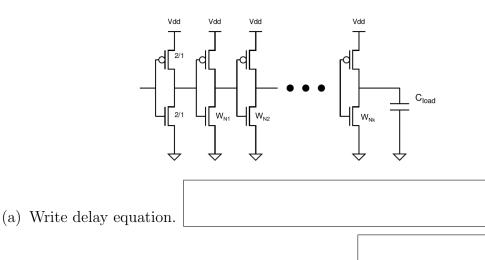

**Today's Question:** How do we drive a large load  $(e.g. C_{load} = 4 \times 10^4 C_0)$  with minimum delay? Detail buffer count and sizing.

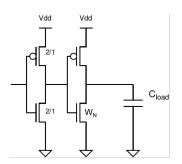

Assume:

- velocity saturated sizing for gate drive; inverter sizing is:  $W_n$ =2,  $W_p$ =2

- Start with  $C_{diff} = 0$  case (for simplicity)

- 1. If we had one inverter stage to size, how should it be sized?

- (a) Write delay equation from  $R_0/2$  drive through driving  $C_{load}$ .

- (b) Symbolic expression for delay-minimizing  $W_N$ .

- (c) Concrete size,  $W_N$ , for  $C_{load} = 4 \times 10^4 C_0$ .

- 2. If we had k inverter stages to size, how should the each be sized?

- (b) Symbolic expression for delay-minimizing  $W_{Ni}$ .

- (c) Symbolic expression for total delay using solution above.

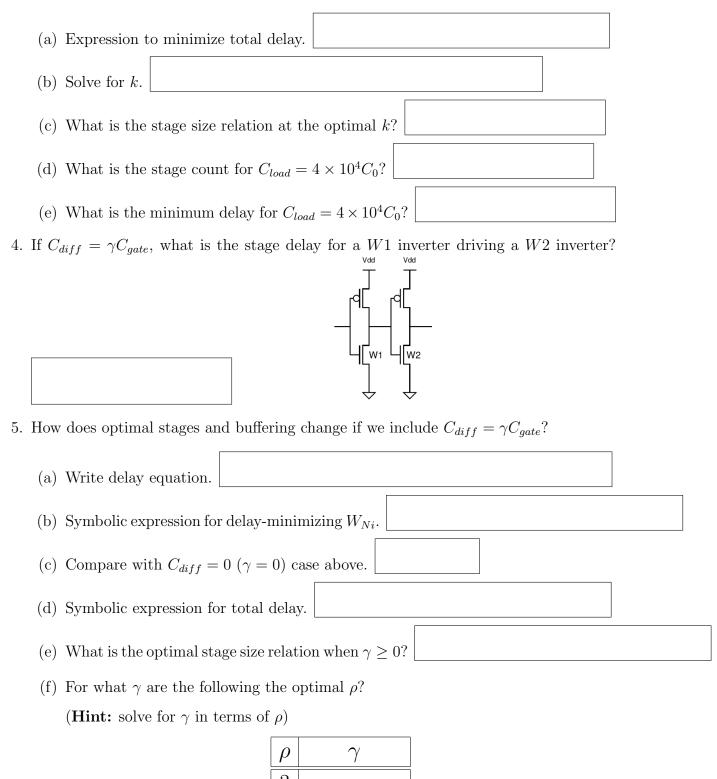

3. What number of stages, N, minimizes total delay?

| $\rho$ | $\gamma$ |

|--------|----------|

| 3      |          |

| 4      |          |