# ESE370: Circuit-Level Modeling, Design, and Optimization for Digital Systems

Lec 3: September 10, 2021

Transistor Introduction (first order)

# Today

- Basic Digital Gates

- Boolean Logic

- Basic Algebra

- DeMorgan's Law

- Minimum Sum of Products/K-maps

- Cascading Gates

- Transistor first order model

- For performance estimates (i.e propagation delay!)

- There are always Rs and Cs!

### Basic Digital Gates

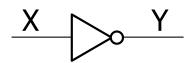

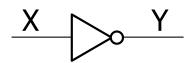

$$\begin{array}{c} NOT \\ Y = \overline{X} \end{array}$$

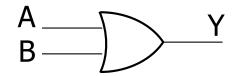

$$OR$$

$Y = A+B$

| Α | В | Y |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

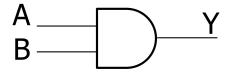

### Basic Digital Gates

$$\begin{array}{l}

\mathsf{NOT} \\

\mathsf{Y} = \overline{\mathsf{X}}

\end{array}$$

$$OR$$

$Y = A+B$

| X | Y |

|---|---|

| 0 | 1 |

| 1 | 0 |

| A | В | Y | Z |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 |

A B

$Z = \overline{A \cdot B}$

**NOR**

$Z = \overline{A+B}$

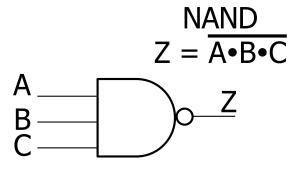

# Basic Digital Gates

| A | В | С | Z |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

### Boolean Algebra

### **☐ TABLE 2-3**

### **Basic Identities of Boolean Algebra**

1.

$$X + 0 = X$$

$$X + 1 = 1$$

$$5. \quad X + X = X$$

7.

$$X + \overline{X} = 1$$

9.

$$\overline{\overline{X}} = X$$

$$10. \quad X + Y = Y + X$$

12.

$$X + (Y + Z) = (X + Y) + Z$$

$$14. \quad X(Y+Z) = XY + XZ$$

16.

$$\overline{X} + \overline{Y} = \overline{X} \cdot \overline{Y}$$

$$2. X \cdot 1 = X$$

$$4. \quad X \cdot 0 = 0$$

$$6. X \cdot X = X$$

$$8. X \cdot \overline{X} = 0$$

11.

$$XY = YX$$

13.

$$X(YZ) = (XY)Z$$

15.

$$X + YZ = (X + Y)(X + Z)$$

17.

$$\overline{X} \cdot \overline{Y} = \overline{X} + \overline{Y}$$

### Combination

- Sum-of-products form (SOP)

- Eg. ABC+DEF+GHI

- Product-of-sums form (POS)

- Eg. (A+B+C)(D+E+F)(G+H+I)

- Convert between the two with Boolean algebra

- DeMorgan's Law

$$A + B = A \cdot B$$

$$= = A \cdot B$$

$$A \cdot B = A + B$$

### Combination

### Canonical Form

□ Every minterm in your expression has every variable

| Row Number | Α | В | C | f |

|------------|---|---|---|---|

| 0          | 0 | 0 | 0 | 0 |

| 1          | 0 | 0 | 1 | 0 |

| 2          | 0 | 1 | 0 | 0 |

| 3          | 0 | 1 | 1 | 1 |

| 4          | 1 | 0 | 0 | 0 |

| 5          | 1 | 0 | 1 | 0 |

| 6          | 1 | 1 | 0 | 1 |

| 7          | 1 | 1 | 1 | 1 |

### Canonical Form

□ Every minterm in your expression has every variable

| Row Number                                         | Α | В | C | f        |

|----------------------------------------------------|---|---|---|----------|

| 0                                                  | 0 | 0 | 0 | 0        |

| 1                                                  | 0 | 0 | 1 | 0        |

| 2                                                  | 0 | 1 | 0 | 0        |

| 3                                                  | 0 | 1 | 1 | 1,       |

| 4                                                  | 1 | 0 | 0 | 0        |

| 5                                                  | 1 | 0 | 1 | 0        |

| 6                                                  | 1 | 1 | 0 | /1       |

| 7                                                  | 1 | 1 | 1 | 1        |

|                                                    | - |   |   | <b>/</b> |

| $f(A,B,C) = ABC + AB\overline{C} + \overline{ABC}$ |   |   |   |          |

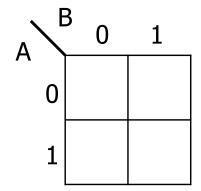

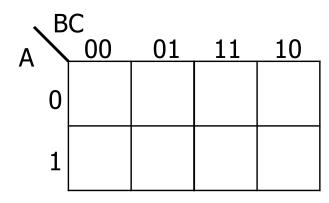

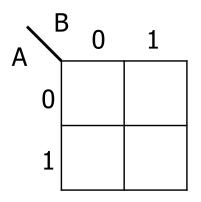

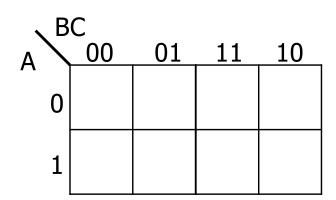

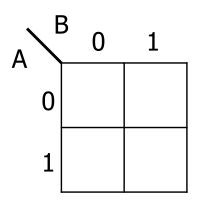

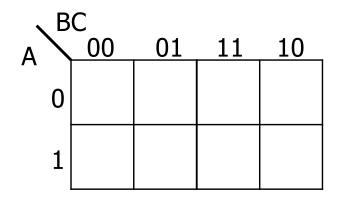

### What is a K(arnaugh)-map?

- □ A grid of squares (representing truth table)

- Each square represents one minterm

- □ The minterms are ordered according to Gray code

- Only one variable changes between adjacent squares

- Squares on edges are considered adjacent to squares on opposite edges

- I.e Table wraps around

- □ K-maps are clumsy with more than 4 variables

## K-map Examples (Preclass 1)

□ 2-variable

Eg:

$$Z = A'B' + AB' + A'B$$

□ 3-variable

### K-map Examples (Preclass 2)

□ 2-variable

Eg:

$$Z = A'B' + AB' + A'B$$

□ 3-variable

Eg:

$$Z = A'B'C' + A'B + ABC' + AC$$

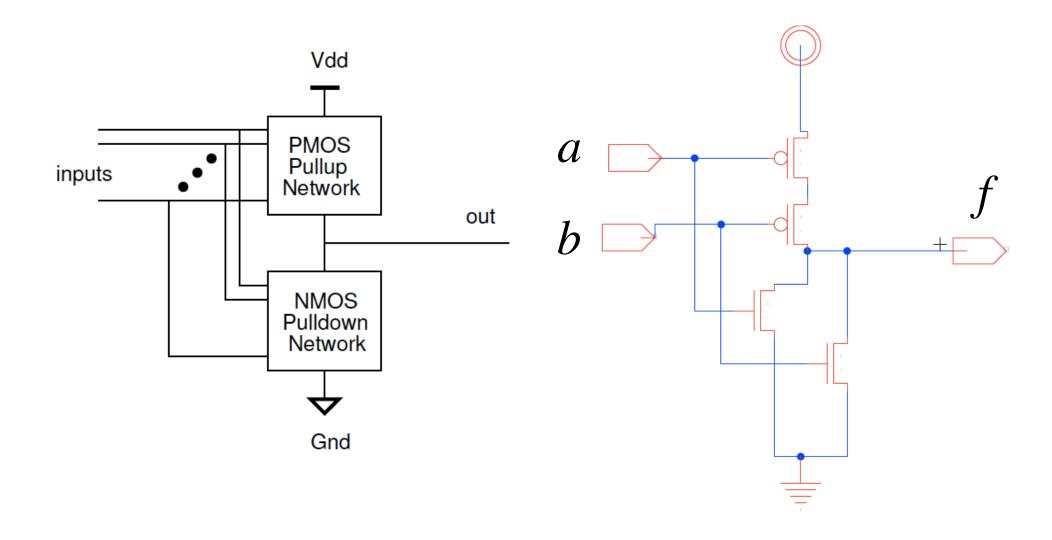

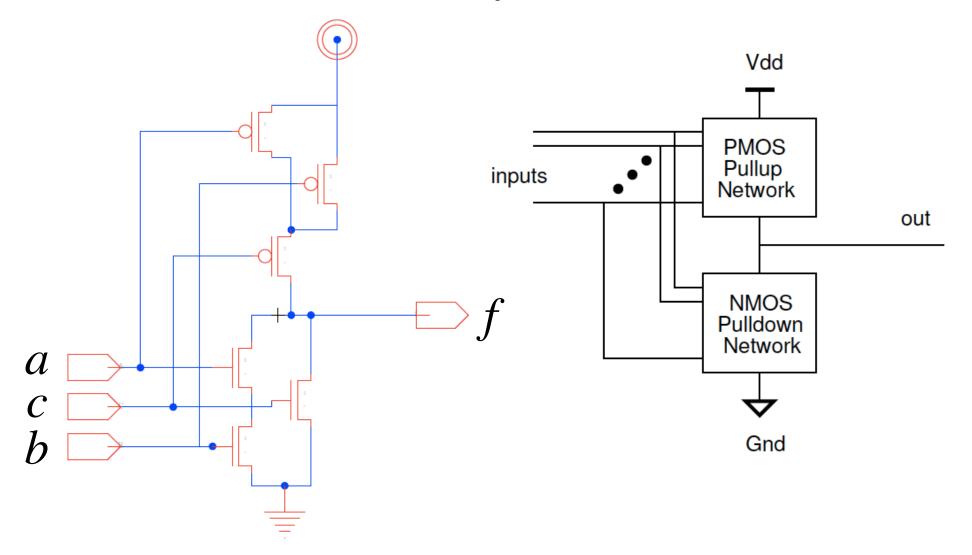

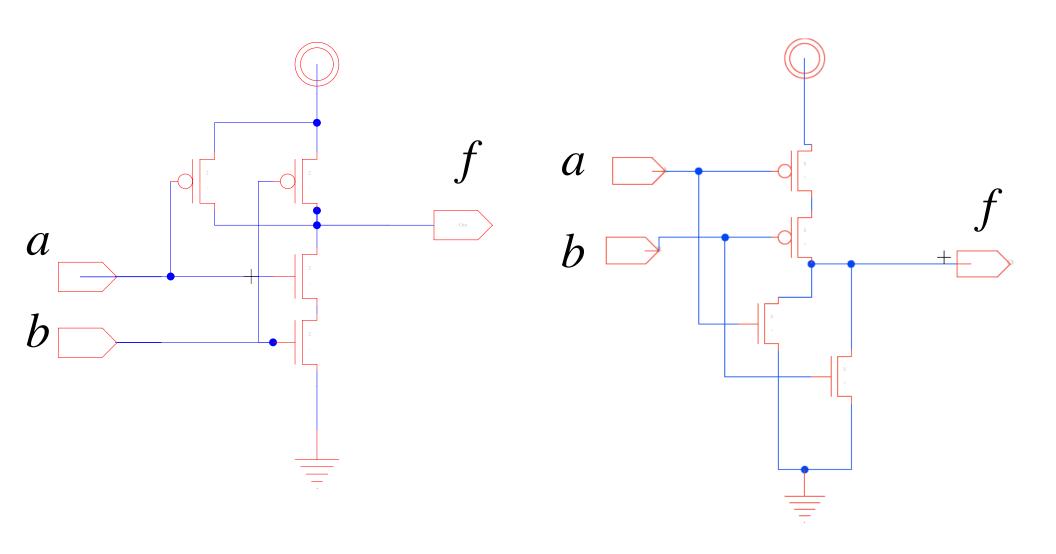

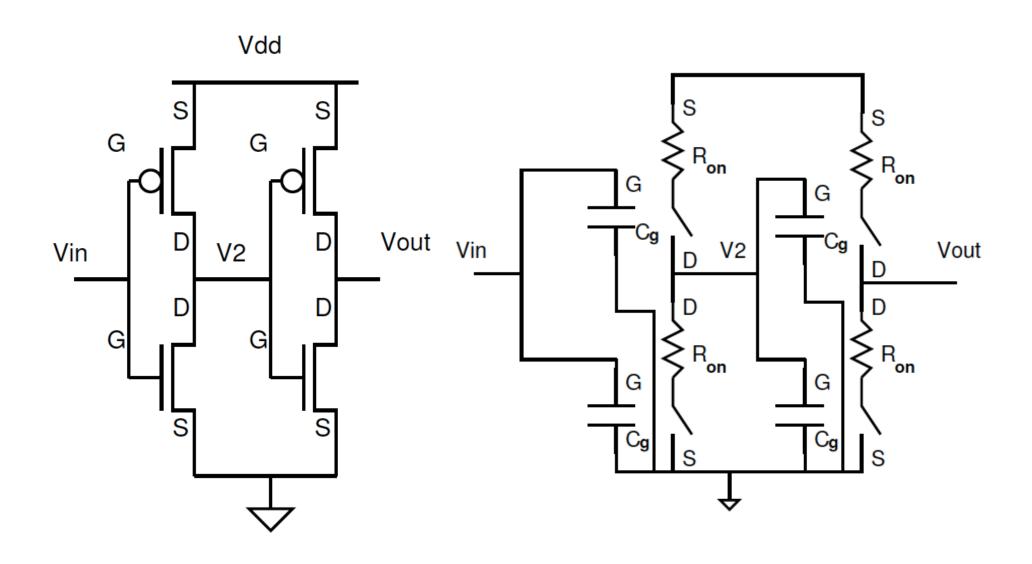

### Static CMOS Gate Structure

### Gate Design Example

Design gate to perform:  $f = (a + b) \cdot c$

### Inverting Stage

■ Each stage of Static CMOS gate is inherently inverting

## NAND/NOR Fundamental Gates

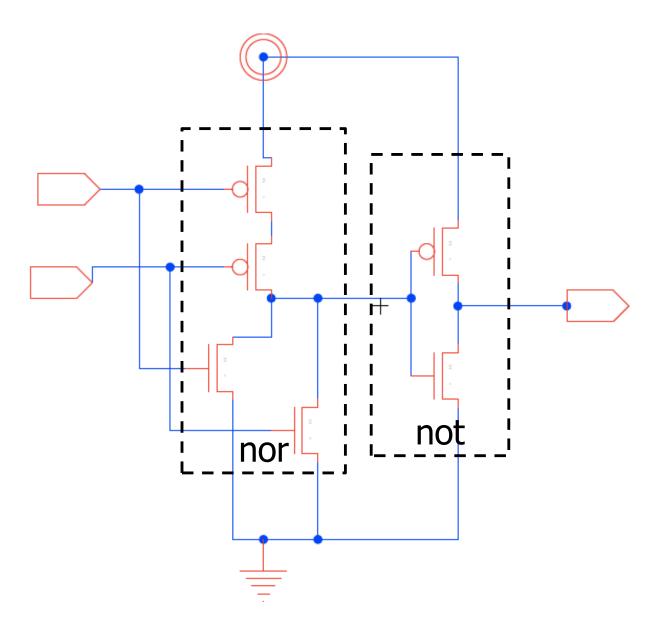

# How implement OR?

# How implement OR?

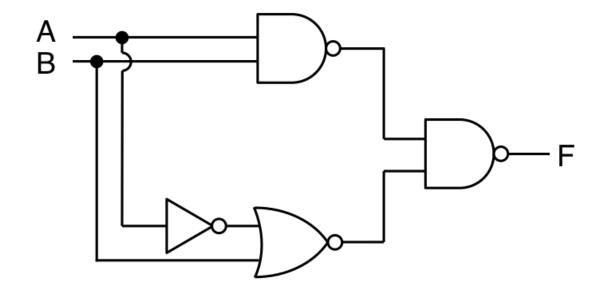

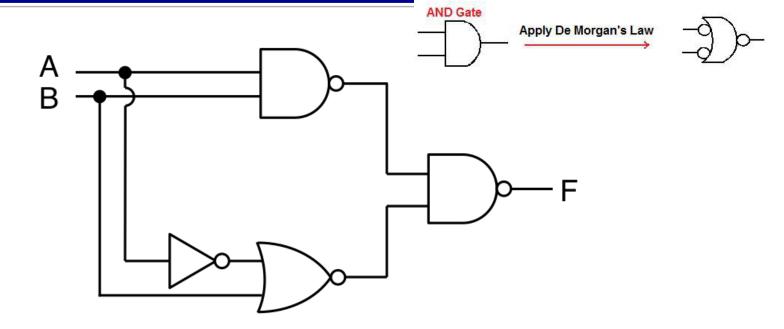

### Cascading Stages

- Can always cascade "stages" to build more complex gates

- Could simply build nor2 or nand2 at circuit level and assemble arbitrary logic by combining – universality

- but may not be smallest/fastest/least power

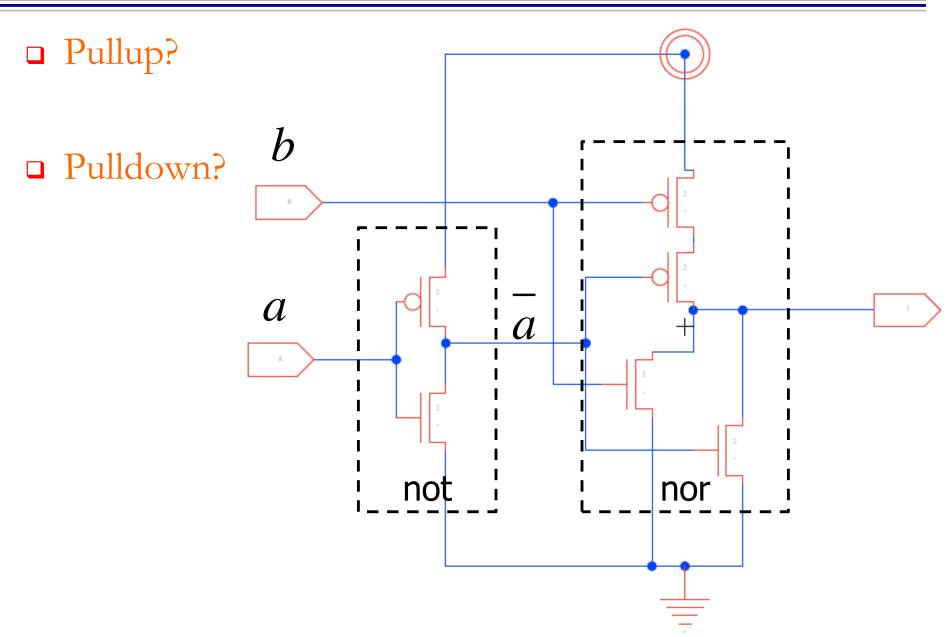

# Implement: $f = a \cdot b$

□ Pullup?

□ Pulldown?

Hint: use cascading stages

# Implement: $f = a \cdot \overline{b}$

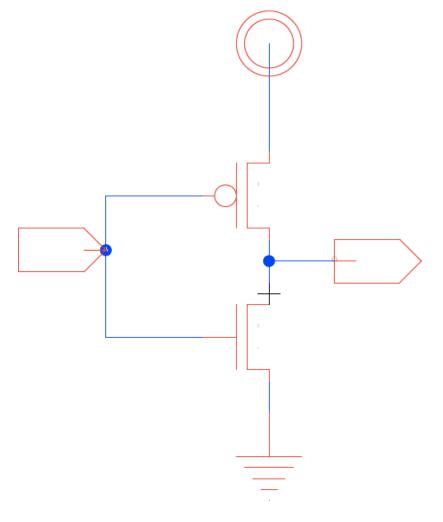

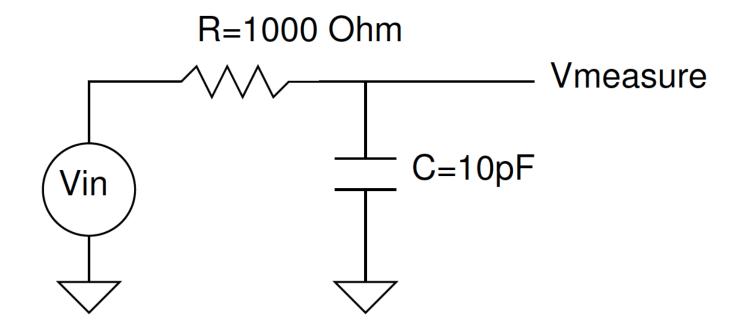

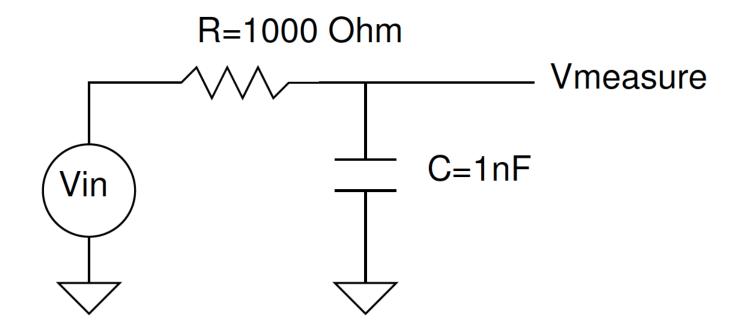

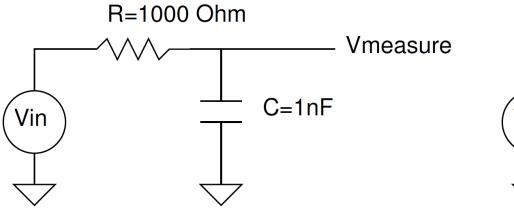

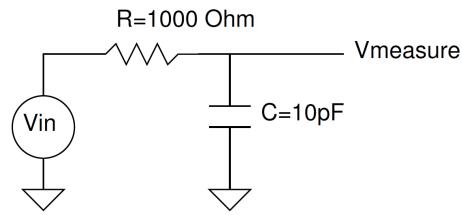

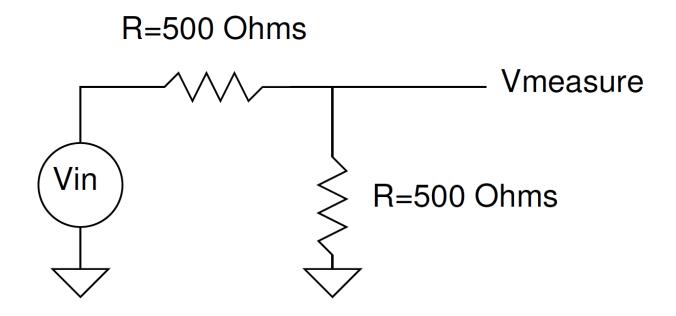

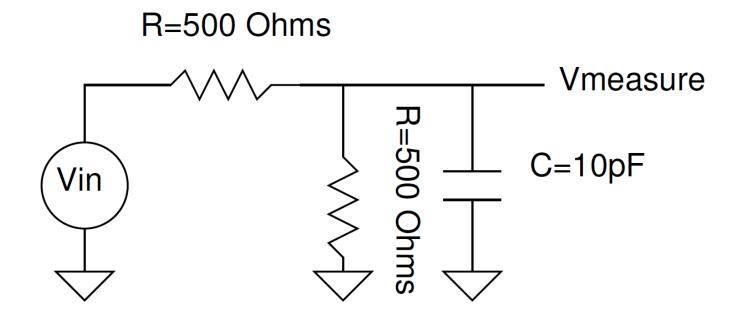

# Final Voltage? (Preclass 4)

Assume  $V_{in}$  is 0 for t < 0 and steps to 1V at t = 0.

What value does  $V_{measure}$  take on as  $t \to \infty$ ?

Assume  $V_{in}$  is 0 for t < 0 and steps to 1V at t = 0.

What value does  $V_{measure}$  take on as  $t \to \infty$ ?

□ Bonus question: Which one will settle faster?

A

В

Assume  $V_{in}$  is 0 for t < 0 and steps to 1V at t = 0.

What value does  $V_{measure}$  take on as  $t \to \infty$ ?

Assume  $V_{in}$  is 0 for t < 0 and steps to 1V at t = 0.

What value does  $V_{measure}$  take on as  $t \to \infty$ ?

### Conclude?

- DC/Steady-State

- Ignore the capacitors

- Look like "open circuit"

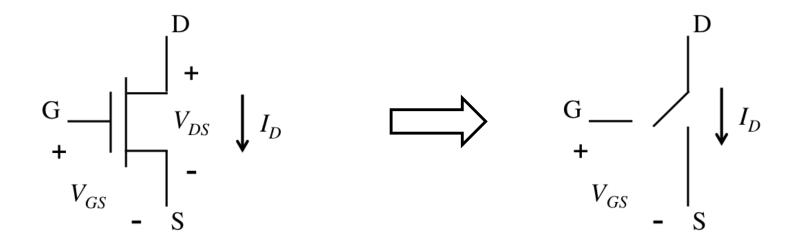

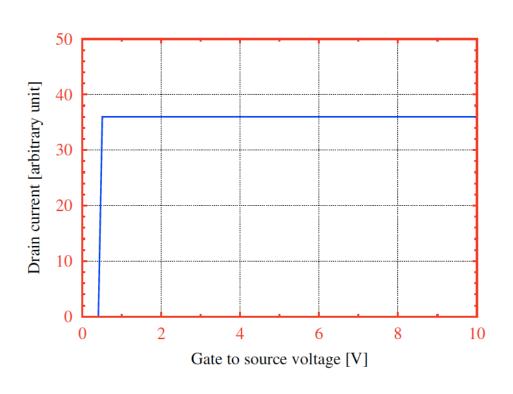

## MOSFET – Zeroeth Order Model

Ideal Switch

$V_{GS} > V_{th} \rightarrow$  switch is closed, conducts  $V_{GS} < V_{th} \rightarrow$  switch is open, does not conduct

- □ Gate draws no current from input

- Loads input capacitively (gate capacitance)

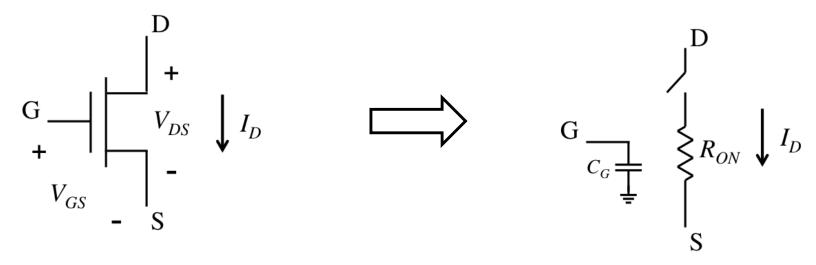

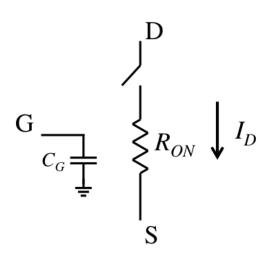

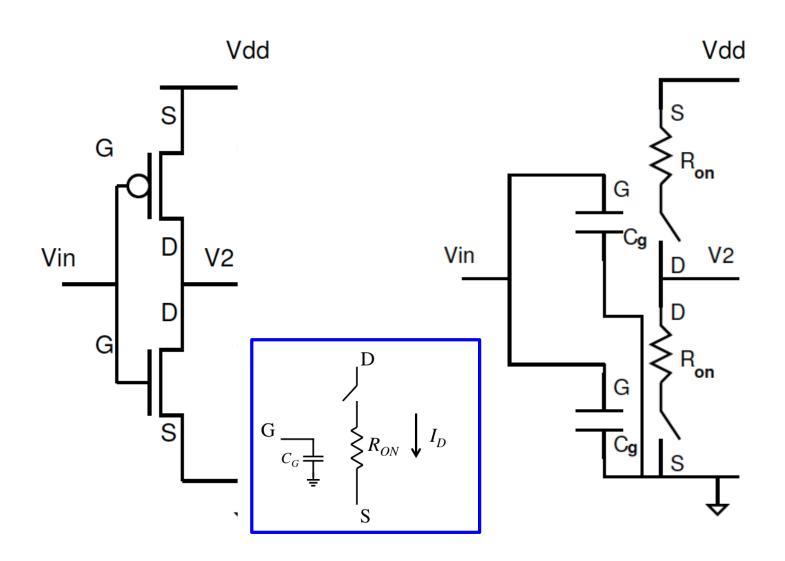

### First Order Model

- Switch

- Loads gate input capacitively

- C<sub>g</sub>

- Has finite drive strength

- $R_{on}$

### First Order Model

- Switch

- Loads gate input capacitively

- C<sub>g</sub>

- Has finite drive strength

- $R_{on}$

What do drive and load mean?

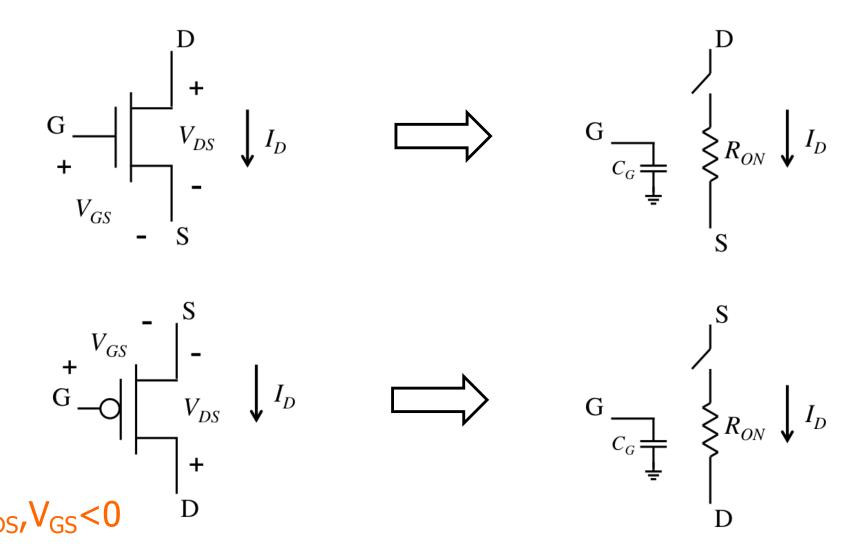

### First Order Model - PMOS

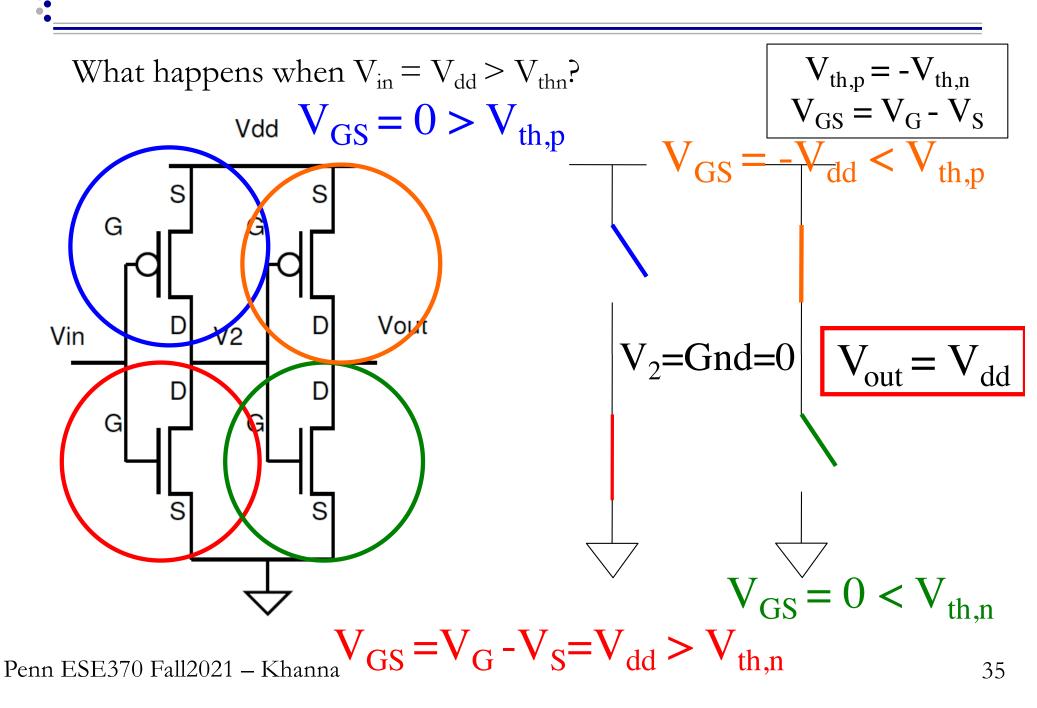

### CMOS Buffer Gate

Stage 1 Stage 2 Vdd G G Vout Vin

### Reminder: Zero-Order Model?

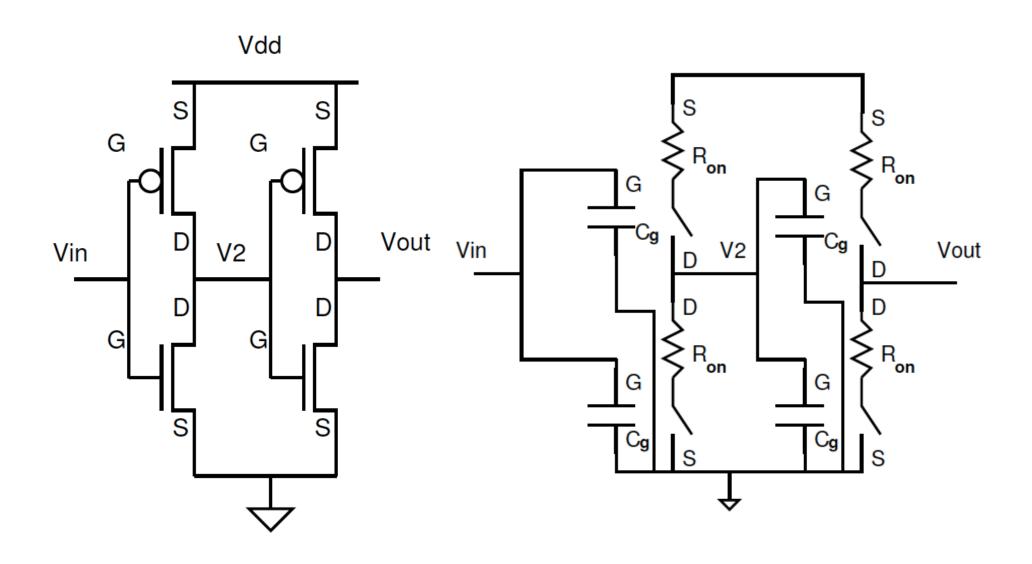

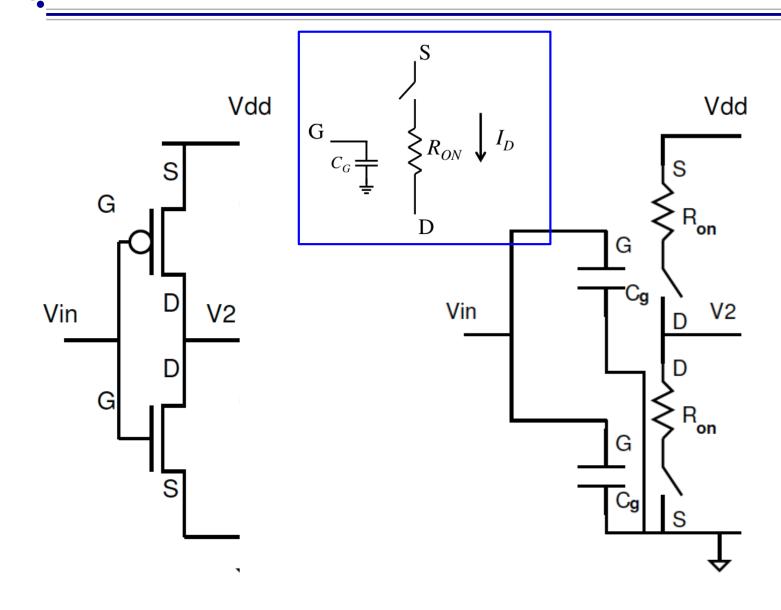

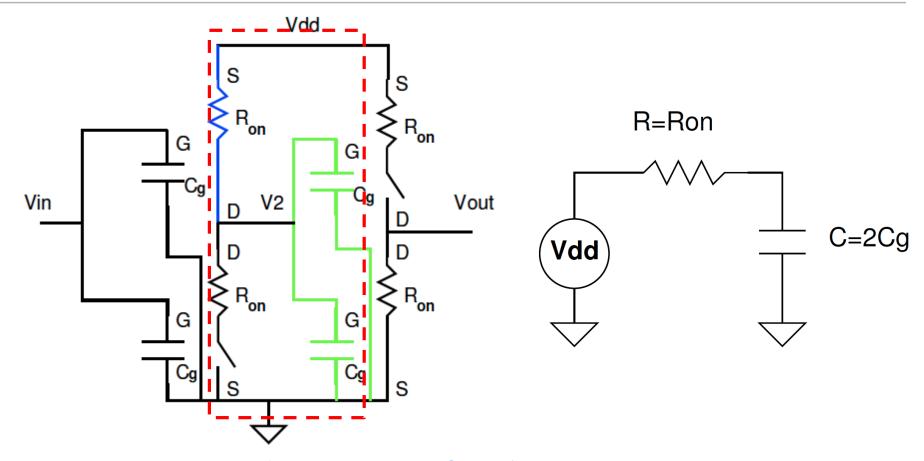

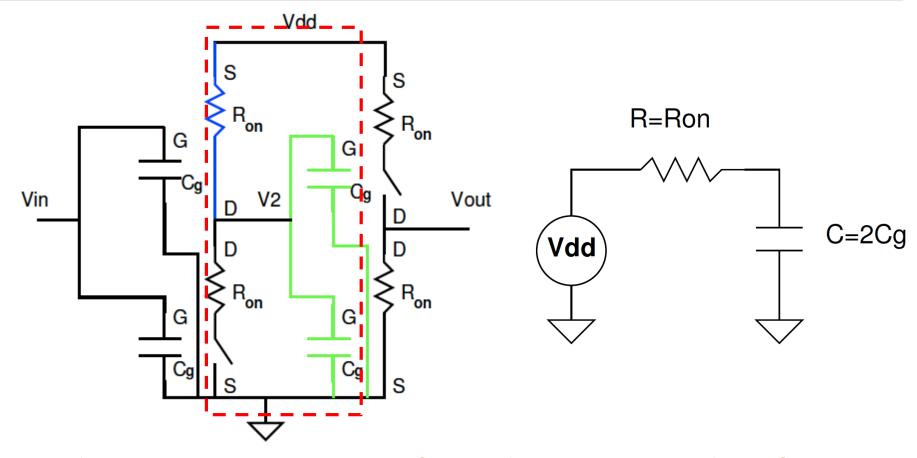

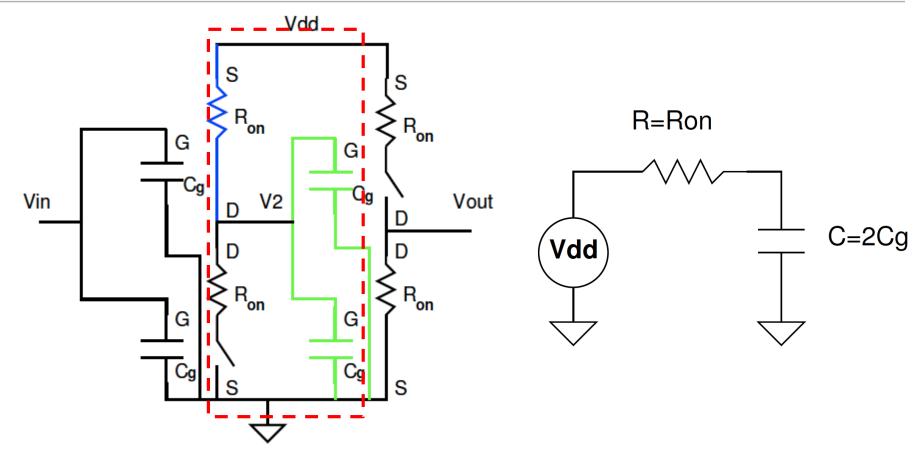

### CMOS Buffer Gate - First Order

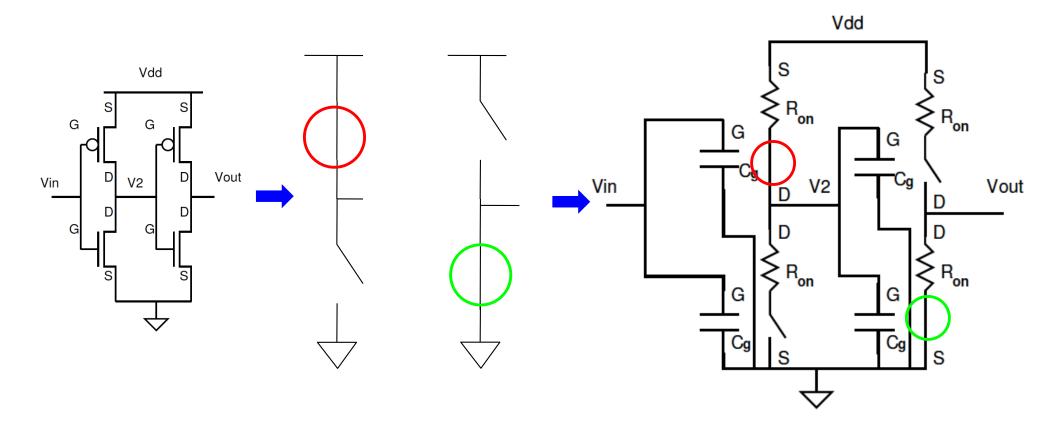

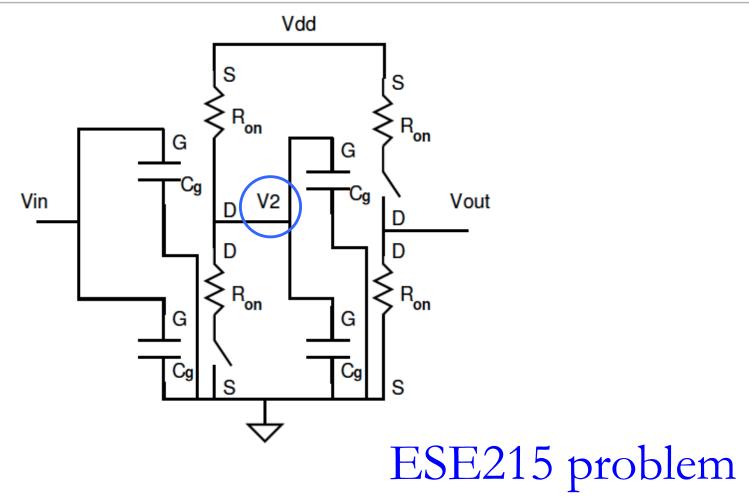

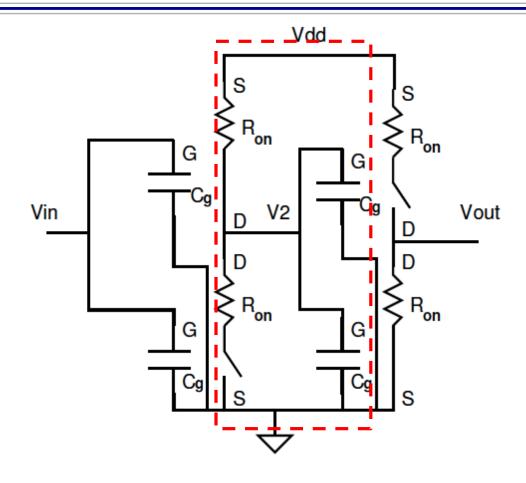

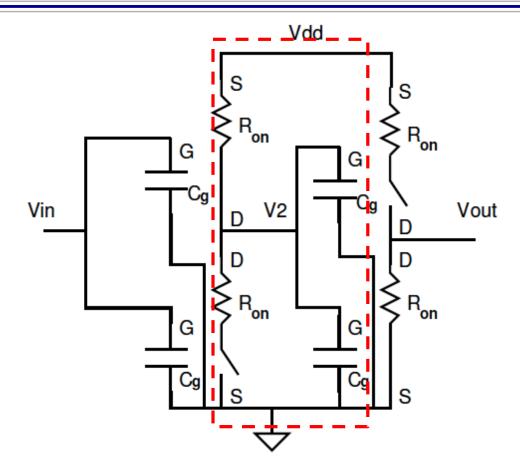

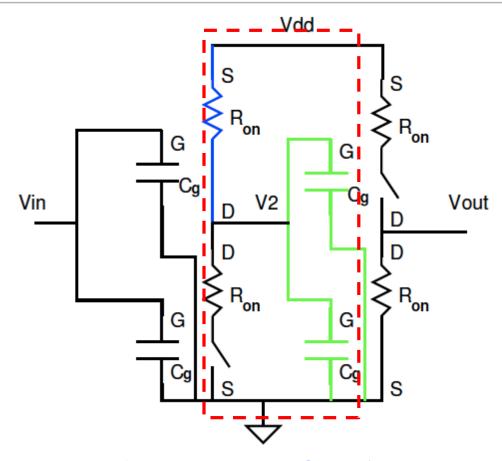

# Zero-Order Model to Set Switches

$\Box$  What is  $V_{IN}$  for this switch pattern?

□ Leaves an RC Circuit we can analyze

- □ Look at intermediary node V<sub>2</sub>

- Connected to output of stage 1 and input of stage 2

■ What is equivalent circuit for the gate output of stage 1 driving  $V_2$ ? What is load on the output of stage 1?

- □ Stage 1 equivalent circuit for the gate output

- Load on V<sub>2</sub>

- Capacitive, input of stage 2

- □ Stage 1 equivalent circuit for the gate output

- Load on V<sub>2</sub>

- Capacitive, input of stage 2

■ What is time constant of  $V_2$  when  $V_{in}$  switches from  $V_{DD}$  to 0?

- □ What is time constant of  $V_2$  when  $V_{in}$  switches from  $V_{DD}$  to 0?

- $= \tau = 2R_{on}C_g$

### First-Order Model

- Includes settling times/delay

- Voltage settling with capacitive loads

- At least some basis for reasoning about delay

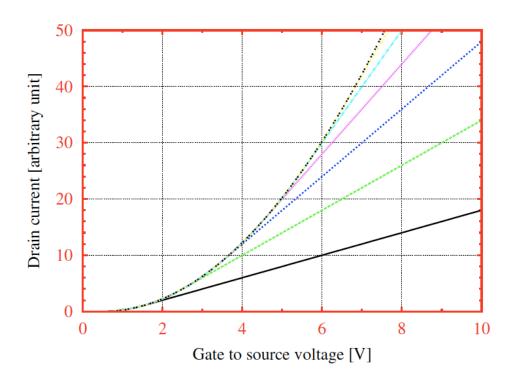

#### IV curve

### 1st Order

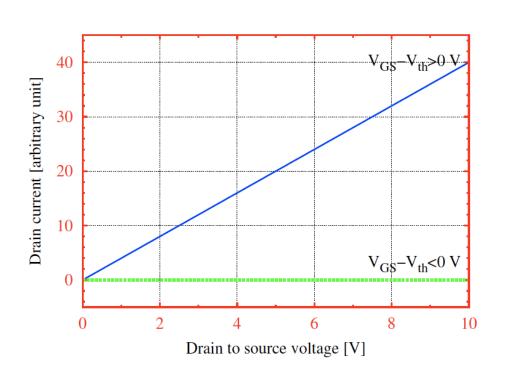

# What is still missing?

#### IV curve

####

#### 1st Order

# What is still missing?

- What happens at intermediate voltages?

- When the input is not rail-to-rail (not just gnd or  $V_{dd}$  inputs)

- Details of dynamics, including...

- Input transition is not an ideal step

- Intermediate drive strengths change with V<sub>GS</sub>

- Drain resistance changes

- Sub-threshold operation

- When  $V_{gs} < V_{th}$

# Design: Engineering Control

- $lue{}$   $V_{th}$

- Process engineer

- □ Drive strength (R<sub>on</sub>)

- Circuit engineer

- Control with sizing transistors

- □ Supply voltages (V<sub>dd</sub>)

- Range set by process engineer

- Detail use by circuit engineer

# Big Ideas

- MOSFET Transistor as switch

- With limited drive

- Purpose-driven simplified modeling

- Aid reasoning, sanity check, simplify design

- Analysis methodology

- Zero order to understand switch state (logic)

- First-order to get equivalent RC circuit (delay)

#### Admin

- Diagnostic grades recorded

- Solutions posted online (pdf in Canvas)

- Make sure you understand

- Diagnose what you need to review and study

- Karnaugh maps (minimum sum of products), RC capacitive settling (time constant), and wire resistive and capacitive properties

- □ HW 1 due Tuesday 9/14 next week

- Because you need Monday lecture for noise margins

- Can look at last year's lecture slides if you want to look ahead

- HW due following Monday 9/20