# ESE370: Circuit-Level Modeling, Design, and Optimization for Digital Systems

### Lec 31: November 24, 2021 Crosstalk

- Crosstalk

- Characterization

- Magnitude

- Avoiding

- Design practices

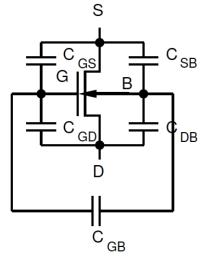

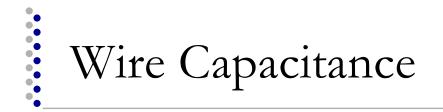

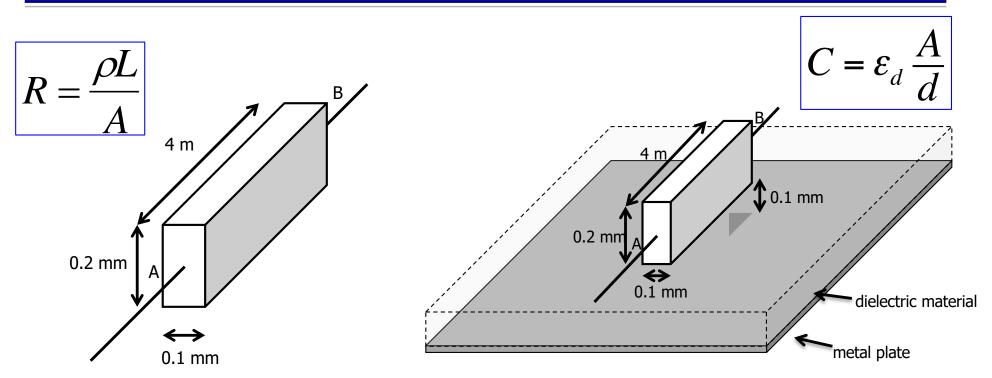

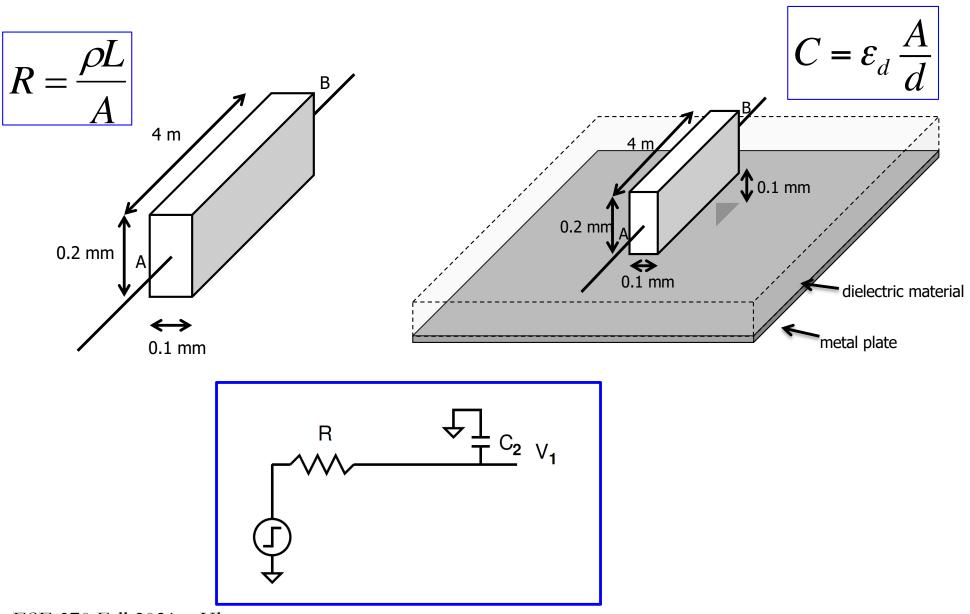

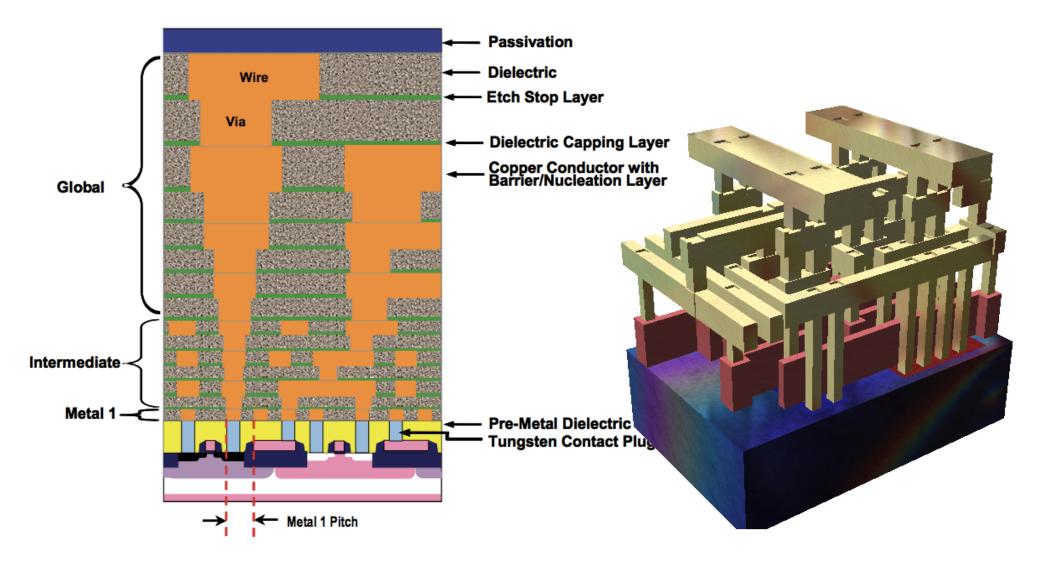

- □ There are capacitors everywhere

- Already talked about

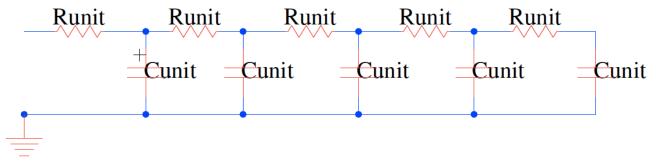

- Wires modeled as a distributed RC network

Parasitic capacitances between terminals on transistor

- Potentially a capacitor between any two conductors

- On the chip

- On the package

- On the board

- □ All wires

- Package pins

- PCB traces

- Cable wires

- Bit/word lines

- □ ...decreases with conductor separation

- □ ...increases with size

- ...depends on dielectric

$C = \varepsilon_r \varepsilon_0 \frac{A}{d}$

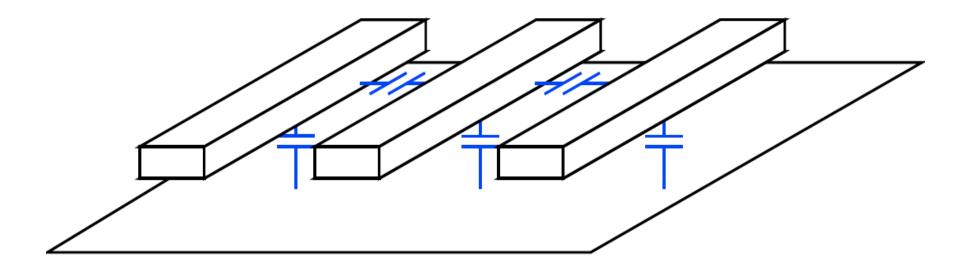

Changes in voltage on one wire may couple through parasitic capacitance to an adjacent wire

- A capacitor does not like to change its voltage instantaneously

- A wire has high capacitance to its neighbor.

- When the neighbor switches from 1-> 0 or 0->1, the wire tends to switch too.

- Called capacitive *coupling* or *crosstalk*.

- Crosstalk effects

- Noise on non-switching wires

- Increased delay on switching wires

### Qualitative

- □ What happens to undriven wire?

- □ Where do we have undriven wires?

□ What happens to a driven "neighbor" wire?

- One wire switches

- Neighbors driven but not switch

- What happens to neighbors?

- □ Can this be a problem?

- What if switching neighbor is:

- Clock line

- Non-clock signal used in synchronous system

- Asynchronous control

- CMOS driven lines

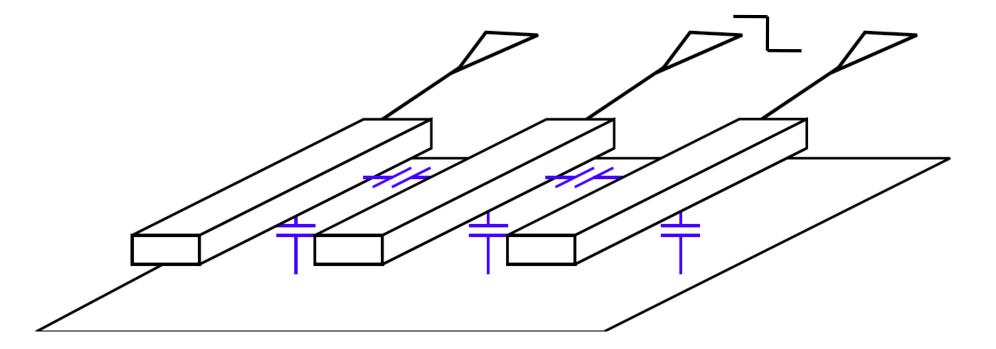

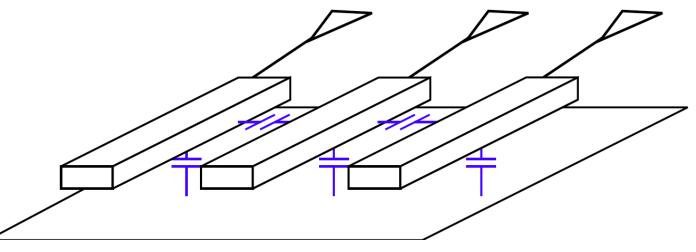

- Clocked logic

- Willing to wait to settle/evaluate

- □ Impact is on delay

- May increase delay of transitions

#### Quantitative

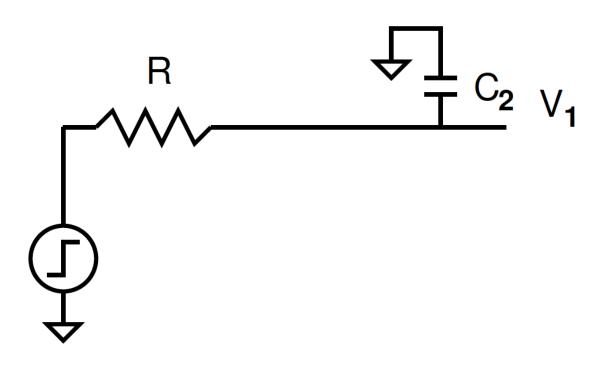

□ Step response for isolated wire?

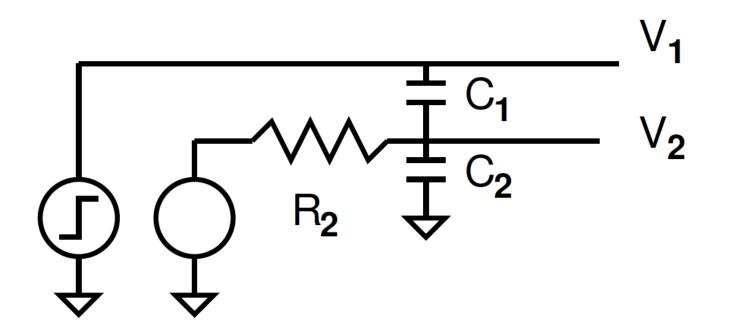

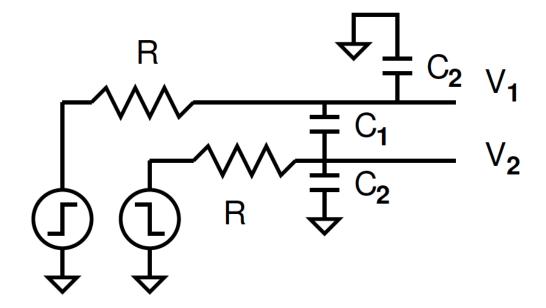

## Undriven Adjacent Wire (preclass 2)

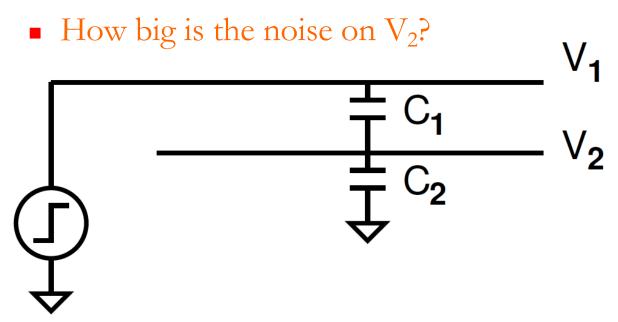

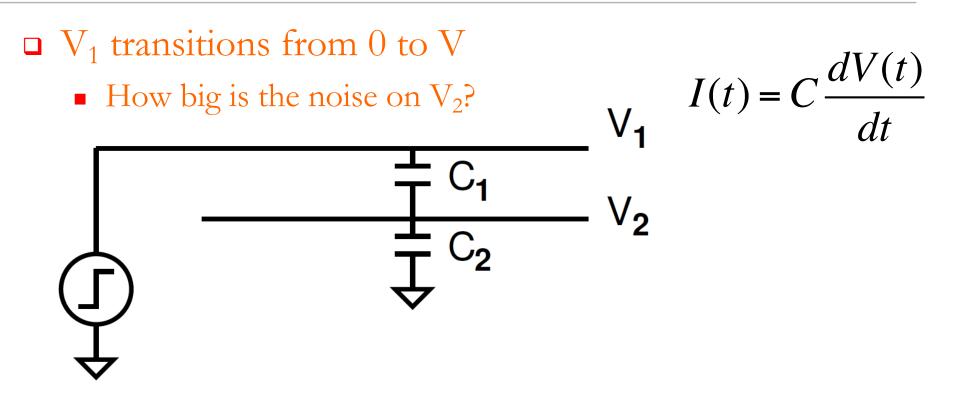

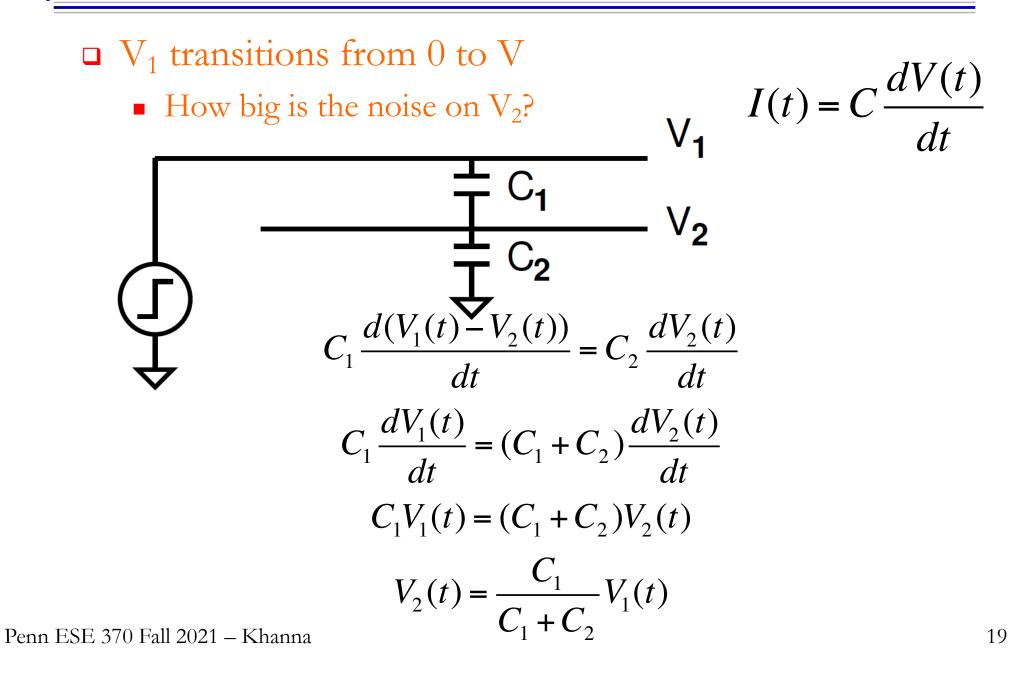

$\square$  V<sub>1</sub> transitions from 0 to V

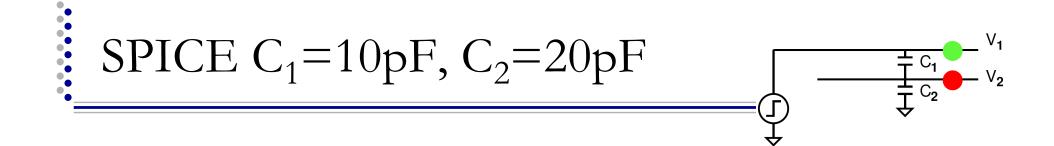

\*\*\* spice deck for cell test\_cap\_undriven{sch} from library test

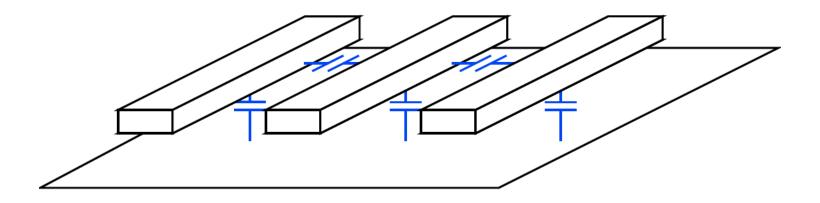

- **\Box** High capacitance to ground plane (C<sub>2</sub>)

- Limits node swing from adjacent conductors

□ What happens when neighbor line is driven?

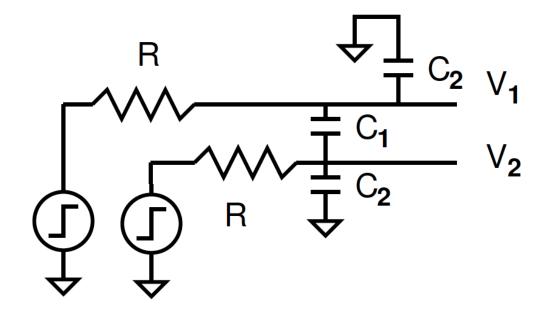

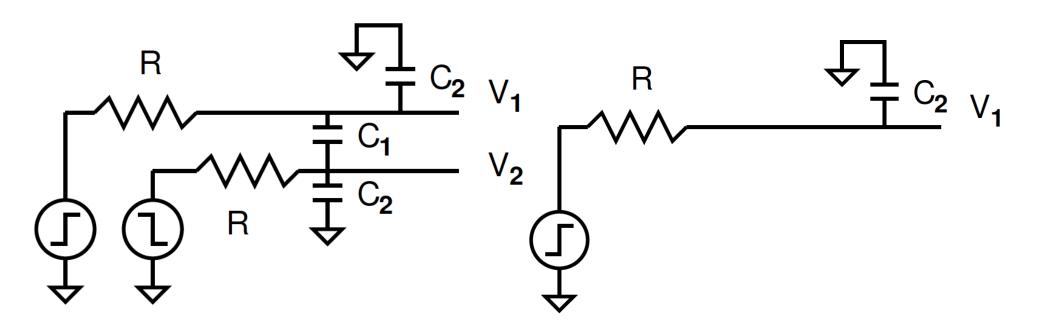

### Driven Adjacent Wire

□ What happens when neighbor line is driven?

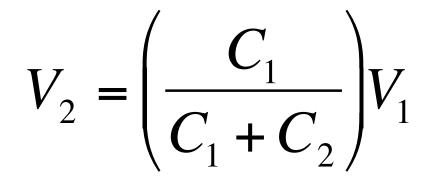

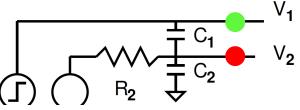

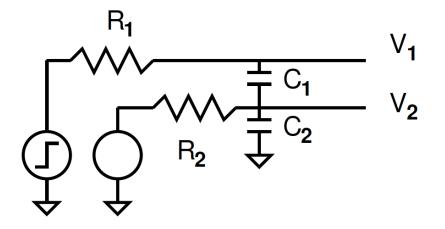

- ٧ı C.  $V_2$  $C_{2}$

- Recovers with time constant:  $R_2(C_1+C_2)$

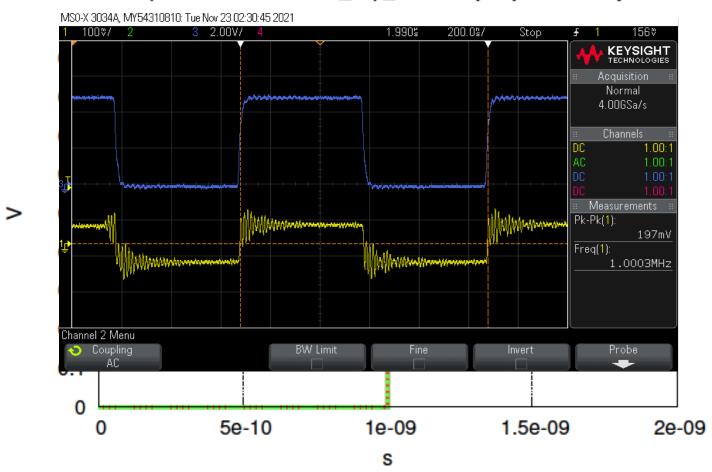

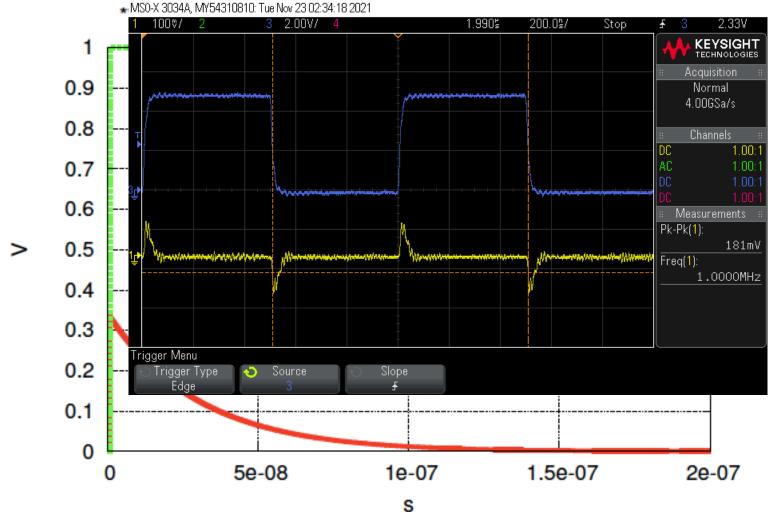

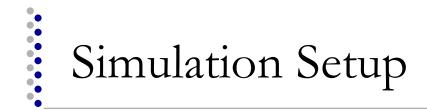

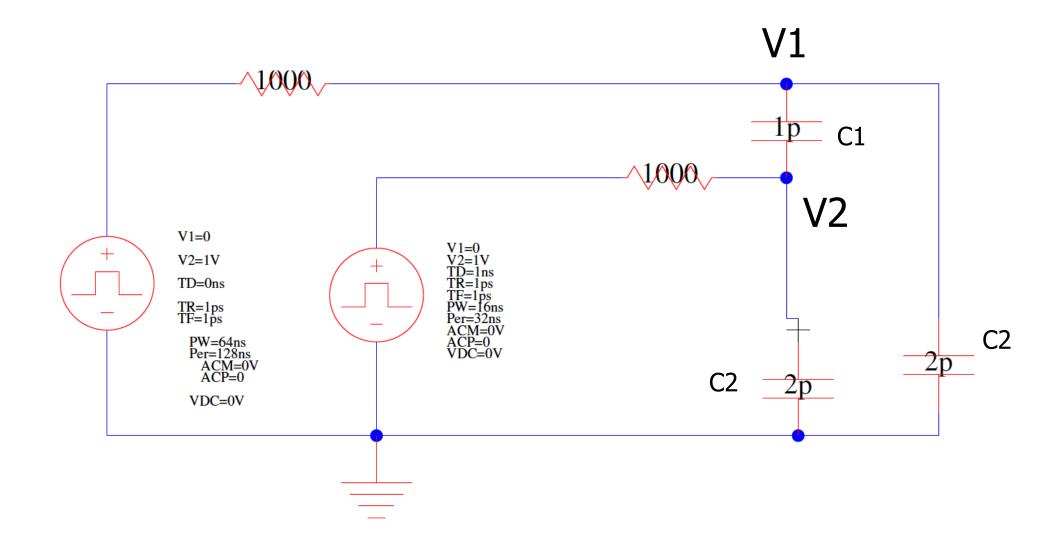

Spice:  $R_2 = 1K$ ,  $C_1 = 10pF$ ,  $C_2 = 20pF$ ٧ı C<sub>1</sub> **√**っ  $R_2$ spice deck for cell test\_cap\_undriven{sch} from library 1 vict **V2** 0.9 aggress **V1** 0.8 0.7 0.6 diversion > 0.5 0.4 0.3 0.2 0.1 0 5e-08 1e-07 1.5e-07 2e-07 0 s

Penn ESE 370 Fall 2021 – Khanna

Spice: R<sub>2</sub>=1K, C<sub>1</sub>=10pF, C<sub>2</sub>=20pF

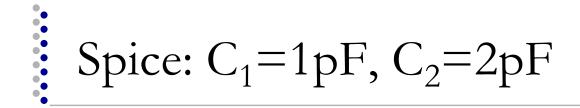

# Magnitude of Noise on Driven Line (preclass 3)

- Magnitude of diversion depends on relative time constants

- $\tau_1 << \tau_2$

- $\tau_1 >> \tau_2$

- $\tau_1 \sim = \tau_2$

- Magnitude of diversion depends on relative time constants

- $\tau_1 << \tau_2$

- full diversion, then recover

- $\tau_1 >> \tau_2$

- Drive capacitor (C<sub>2</sub>) faster than line 1 can change

- little noise

- $\tau_1 \sim = \tau_2$

- Somewhere in between

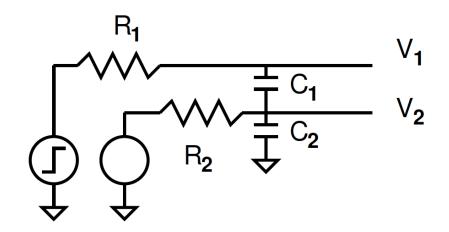

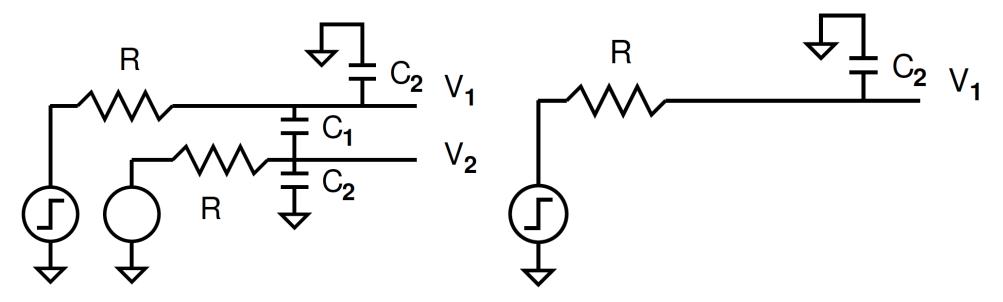

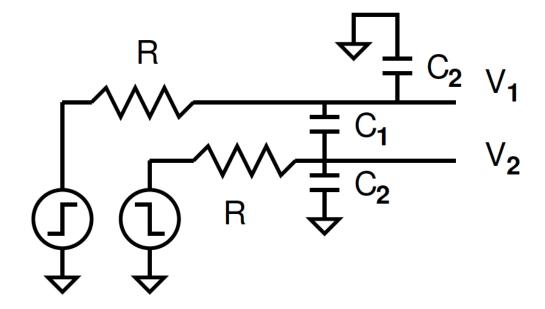

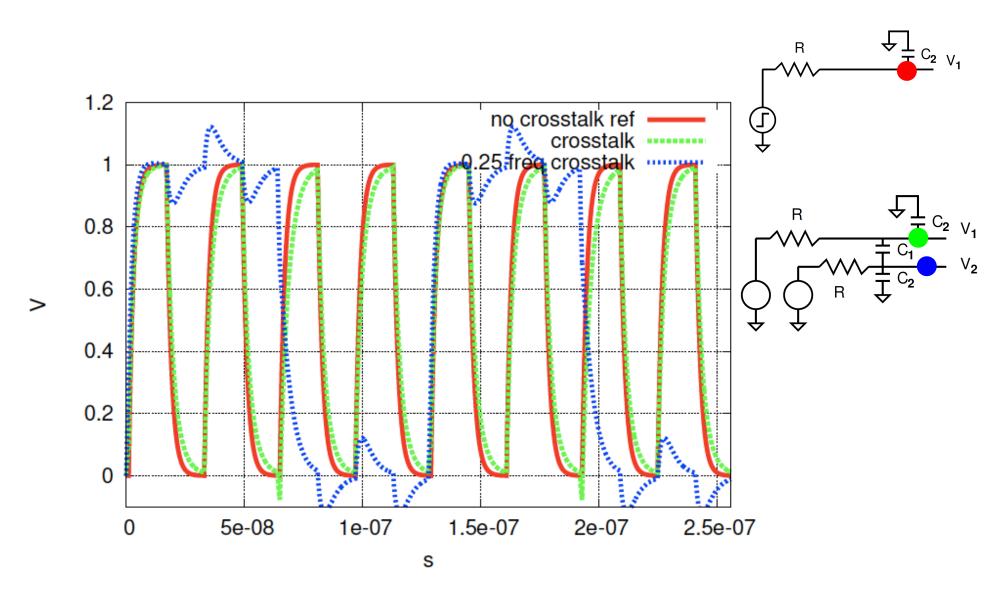

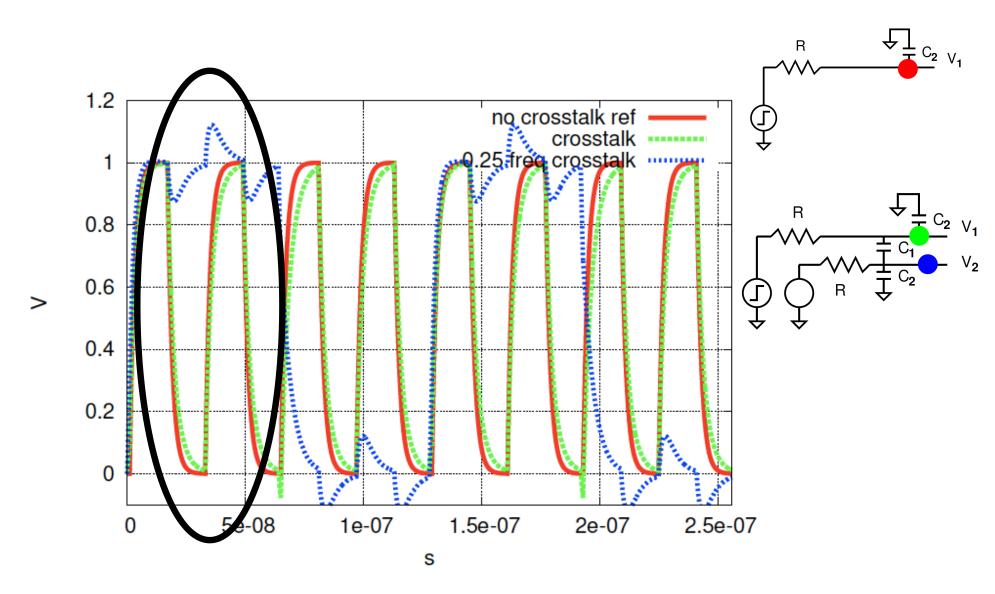

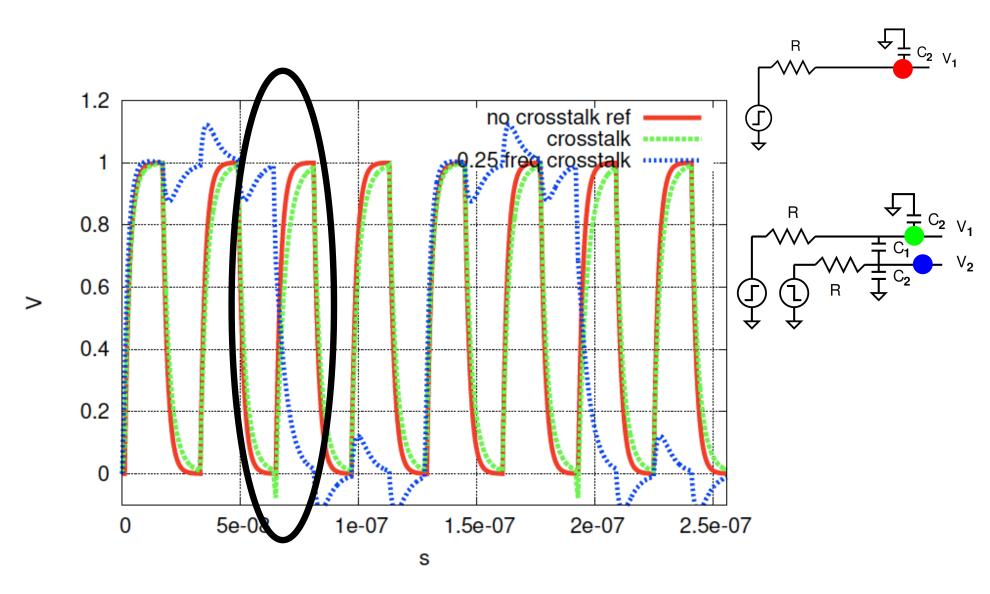

## Switching Line with Finite Drive

- What impact does the presence of the neighbour line have on the switching line?

- All previous questions were about noise on nonswitching wire

- Finite drive (R)

What happens if lines transition in opposite directions?

- What happens if lines transition in opposite directions?

- Must charge C<sub>1</sub> by 2V

- Or looks like 2C<sub>1</sub> between wires

□ What happens if lines transition in same direction?

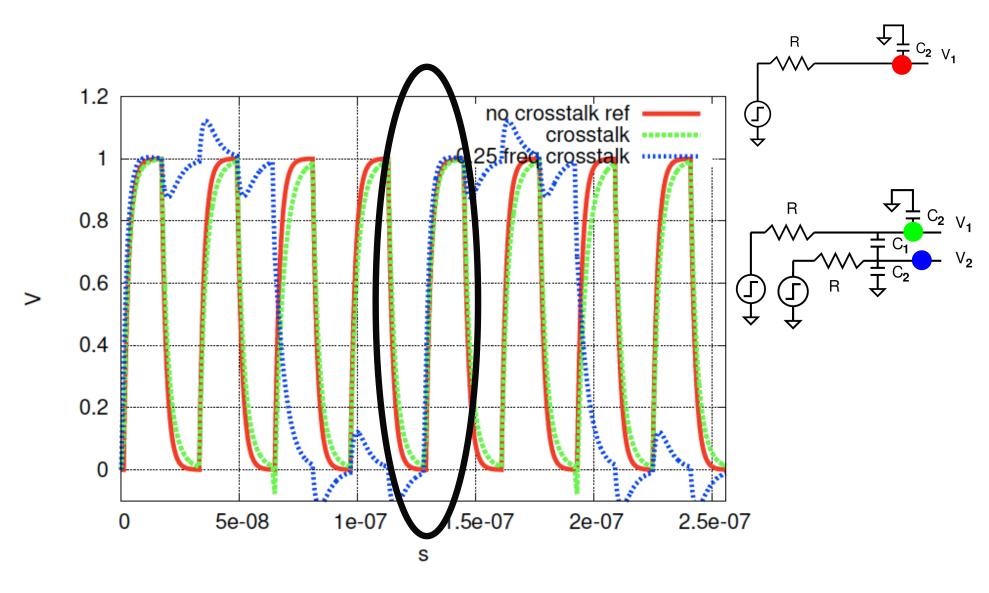

- $V_2$  switching at  $\frac{1}{4}$  frequency of  $V_1$

- $\square$  No crosstalk reference case where no V<sub>2</sub>

Penn ESE 370 Fall 2021 – Khanna

Penn ESE 370 Fall 2021 – Khanna

Penn ESE 370 Fall 2021 – Khanna

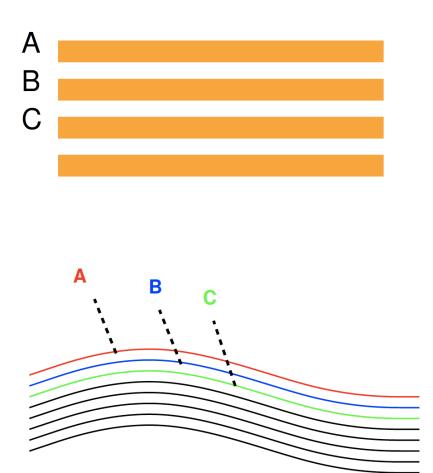

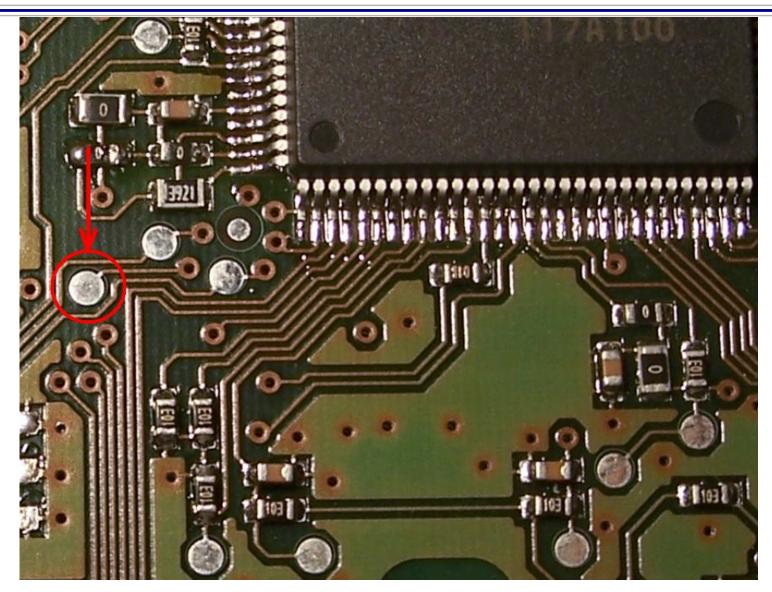

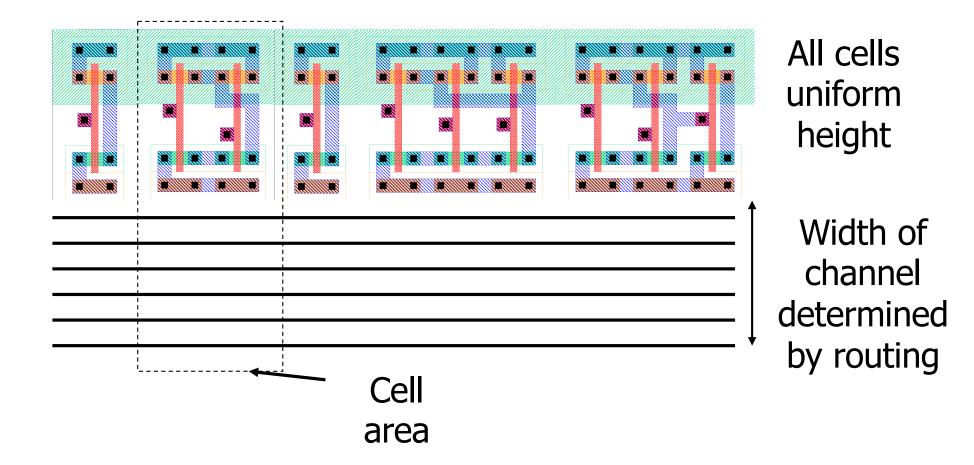

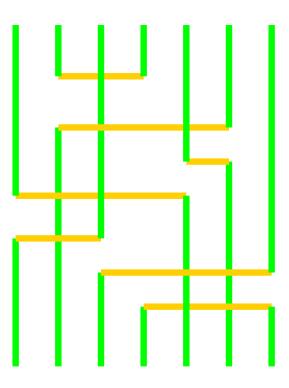

## Where Does it Arise?

Source; http://en.wikipedia.org/wiki/File:Flachbandkabel.jpg

Source: http://en.wikipedia.org/wiki/File:Testpad.JPG Penn ESE 370 Fall 2021 – Khanna

Will be capacitively coupled to many adjacent wires of varying degrees

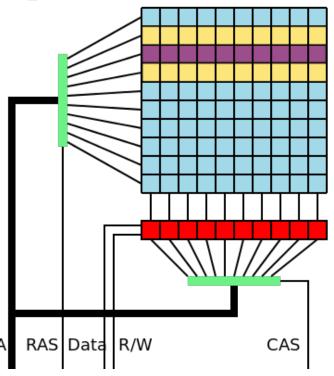

- Smaller and higher density DRAMs leads to increase electromagnetic interactions between memory cells

- Rapid wordline switching can affect adjacent words causing them to flip

## Noise Implications

- So what if we have noise?

- If the noise is less than the noise margin, nothing happens

- Static CMOS logic will eventually settle to correct output even if disturbed by large noise spikes

- But glitches cause extra delay

- Also cause extra power from false transitions

- Dynamic logic never recovers from glitches

- Can't correct mid-cycle, need precharge nodes

- Memories and other sensitive circuits also can produce the wrong result

- Goal: achieve delay, area, power goals with acceptable noise

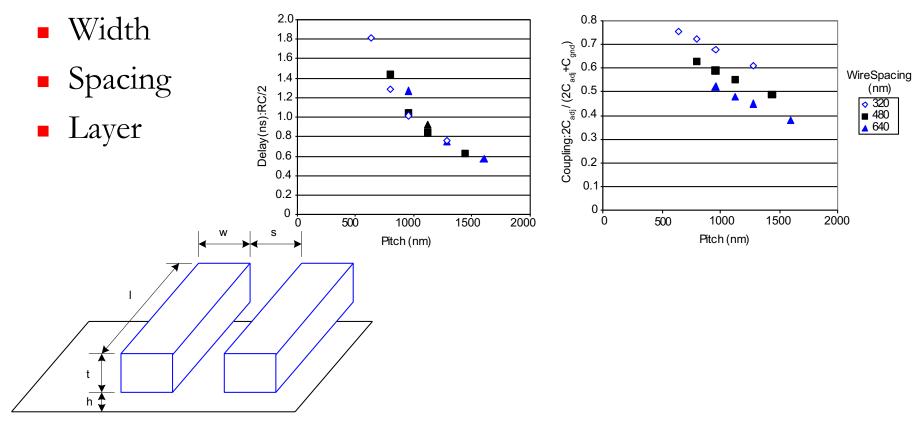

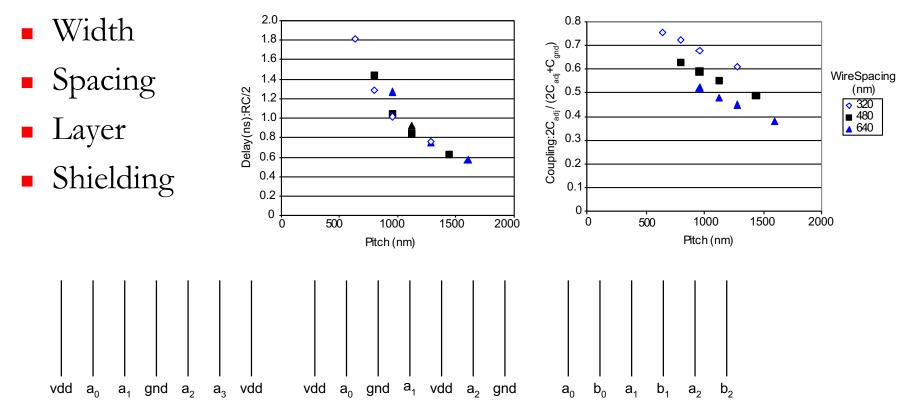

- Degrees of freedom:

- Goal: achieve delay, area, power goals with acceptable noise

- Degrees of freedom:

- Goal: achieve delay, area, power goals with acceptable noise

- Degrees of freedom:

- □ Capacitance is everywhere

- Especially between adjacent wires

- □ Will get "noise" from crosstalk

- Clocked and driven wires

- Slow down transitions

- Undriven wires voltage changed

- Can cause spurious transitions

- □ Monday 11/29 in Ketterer again, no lecture

- Project 2

- Due Friday 12/3

- Milestone feedback:

- Don't forget about the clock

- Controls registers to allow inputs to change at any time, but only affect memory at clk edge

- Non-overlapping clocks!

- Get SRAM column/row working first to make testing/debugging smoother

- Can use a min size cell, just have to justify why that sizing