## University of Pennsylvania Department of Electrical and System Engineering Circuit-Level Modeling, Design, and Optimization for Digital Systems

| ESE370, Fall 2021 | Midterm 2 | Wednesday, November 3 |

|-------------------|-----------|-----------------------|

|-------------------|-----------|-----------------------|

- Point values for each problem are denoted in exam. Point breakdown within problems varies.

- Calculators allowed. No smartphones.

- Closed book = No text or notes allowed.

- $V_{dd}=1$ V,  $V_{thn} = -V_{thp} = 250$ mV,  $\mu_n = \mu_p$ ,  $R_{p0} = R_{n0} = R_0$ , unless otherwise specified in problem.

- Unless otherwise noted, inputs driven by  $R_0$  drive with self load  $2\gamma C_0$ .

A model for the input driver is:

## Name:

Grade:

| Q1    |  |

|-------|--|

| Q2    |  |

| Q3    |  |

| Q4    |  |

| Q5    |  |

| Total |  |

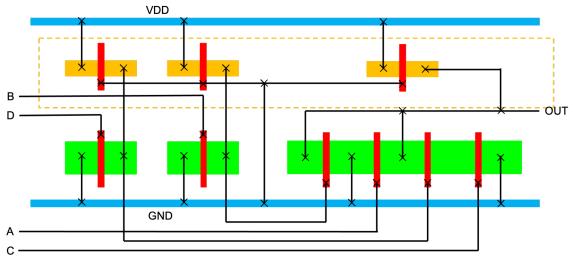

1. (10 points) Below is a stick drawing of the layout of a gate. Identify the logic function of the gate and draw the corresponding schematic for this stick diagram. All Xs represent connections between layers or within the same layer

The original stick diagram on the exam had an error on it. Everyone got full credit. Above is the corrected stick diagram.

- 2. (20 pts) Assume:

- $|V_{T_p}| = |V_{T_n}|$

- $R_0$ =resistance of  $W_n = 1$  NMOS transistor  $\mu_n=300 \text{ cm}^2/(V \cdot s), \ \mu_p=150 \text{ cm}^2/(V \cdot s)$  (I.e.  $R_{p0}=2R_{n0}$ )

- $C_0$  = gate capacitance of  $W_n = 1$  transistor

- $C_{diff}=0$

- The output is loaded with a  $C_{Load} = 8C_0$

- All inputs are driven by inverters with an output resistance of  $R_0/2$

Design a CMOS gate for the function  $OUT = \overline{A} \cdot \overline{B} \cdot C + \overline{C} \cdot \overline{D}$  with sizes labelled for a worst-case output resistance of  $R_0/2$  in each stage. Calculate the worst-case delay in units of  $\tau$  including driving the inputs and worst case switching energy.

| Delay          |  |

|----------------|--|

| Dynamic Energy |  |

3. (30pts) Estimate Delay and Switching Energy for the following implementations of a 5-bit priority encoder. An n-bit priority encoder is a circuit with n inputs,  $A_i$ , and n outputs,  $Y_i$ , where  $0 \le i < n$ , such that

$$Y_i = \begin{cases} 1, & \text{if } A_0 = \dots = A_{i-1} = 0 \text{ and } A_i = 1\\ 0, & \text{otherwise} \end{cases}$$

Informally, a priority encoder identifies the first in the sequence of input bits with value 1. The truth table for a 5-bit priority encoder is given below (for compactness a \* indicates either 0 or 1).

|       | Ι     | nput  | s     |       |       | 0     | utpu  | ts    |       |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| $A_0$ | $A_1$ | $A_2$ | $A_3$ | $A_4$ | $Y_0$ | $Y_1$ | $Y_2$ | $Y_3$ | $Y_4$ |

| 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0     | 0     | 0     | 0     | 1     | 0     | 0     | 0     | 0     | 1     |

| 0     | 0     | 0     | 1     | *     | 0     | 0     | 0     | 1     | 0     |

| 0     | 0     | 1     | *     | *     | 0     | 0     | 1     | 0     | 0     |

| 0     | 1     | *     | *     | *     | 0     | 1     | 0     | 0     | 0     |

| 1     | *     | *     | *     | *     | 1     | 0     | 0     | 0     | 0     |

For the rest of the problem assume:

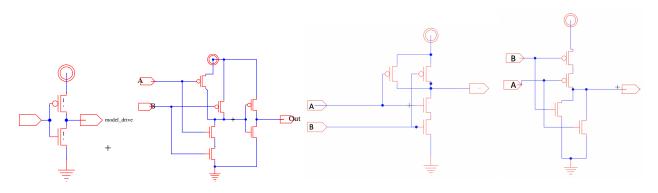

- Inverter, and2, nand2, and nor2 schematics given below.

- All transistors W=L=1.

- Give answers in terms of  $\tau$  and  $\gamma$ ;  $\gamma = C_{diff}/C_{gate}$ .

- Assume all inputs arrive at the same time and are driven by  $R_0$  drive with  $2\gamma C_0$  self load.

- The load on each of the outputs is  $8C_0$ .

- $\mathbf{Y}_{\mathbf{0}}$  $A_0$ A B  $A_1$  $\mathbf{Y}_1$ ωÞ А  $A_2$  $Y_2$ в BA А A 3 Y 3 в ΒÞ A B  $A_4$ Y 4

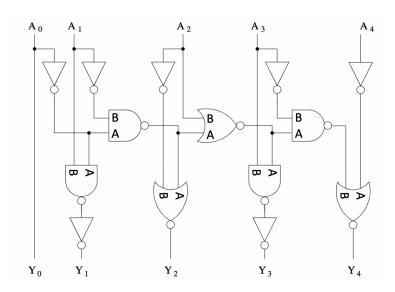

- (a) Below is a daisy chain implementation of the 5-bit priority encoder:

Report worst-case delay for the 5-bit priority encoder from the  $R_0$  input driver driving the inputs through driving the  $8C_0$  load on each  $Y_i$  in units of  $\tau$  and the worst-case dynamic switching energy. Show individual stage delays for partial credit.

| Delay          |  |

|----------------|--|

| Dynamic Energy |  |

(b) Below is an inverting daisy chain implementation of the 5-bit priority encoder:

Report worst-case delay for the 5-bit priority encoder from the  $R_0$  input driver driving the inputs through driving the  $8C_0$  load on each  $Y_i$  in units of  $\tau$  and the worst-case dynamic switching energy. Show individual stage delays for partial credit.

| Delay          |  |

|----------------|--|

| Dynamic Energy |  |

4. (20 points) Pass transistor logic.

For this problem assume:

- $|V_{T_p}| = |V_{T_n}|$

- $R_0$ =resistance of  $W_n = 1$  NMOS transistor

- $R_{0p} = R_{0n}$  = resistance of  $W_p = 1$  PMOS transistor

- $C_0 = \text{gate capacitance of } W_n = 1 \text{ transistor}$

- $C_0$  = gate capacitance of  $W_p = 1$  transistor

- $C_{diff} = \frac{1}{2}C_0$

- All inputs arrive simultaneously

- (a) Design a nor2 gate with restoration using pass transistor logic and CMOS inverters while minimizing area (i.e use as few transistors as possible).

(b) Assuming all transistors are minimum size, estimate the delay in units of  $\tau$  of your nor2 gate assuming the inputs are driven by minimum size inverters and your output is loaded by  $18C_0$ .

(c) Modify your design to reduce the delay (try for 20-50%). Show your new design with transistor sizes specified and report new delay in units of  $\tau$

- 5. (20 pts) Short Answer Questions: Answer the questions briefly. Include diagrams and equations as needed. Be clear in your explanation and handwriting.

- A What effect does increasing  $V_{th}$  have on leakage energy? Explain your answer.

**B** Draw the cross section of a fabricated nMOS device. Label all terminals and indicate the different layers.

**C** A ratioed logic nor2 and nand2 with nMOS PDN and load pMOS device are sized to have the same drive strength. Which one would take more area and why?

${\bf D}\,$  What is velocity saturation and when does it occur?

${\bf E}\,$  How do you measure propagation delay? Use figures and equations to help explain your answer.