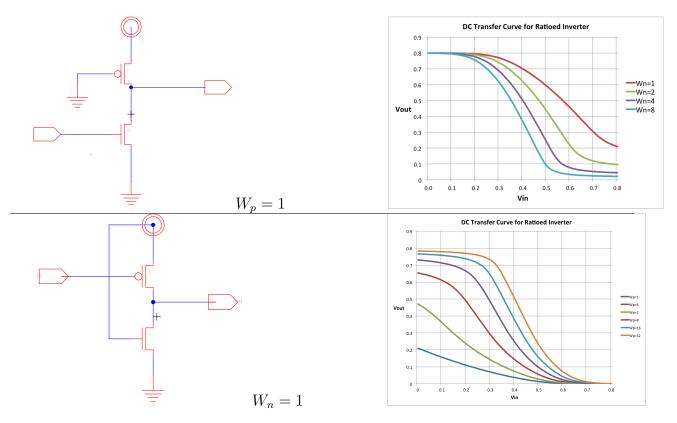

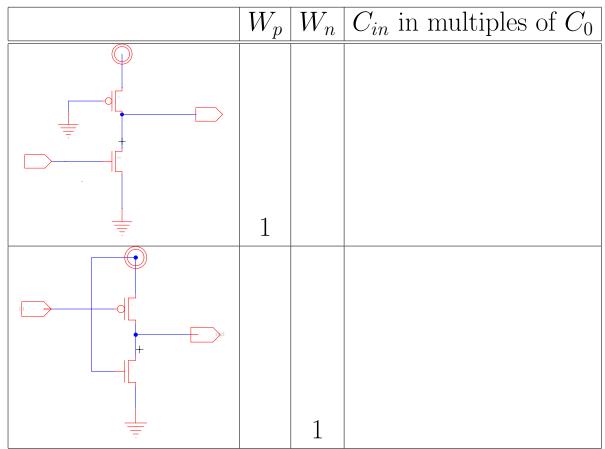

1. Size  $W_n$  or  $W_p$  for correct operation with  $V_{ol} \leq 0.1 V_{dd}$  and  $V_{oh} \geq 0.9 V_{dd}$ , where  $V_{dd} = 0.8$ . Assume extreme velocity saturation,  $R_{0p} = R_{0n}$ .

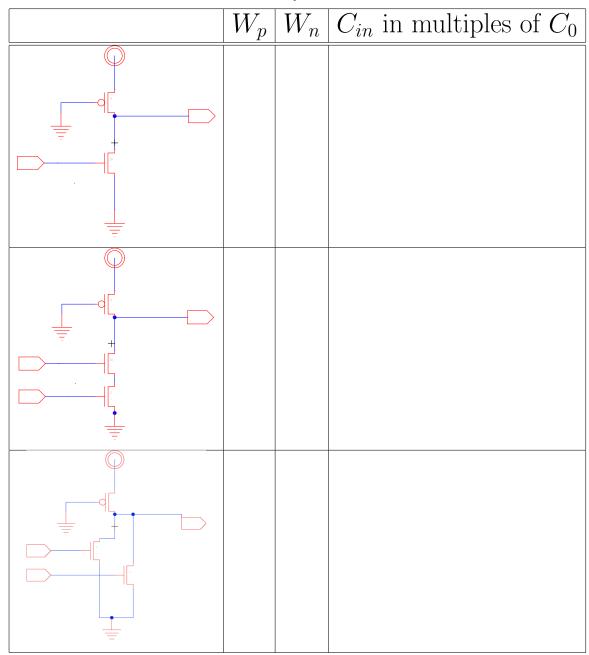

2. Size for  $R_0/2$  worst-case drive (Assume  $R_{p0} = R_{n0}$ ):

3. For a k-input NOR gate, sized for worst-case  $R_{drive} = \frac{R_0}{2}$  (Assume  $R_{p0} = R_{n0}$ ):

|                                         | Ratioed Gate | CMOS |

|-----------------------------------------|--------------|------|

| What is $C_{in}$ as a function of $k$ ? |              |      |

Our design example will be:

Design a circuit to detect when two 32b values match with the minimum energy.

$$Out = (A[31:0] == B[31:0])$$

(1)

- Assume the match condition is relatively uncommon.

- This is a wakeup circuit for some larger computation. The rest of the computation is powered down to save energy. Maybe this is a battery powered device waiting for a password.

- 1. How would you decompose this problem into sub-pieces?

2. How would you perform the match operation using nand2 gates and inverters?

3. Design a single gate that takes in two inputs and has one output at the transistor level that you could use to perform the match condition.

4. List and briefly explain five things in the design space you could explore to look for a good solution? (Said another way: what "knobs" are available for you to turn and "choices" are available for you to make?)