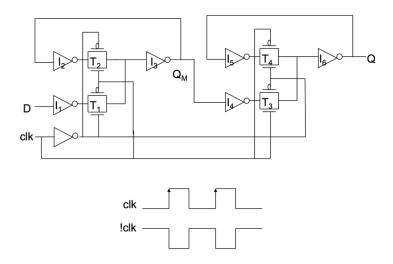

1. Below is a register built with two latches built from transmission gate muxes cascaded together controlled by non-overlapping clocks.

(a) Is this a positive or negative edge-triggered register?

Assume propagation delays are  $t_{pd,inv}$  and  $t_{pd,tx}$  and the inverter delay to drive  $\overline{clk}$  is 0.

- (b) What is the setup time for the register?

- (c) What is the  $CLK \rightarrow Q$  propagation delay?

- (d) What is the hold time?

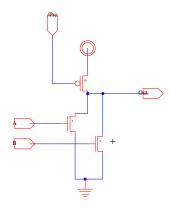

Assume: velocity saturated,  $R_0/2$  sizing for gate drive; inverter sizing is:  $W_n=W_p=2$

## 2. Consider:

- (a) if A=B=0 and /pre is 0, what voltage does Out hold?

- (b) if /pre switches from 0 to 1, and A=B=0, what voltage settles on Out?

- (c) if /pre is at 1 and, B switches from 0 to 1 what voltage settles on Out?

- (d) What are the sizing constraints on the NMOS devices (compare to ratioed logic)?

- (e) What concerns might we have with this logic?

- (f) What requirements must we satisfy for correct operation?

3. Determine delays. Assume  $\frac{R_0}{2}$  drive on inputs, negligible clk drive, and  $R_{0p}=R_{on}$ . (express in  $\tau$  units in terms of  $\gamma$ ):

|             | Precharge                                      | Drive Input | Drive Inv.<br>and Self<br>Output |

|-------------|------------------------------------------------|-------------|----------------------------------|

| CLK  Out  F | (pullup<br>transistor<br>charging<br>inverter) |             |                                  |

|             |                                                | Input       | Self Output<br>Delay             |

|             |                                                |             |                                  |

|             |                                                |             |                                  |