## ESE3700: Circuit-Level Modeling, Design and Optimization for Digital Systems

Lec 4: February 5, 2024 Regenerative Property

- We know how to make our logic functional, but how do we make sure logic is robust?

- To enable design cascading gates into any (feed forward) graph and still tolerate voltage drops and noise, while maintaining digital abstraction

- $\square$  Two signal problems  $\rightarrow$  Gate Cascade failure

- **\Box** Regeneration Solution  $\rightarrow$  Gate Abstraction

- Transfer Curves

- Noise Margins

- Non-linearity

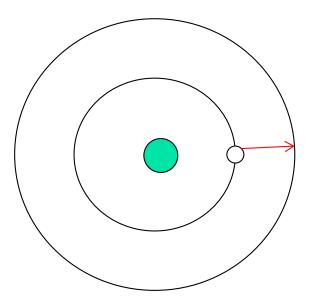

Output does not go to rail Stops short of V<sub>dd</sub> or Gnd

Signals may be perturbed by noise V<sub>x</sub> = V<sub>ideal</sub> ± V<sub>noise</sub>

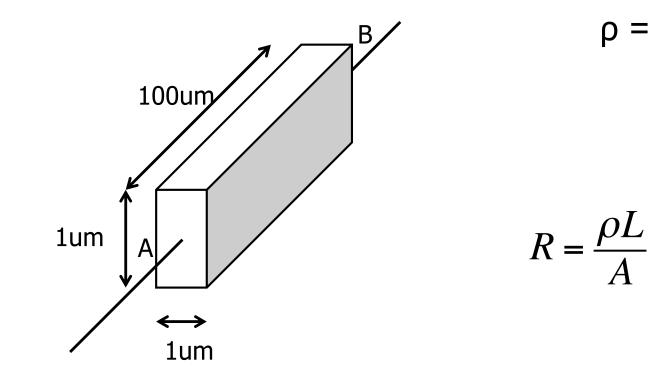

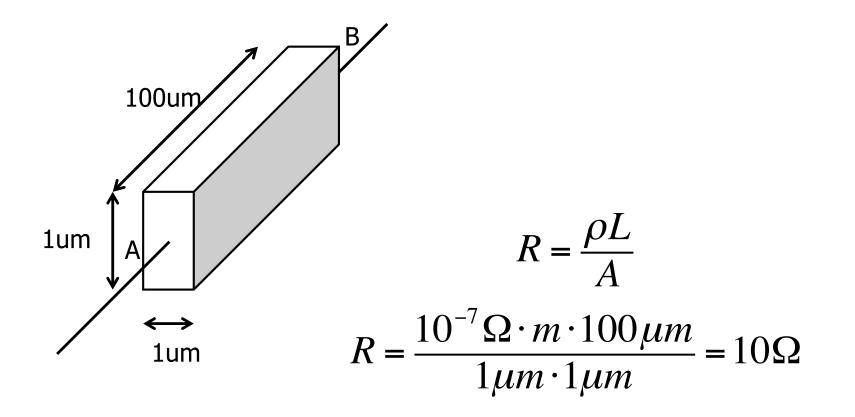

**□** Resistance of 100 µm long wire?

$$\rho = 10^{-7} \Omega \cdot m$$

$\square$  100 µm long wire?

- □ 1 mm long wire?

- □ 1 cm long wire?

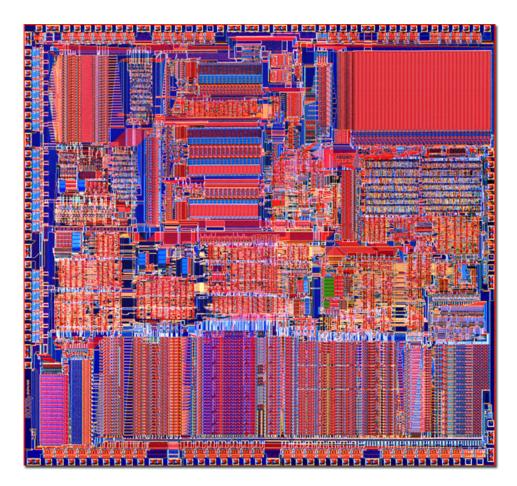

- □ Length of integrated circuit chip side?

- (we often call an IC chip a "die")

| Chip                         | #Trans. | Year | Maker     | process | mm <sup>2</sup> |

|------------------------------|---------|------|-----------|---------|-----------------|

| GK10 Kepler                  | 7B      | 2012 | NVIDIA    | 28nm    | 561             |

| 22-core Xeon<br>Broadwell-E5 | 7B      | 2016 | Intel     | 14nm    | 456             |

| GC2 IPU                      | 23.6B   | 2018 | Graphcore | 16nm    | 825             |

| Apple A12X Bionic            | 10B     | 2018 | Apple     | 7nm     | 122             |

| Tegra Xavier SoC             | 9B      | 2018 | Nvidia    | 12nm    | 350             |

| Navi 10                      | 10B     | 2021 | AMD       | 7nm     | 251             |

| AMD<br>Instinct MI300A       | 146B    | 2023 | AMD       | 5nm     | 1,017           |

#### source: http://en.wikipedia.org/wiki/Transistor\_count

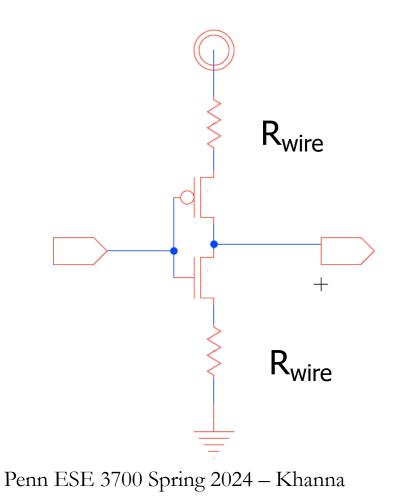

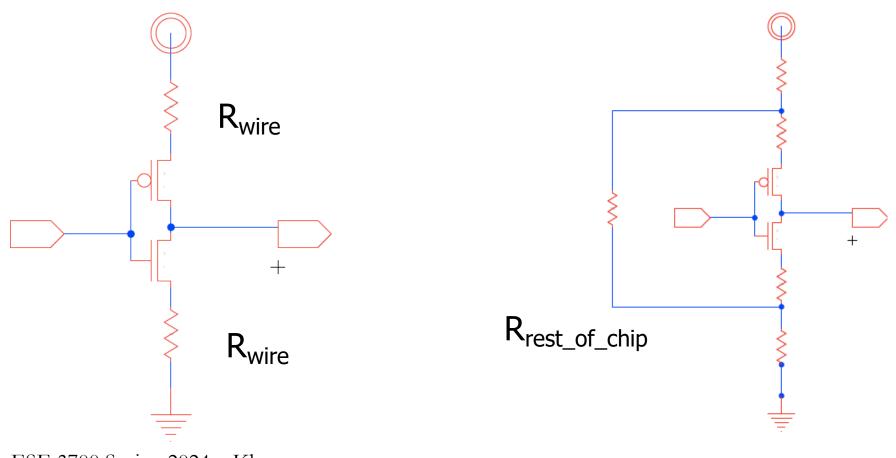

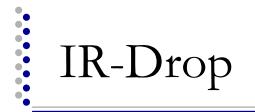

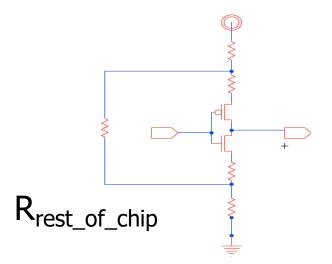

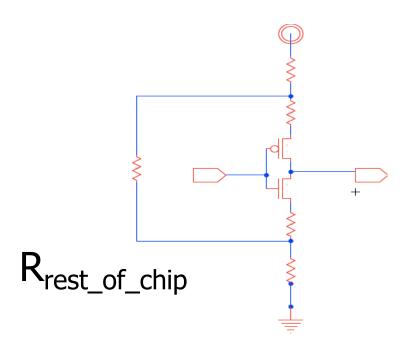

What does the circuit really look like for an inverter in the middle of the chip?

What does the circuit really look like for an inverter in the middle of the chip?

What does the circuit really look like for an inverter in the middle of the chip?

- Since interconnect is resistive and gates pull current off the supply interconnect

- The V<sub>dd</sub> seen by a gate is lower than the supply Voltage by

- $V_{drop} = I_{supply} \ge R_{distributed}$

- Two gates in different locations

- See different R<sub>distributed</sub>

- Therefore, see different V<sub>drop</sub>

Due to V<sub>drop</sub>, "rails" for two communicating gates may not match

- Output not go to rail

Different swing for gates

- 2. Signals may be perturbed by noise

Voltage seen at input to a gate may be lower/higher than input voltage

- Signal coupling

- Crosstalk

- Inductive noise

- Leakage

- Ionizing particles (shot noise)

# Signals will be degraded

- 1. Output not go to rail

- Is this tolerable?

- 2. Signals may be perturbed by noise

- Voltage seen at input to a gate may be lower/higher than expected input voltage

- □ What happens to degraded signals?

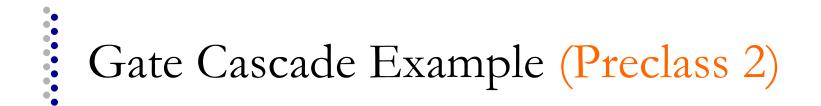

□ What is the output when all inputs are all 1s?

□ What is the output when all inputs are all 1s?

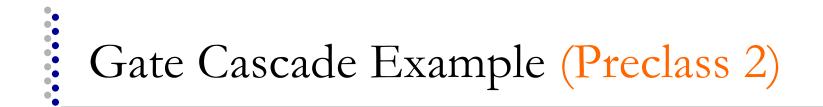

## Gate Cascade Example (Preclass 2)

What is the output when all inputs are all 1.0 and NAND(A, B) = 1-A\*B?

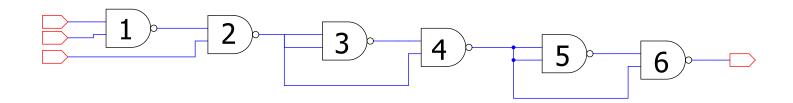

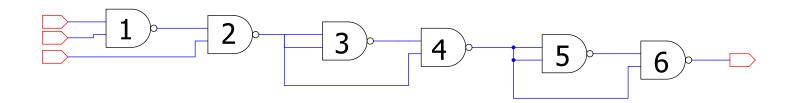

## Gate Cascade Example (Preclass 2)

What is the output when all inputs are all 0.95 and NAND(A, B) = 1-A\*B?

- Cannot have signal degrade across cascaded gates

- □ Want to be able to cascade arbitrary set of gates

- No limit on number of gates to maintain signal integrity

- Gates should leave the signal "better" than they found it

- "better"  $\rightarrow$  closer to the rails

- Define legal inputs

- Gate works if V<sub>in</sub> "close enough" to the rail

- Define legal inputs

- Gate works if V<sub>in</sub> "close enough" to the rail

- Regeneration

- Gate produces V<sub>out</sub> "closer to rail"

- This tolerates some drop between one gate and next (between out and in)

- Call this our "Noise Margin"

### Regeneration/Restoration/Static Discipline

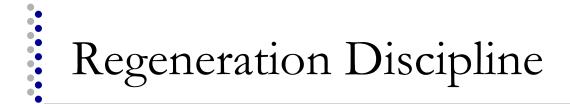

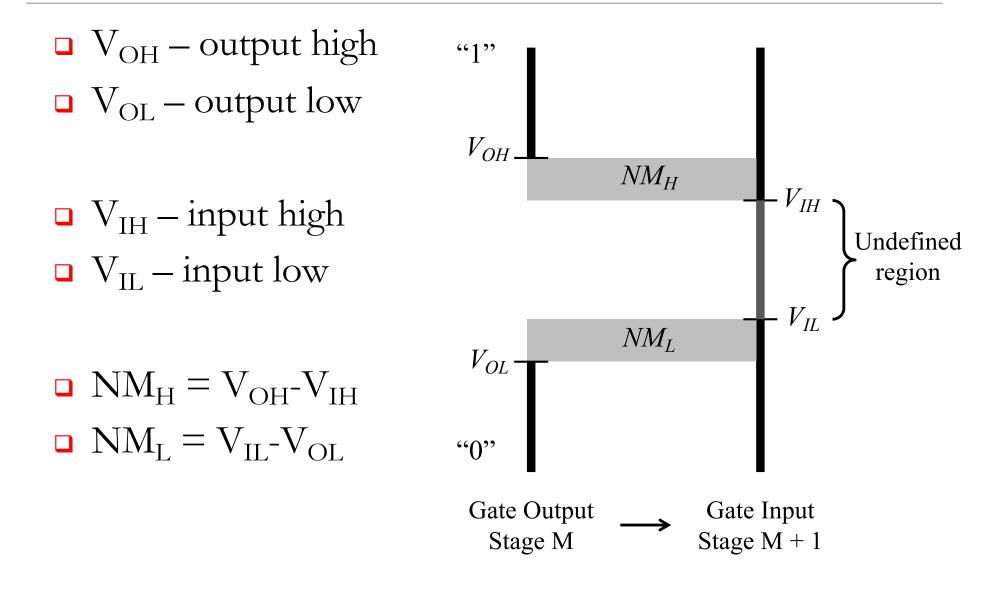

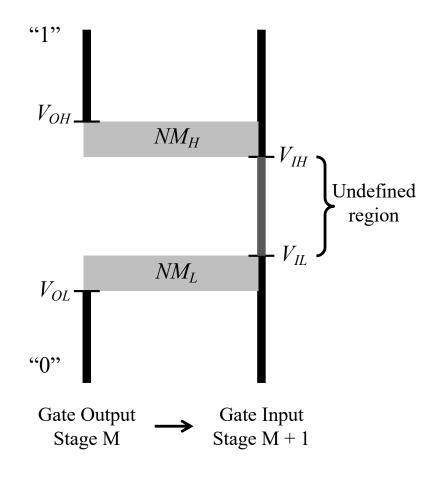

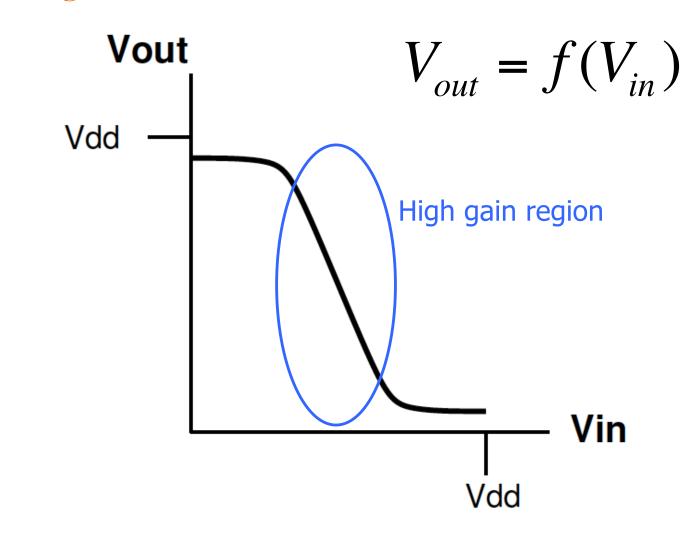

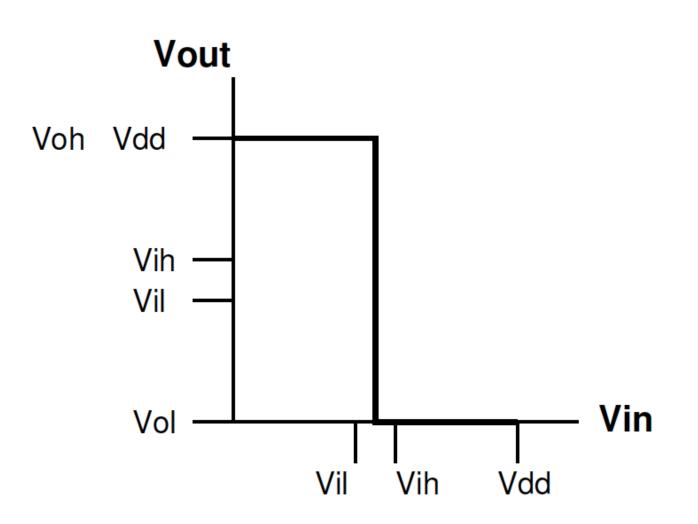

## Regeneration Discipline (getting precise)

- Define legal inputs

- Gate works if V<sub>in</sub> "close enough" to the rail

•

$$V_{in} > V_{IH}$$

or  $V_{in} < V_{IL}$

#### Regeneration

Gate produces V<sub>out</sub> "closer to rail"

•

$$V_{out} < V_{OL}$$

or  $V_{out} > V_{OH}$

## Regeneration Discipline (getting precise)

- Define legal inputs

- Gate works if V<sub>in</sub> "close enough" to the rail

•

$$V_{in} > V_{IH}$$

or  $V_{in} < V_{IL}$

#### Regeneration

Gate produces V<sub>out</sub> "closer to rail"

•

$$V_{out} < V_{OL}$$

or  $V_{out} > V_{OH}$

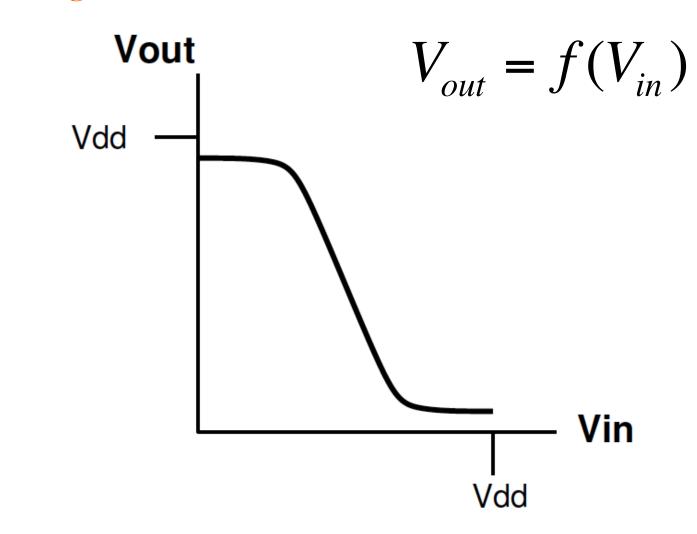

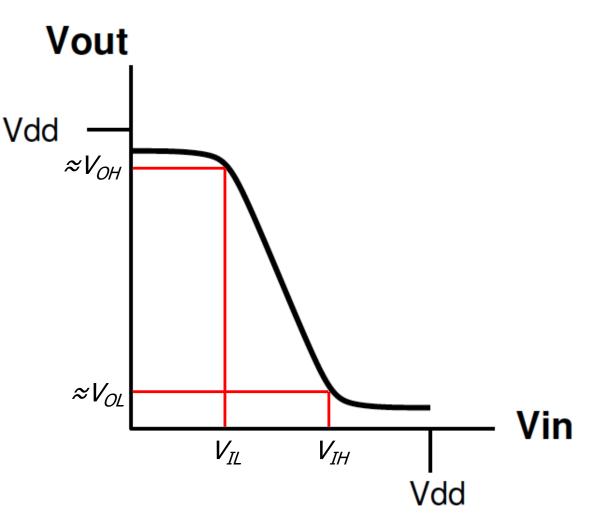

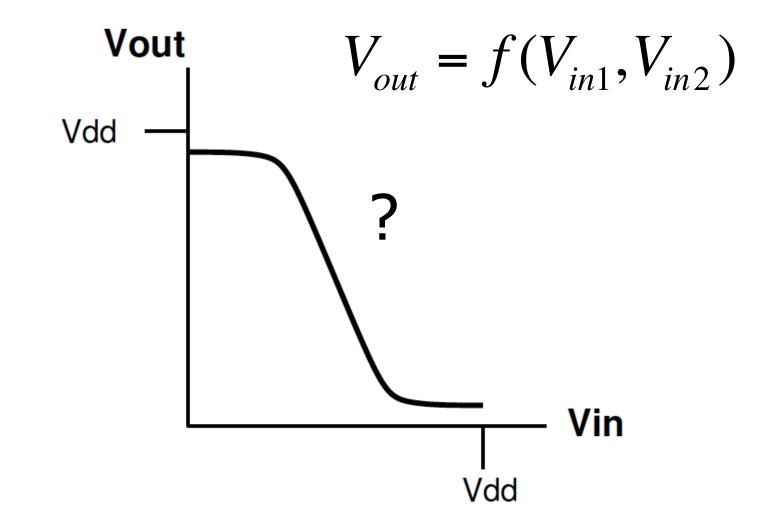

Describes what the output is given logic gate input

•

$$V_{out} = f(V_{in})$$

□ What gate is this?

□ What gate is this?

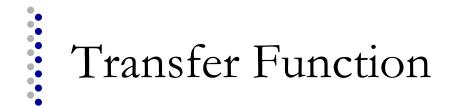

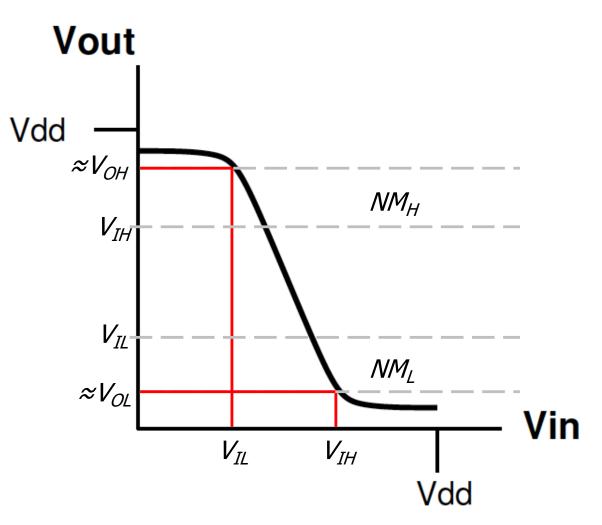

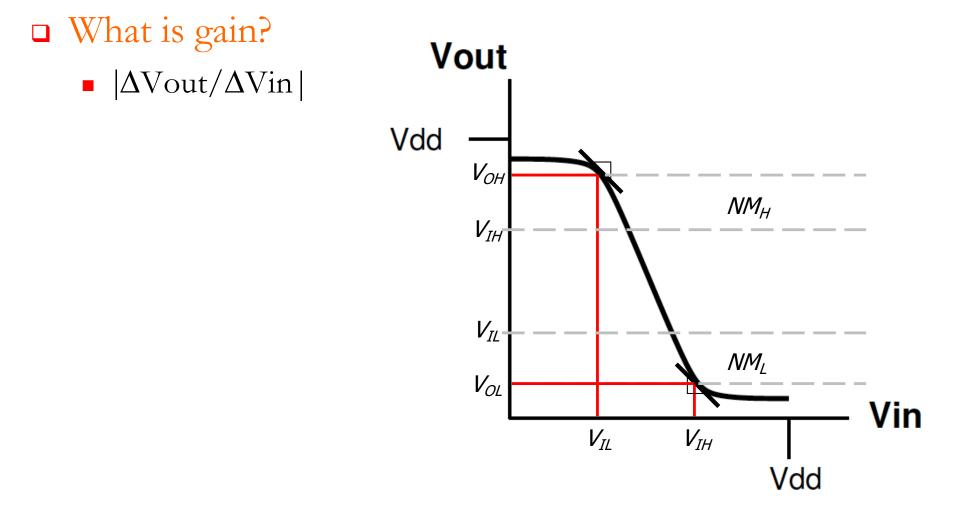

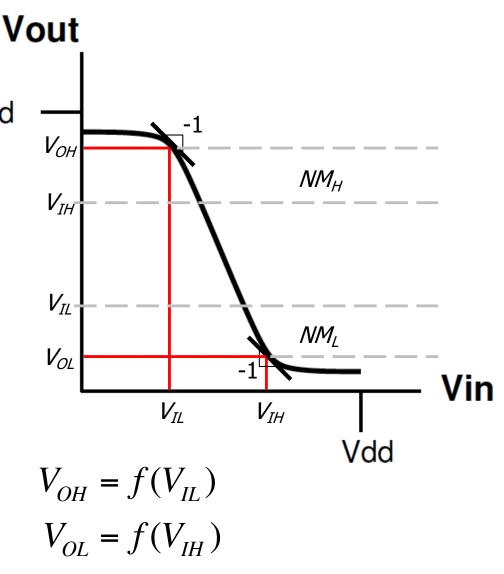

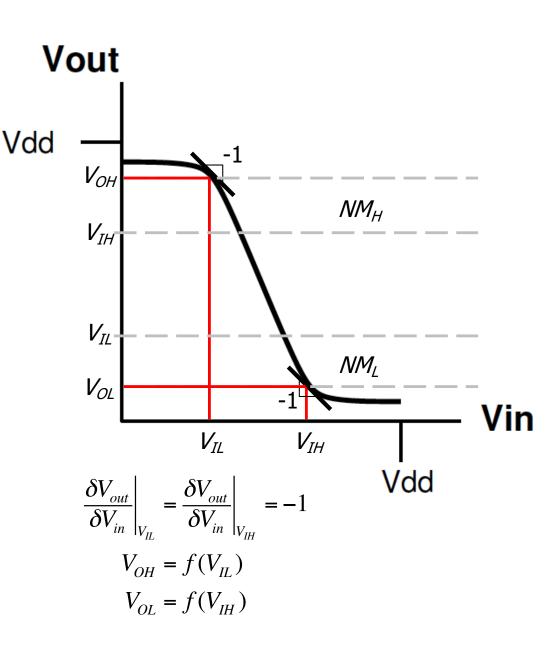

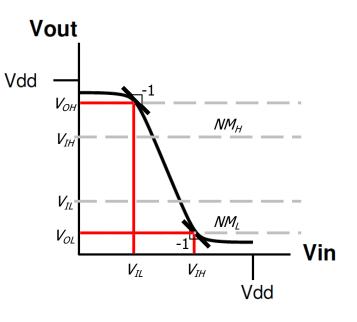

#### Use gain (i.e. slope) to define noise margins

#### Use gain (i.e. slope) to define noise margins

#### Use gain (i.e. slope) to define noise margins

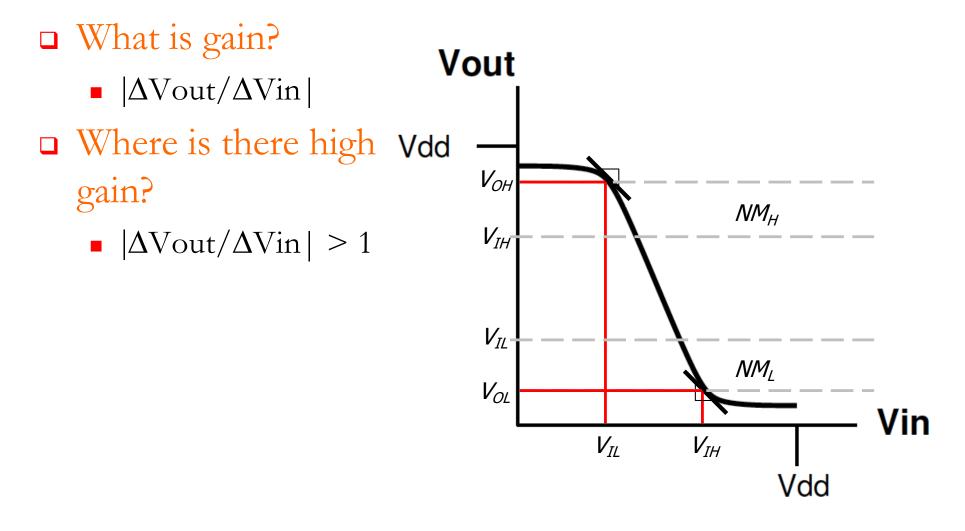

□ What is gain? Vout •  $|\Delta Vout/\Delta Vin|$ □ Where is there high Vdd  $V_{OH}$ gain?  $NM_{H}$  $V_{IH}$ •  $|\Delta \text{Vout}/\Delta \text{Vin}| > 1$ □ Where is there  $V_{IL}$ low gain?  $NM_L$ •  $|\Delta \text{Vout}/\Delta \text{Vin}| < 1$  $V_{OL}$ Vin  $V_{IL}$  $V_{IH}$ Vdd

- □ What is gain?

- |ΔVout/ΔVin|

- Where is there high Vdd gain?

- $|\Delta \text{Vout}/\Delta \text{Vin}| > 1$

- Where is there low gain?

- $|\Delta \text{Vout}/\Delta \text{Vin}| < 1$

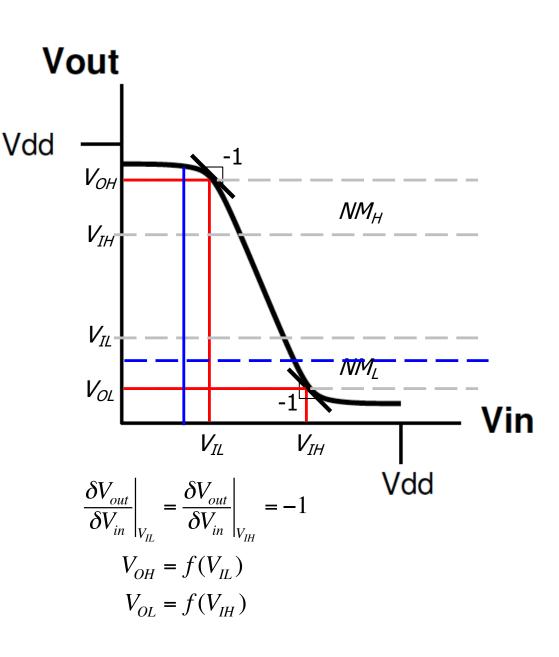

- Dividing point?

$$\frac{\delta V_{out}}{\delta V_{in}}\bigg|_{V_{IL}} = \frac{\delta V_{out}}{\delta V_{in}}\bigg|_{V_{IH}} = -1$$

- An input closer to rail than V<sub>IL</sub>, V<sub>IH</sub> doesn't make much difference on V<sub>out</sub>

- i.e transfer function is flat for input close to rails

- Defining V<sub>IL</sub> lower (or

V<sub>IH</sub> higher) would

reduce NMs and

increase our undefined

region

- An input closer to rail than V<sub>IL</sub>, V<sub>IH</sub> doesn't make much difference on V<sub>out</sub>

- i.e transfer function is flat for input close to rails

- Defining V<sub>IL</sub> lower (or

V<sub>IH</sub> higher) would

reduce NMs and

increase our undefined

region

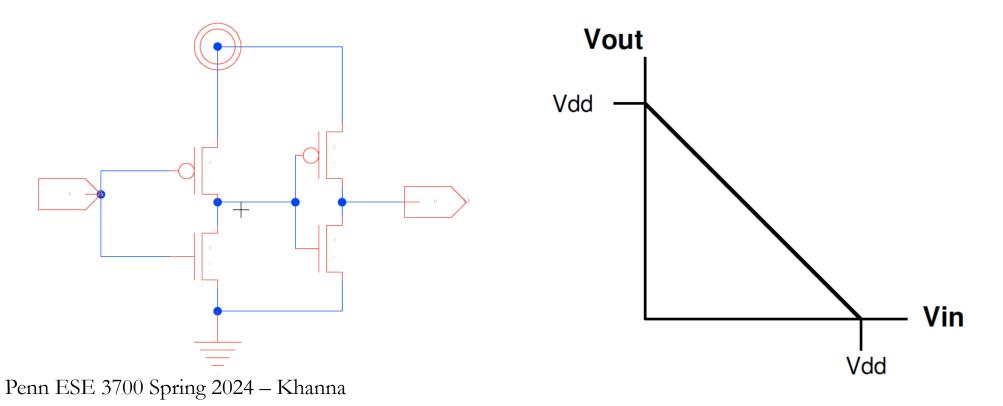

- Consider a nand2 gate

- If want A to control the output

- What value should B be?

- We call B the non-controlling input since it does not determine the output

- Consider a nand2 gate

- If want A to control the output

- What value should B be?

- We call B the non-controlling input since it does not determine the output

| А | В | NAND |

|---|---|------|

| 0 | 0 | 1    |

| 0 | 1 | 1    |

| 1 | 0 | 1    |

| 1 | 1 | 0    |

### Controlling Input

- Consider a nand2 gate

- If want A to control the output

- What value should B be?

- We call B the non-controlling input since it does not determine the output

- What should the non-controlling input value be for a nor2 gate?

|                             | А     | В | NOR |   | А | В | NAND |

|-----------------------------|-------|---|-----|---|---|---|------|

| -                           | 0     | 0 | 1   | - | 0 | 0 | 1    |

|                             | 0     | 1 | 0   |   | 0 | 1 | 1    |

|                             | 1     | 0 | 0   |   | 1 | 0 | 1    |

|                             | 1     | 1 | 0   |   | 1 | 1 | 0    |

| Penn ESE 3700 Spring 2024 - | Khann | a | l   |   |   |   |      |

## Controlling Input for Worst Case

- □ Consider a nor2/nand2 gate

- If want A to control the output

- What value should B be?

$$\Box$$

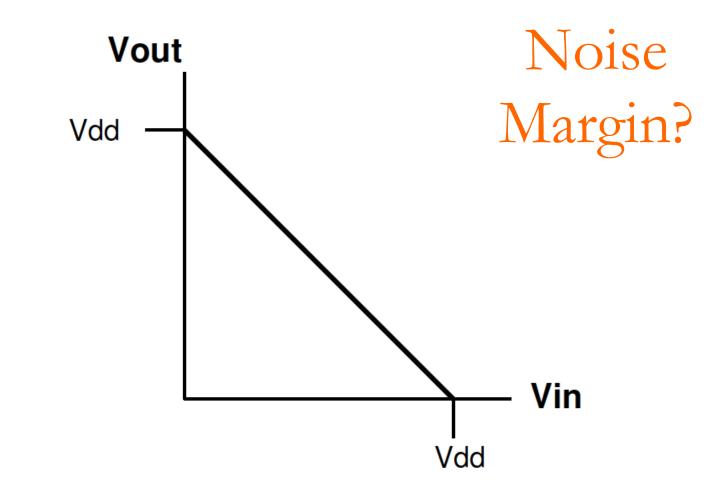

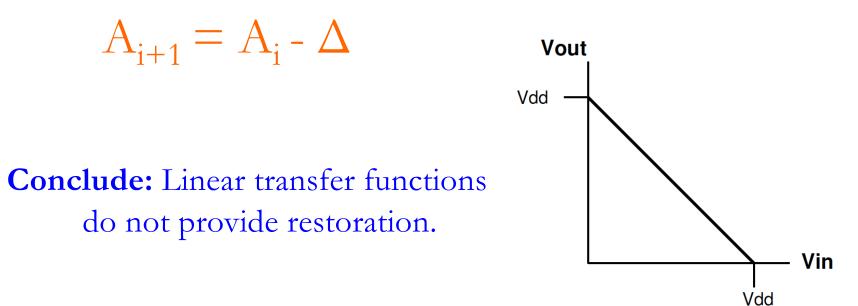

V<sub>out</sub>=V<sub>dd</sub>-V<sub>in</sub>

### Linear Transfer Function?

• Consider two in a row (buffer)

•

$$V_{out1} = V_{dd} - V_{in1}$$

$\Box$  What is transfer function to buffer output V<sub>out2</sub>?

•

$$V_{out2} = V_{dd} - V_{in2} = V_{dd} - V_{out1} = V_{dd} - (V_{dd} - V_{in1}) = V_{in1}$$

### Linear Transfer Function?

- For buffer:  $V_{out2} = V_{in1}$

- Consider a chain of buffers

- What happens if V<sub>in1</sub> drops ∆ volts between each buffer?

- **Need** non-linearity in transfer function

- Could not have built restoring gates with R, L, C circuit

- R, L, C are all linear elements

- If we hope to assemble design from collection of gates,

- Voltage levels must be consistent and supported across all gates

- Must adhere to a V<sub>IL</sub>, V<sub>IH</sub>, V<sub>OL</sub>, V<sub>OH</sub> that is valid across entire gate set of digital circuit

$V_{ol} = MAX(g.V_{ol})$  $g \in G$  $V_{oh} = MIN(g.V_{oh})$  $g \in G$

$V_{il} = MIN(gN_{il})$  $g \in G$  $V_{ih} = MAX(gV_{ih})$  $g \in G$

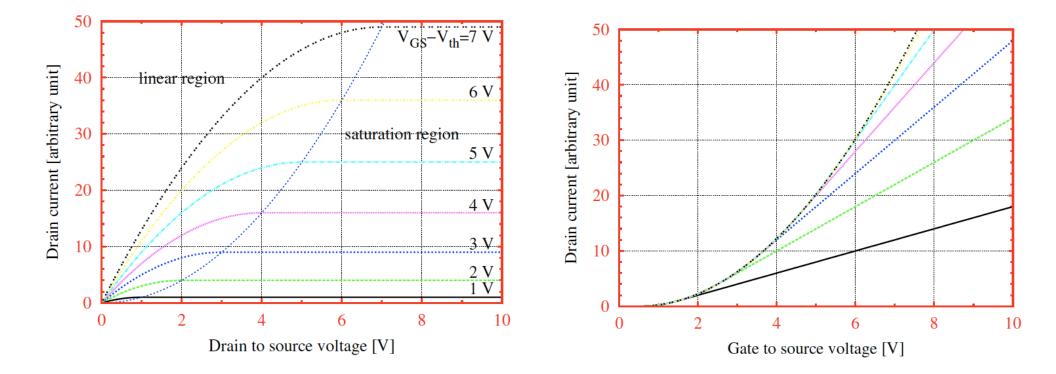

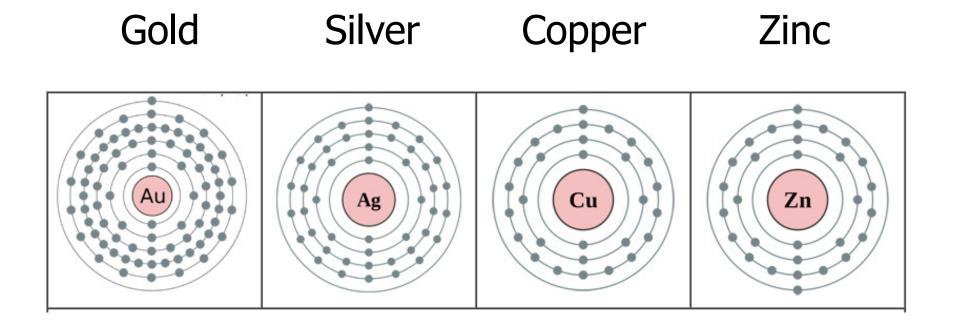

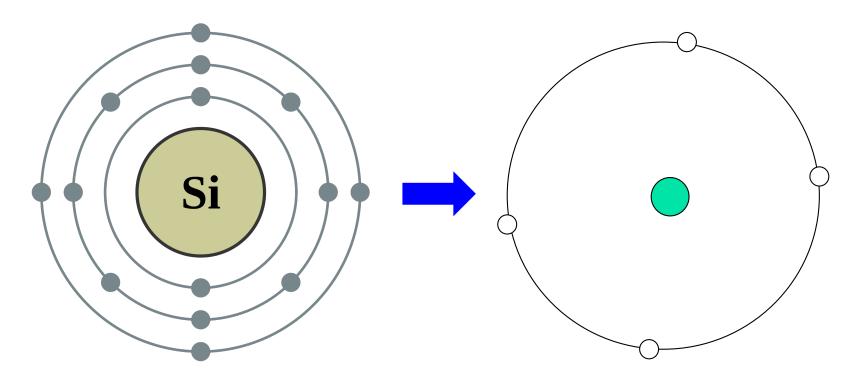

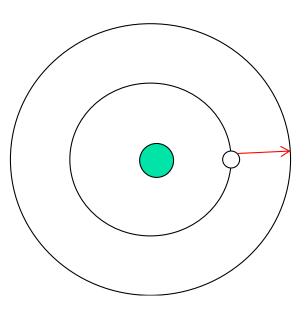

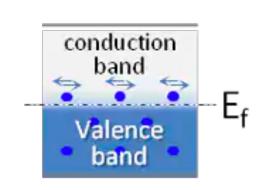

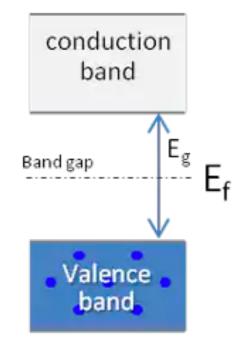

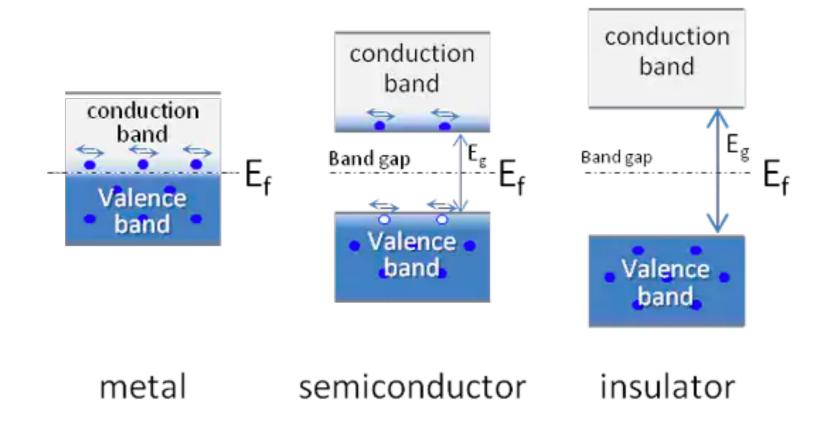

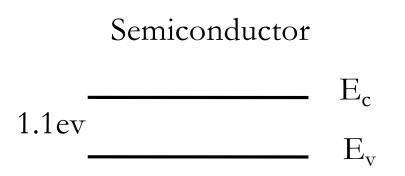

### Semiconductor Physics

- Metal conducts

- Insulator does not conduct

- □ Semiconductor can act as either

- Quantized Energy Levels (bands)

- Valence and Conduction Bands

- □ Must have enough energy to change level (state)

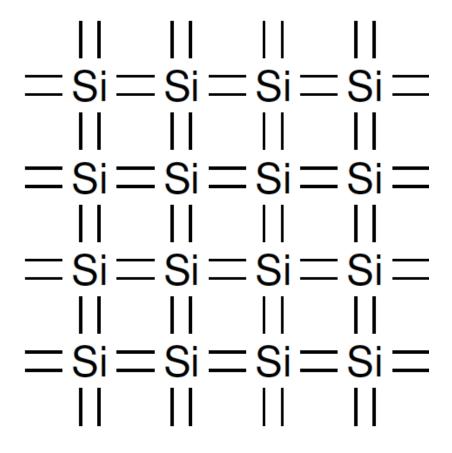

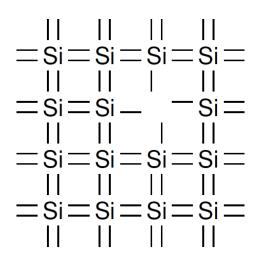

- □ 4 valence electrons

- Inner shells filled

- Only outer shells contribute to chemical interactions

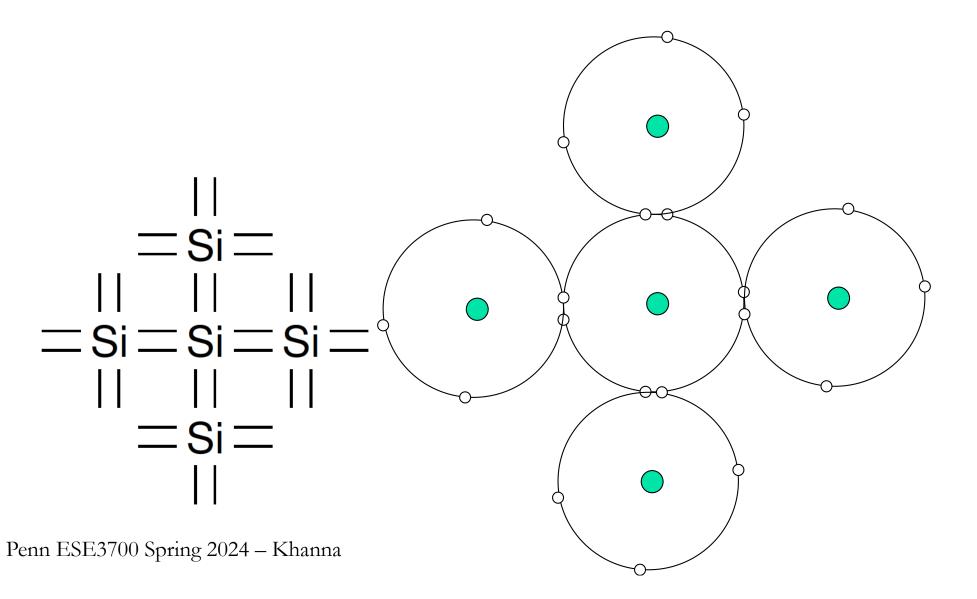

□ Can form covalent bonds with 4 other silicon atoms

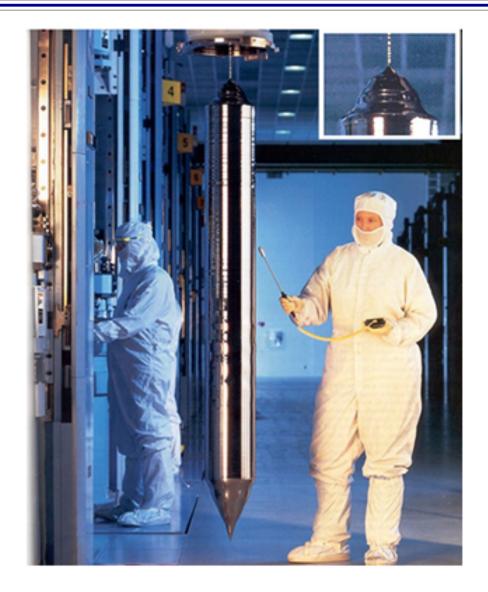

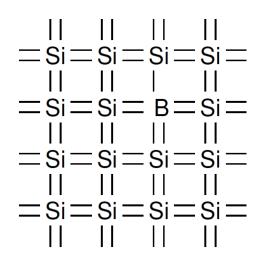

### 1 impurity atom per 10 billion silicon atoms

□ Cartoon two-dimensional view

□ What does this say about energy to move electron?

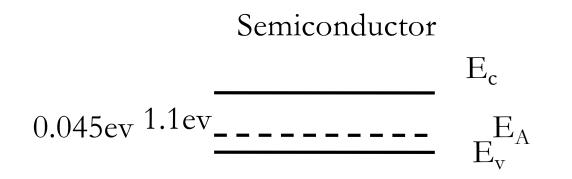

#### Conduction Band- all states empty

Band Gap

Valance Band – all states filled

Penn ESE3700 Spring 2024 - Khanna

Energy

metal

insulator

## Band Gap and Conduction

#### $1eV = 160 \text{ zeptojoules } (10^{-21} \text{ J})$

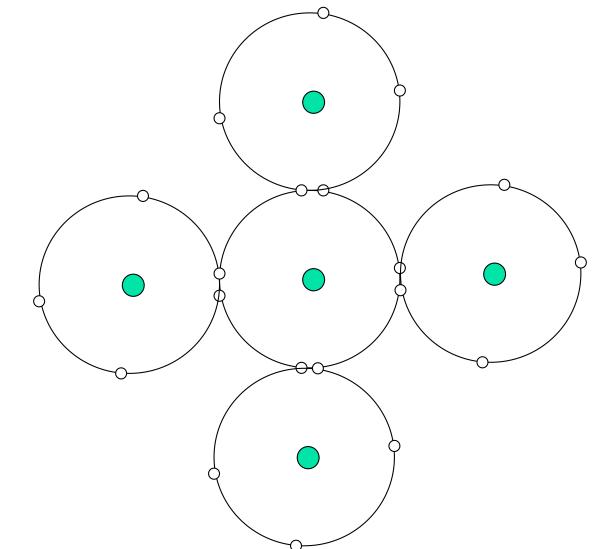

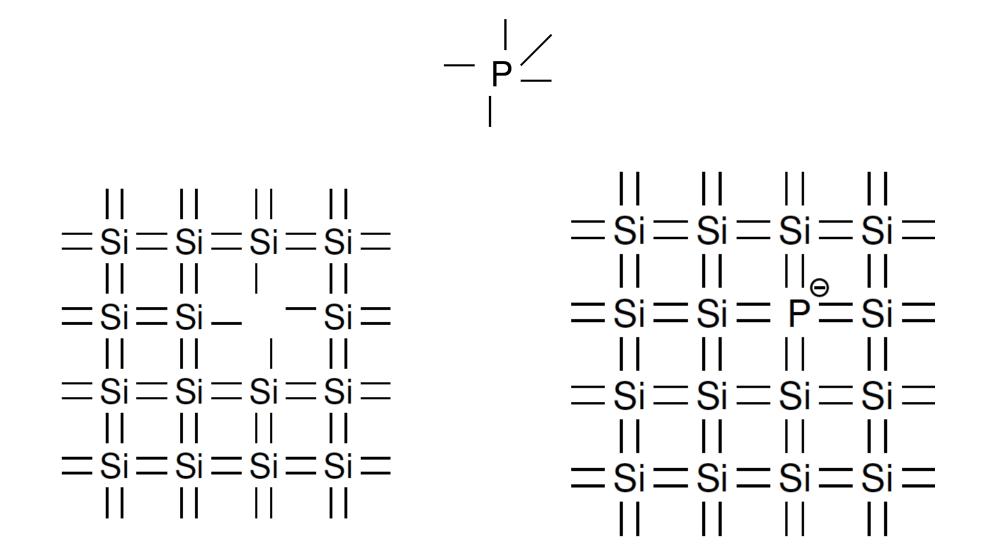

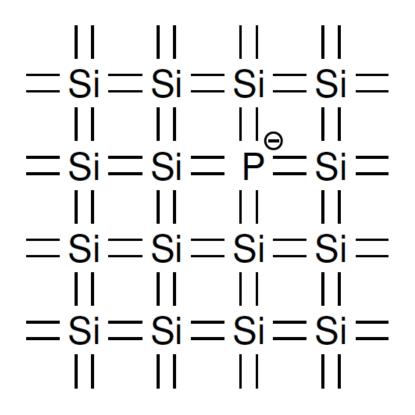

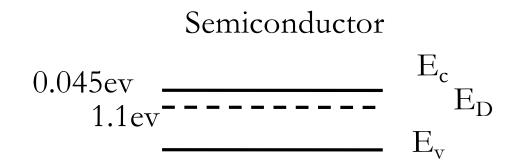

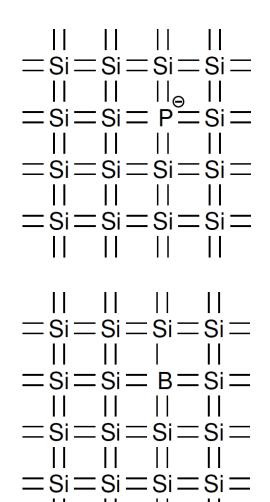

- Add impurities to Silicon Lattice

- Replace a Si atom at a lattice site with another

- □ Add a Group 15 element

- E.g. P (Phosphorus)

- How many valence electrons?

- End up with extra electrons

- Donor electrons

- Not tightly bound to atom

- Low energy to displace

- Easy for these electrons to move

□ Addition of donor electrons makes more metallic

Easier to conduct

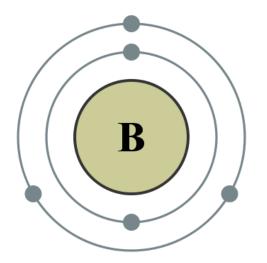

- What happens if we replace Si atoms with group 13 atom instead?

- E.g. B (Boron)

- Valance band electrons?

- □ End up with electron vacancies -- Holes

- Acceptor electron sites

- Easy for electrons to shift into these sites

- Low energy to displace

- Easy for the electrons to move

- Movement of an electron best viewed as movement of hole

• Addition of acceptor sites makes more metallic

Easier to conduct

- Donor doping

- Excess electrons

- Negative or N-type material

- NFET

- Acceptor doping

- Excess holes

- Positive or P-type material

- PFET

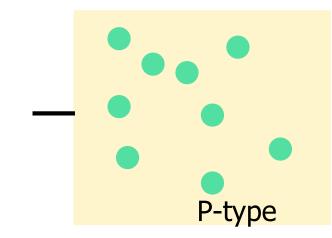

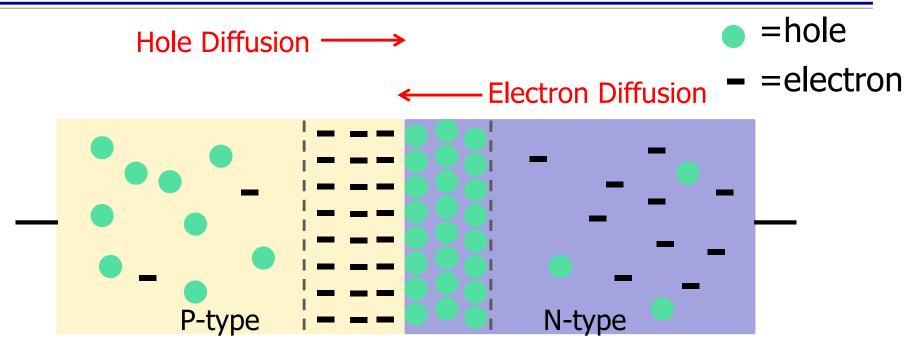

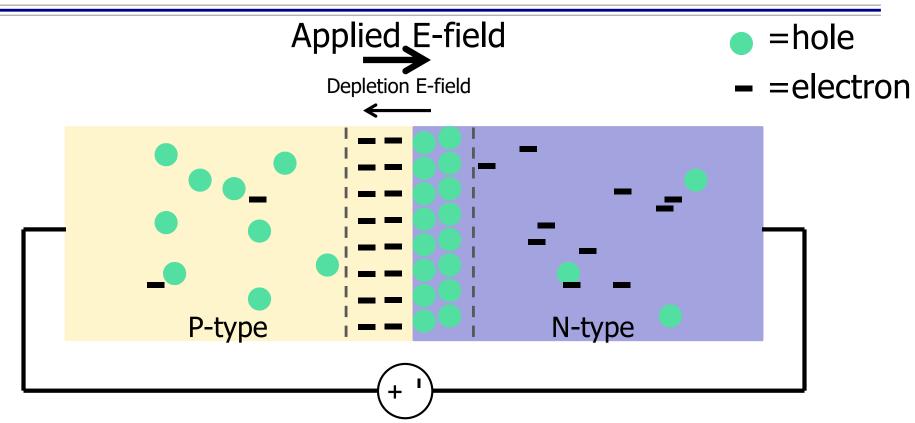

### PN Junction

=hole

– =electron

### Excess holes

Excess electrons

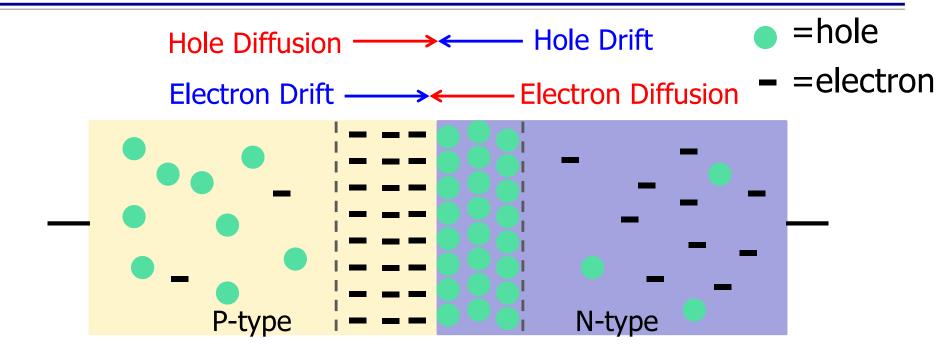

- PN junction causes a depletion region to form

- Electrons diffuse from N-type to P-type

- Holes diffuse from P-type to N-type

- Diffusion current caused by diffusion of carriers

- PN junction causes a depletion region to form

- Electrons diffuse from N-type to P-type

- Holes diffuse from P-type to N-type

- Diffusion current caused by diffusion of carriers

- Equilibrium achieved when  $V_{bi}$ , built-in potential, is formed across the depletion region

- Drift current cause by E-field due to V<sub>bi</sub> to counteract diffusion current

# Drift/Diffusion Currents

- Diffusion current

- Current caused by semiconductor diffusion of holes and electrons

- Drift current

- Current due to movement of holes and electrons caused by force from potential difference induced e-field

- Forward biasing connect positive terminal to p-type and negative terminal to n-type

- Holes/electrons pushed towards depletion region, causing it to narrow

- The applied voltage e-field continues to narrow the depletion region (i.e reduce the depletion e-field)

- current flows through the device from p-type to n-type

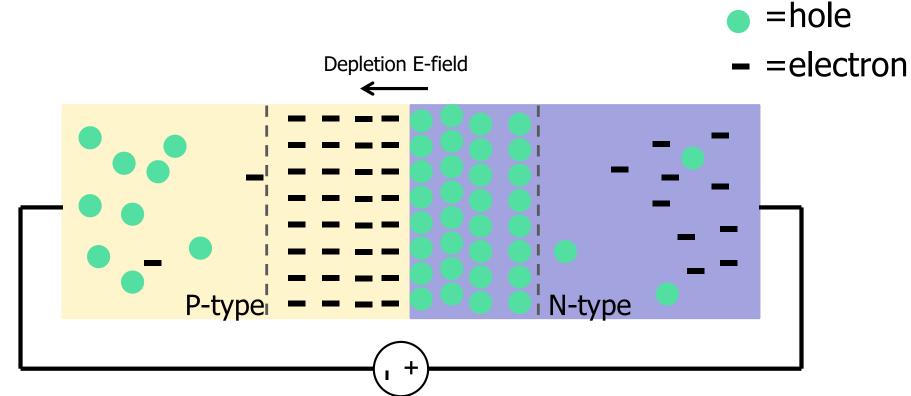

- Reverse biasing connect positive terminal to n-type and negative terminal to p-type

- Holes/electrons attracted away from depletion region, causing it to widen

- No current flows through the device

- If reverse bias increases past breakdown voltage, the depletion e-field increases until breakdown occurs and reverse biased current flows causing thermal damage to junction Penn ESE3700 Spring 2024 – Khanna

- Need robust logic

- Can design into any (feed forward) graph with logic gates and tolerate loss and noise, while maintaining digital abstraction

- **•** Regeneration and noise margins

- Every gate makes signal "better"

- Design level of noise tolerance

#### Homework 2 out now due Friday 2/9

- Will take time to install and learn ngspice

- START EARLY!!! For troubleshooting

- Use Ed discussion and office hours for technical difficulty questions

- Highly recommend you work in study groups/pairs for trouble shooting

- Tool guides/tutorials on course webpage for help

- <u>https://www.seas.upenn.edu/~ese3700/#tools</u>

- Get your design workflow set up now

- EVERYONE will be required to verify this on HW 3

- Prof. André DeHon (University of Pennsylvania)

- □ Prof. Jing Li (University of Pennsylvania)