Please work before lecture starts.

1. Consider a wire 1  $\mu$ m wide and 1  $\mu$ m tall with a resistivity  $\rho = 10^{-7}$ Ohm-m.

| What is the resistance of the 100 $\mu$ m long wire? |  |

|------------------------------------------------------|--|

| a 1 mm long wire?                                    |  |

| a 1cm long wire?                                     |  |

| How large is an Integrated Circuit chip (die)        |  |

| (e.g. your desktop or laptop processor)?             |  |

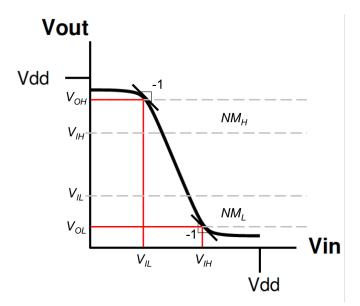

Regeneration/Restoration/Static Discipline:

$$NM_H = V_{OH} - V_{IH} \tag{1}$$

$$NM_L = V_{IL} - V_{OL} \tag{2}$$

As long as input(s) respect:  $V_{in} < V_{IL}$  or  $V_{in} > V_{IH}$ , output,  $V_{out}$ , will have:  $V_{out} < V_{OL}$  or  $V_{out} > V_{OH}$  Please work before lecture starts.

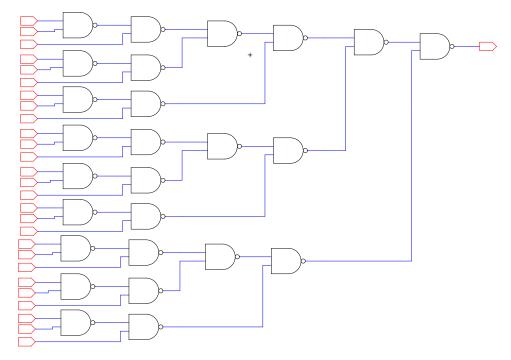

2. Consider the cascading gate structure below:

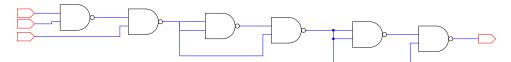

**Hint:** When inputs are equivalent, you can exploit symmetry to use the following simplified circuit for reasoning: (Convince yourself these are equivalent.)

| What is the digital output assuming ideal NAND gates and         |  |

|------------------------------------------------------------------|--|

| all inputs are logical 1?                                        |  |

| What is the output assuming all inputs are 1.0 and each          |  |

| NAND gate computes the real-valued function NAND(A,              |  |

| B)= $(1.0 - (A \times B))$ where A, B are the real-valued inputs |  |

| to the NAND2 gate and '-' and '×' are the real-valued math-      |  |

| ematical operators. Use table below for intermediary out-        |  |

| puts.                                                            |  |

| What is the output assuming all inputs are 0.95 and each         |  |

| nand gate computes NAND(A, B)= $(1.0-A \times B)$ [same as-      |  |

| sumptions as above and table below].                             |  |

Hint: When inputs are at 0.95, output of first NAND2 gate is:  $1.0 - (0.95)^2 \approx 0.1$ .

|       | Value after $i$ -th NAND2 gate |   |   |   |   |   |  |

|-------|--------------------------------|---|---|---|---|---|--|

| input | 1                              | 2 | 3 | 4 | 5 | 6 |  |

| 1.0   |                                |   |   |   |   |   |  |

| 0.95  | 0.1                            |   |   |   |   |   |  |