## Real-Time Tasks

- What timing guarantees might you like for the following tasks?

- Turn steering wheel on a drive-by-wire car

Delay to recognized and car turns

- Self-driving car detects an object in its path

Delay from object appearing to detection

- Pacemaker stimulates your heart

- Video playback (frame to frame delay)

## enn ESE5320 Fall 2022 -- DeHon

- Produce new frame every 30 ms

- Both: schedule to act and complete action

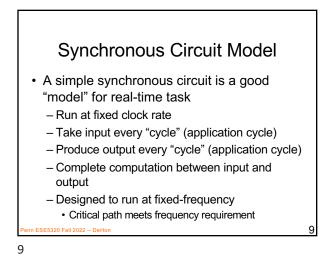

- · Bounded response time

- Respond to keypress within 20 ms

- Detect object within 100 ms

- Return search results within 200 ms

enn ESE5320 Fall 2022 -- DeHon

5

3

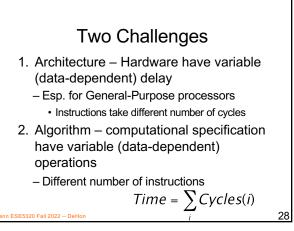

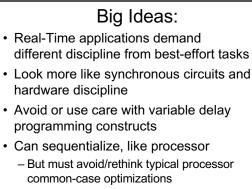

What can we do

to make architecture more

deterministic?

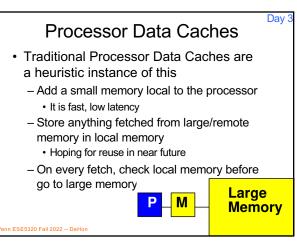

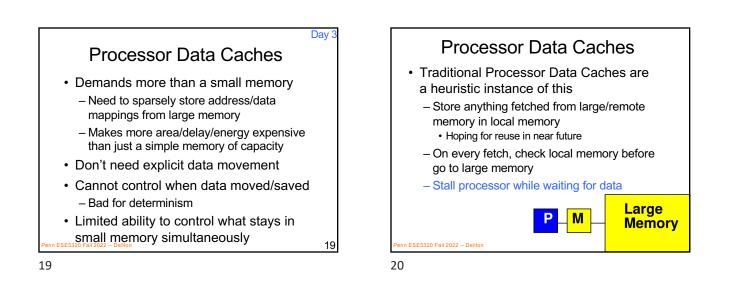

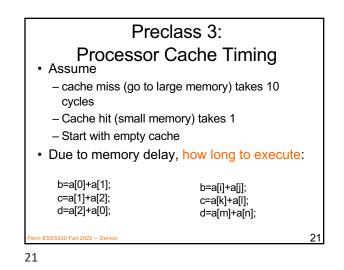

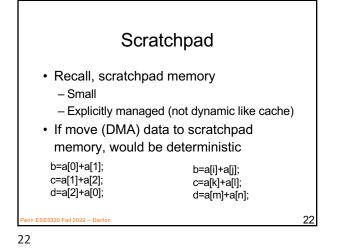

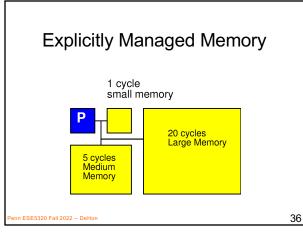

• Explicitly managed memory

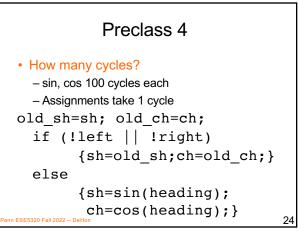

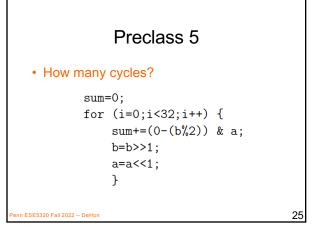

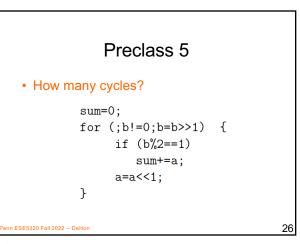

• Eliminate Branching (too severe?)

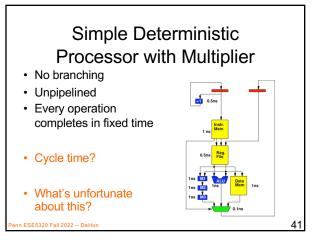

• Unpipelined processors

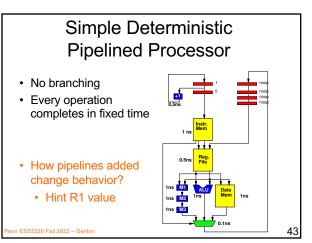

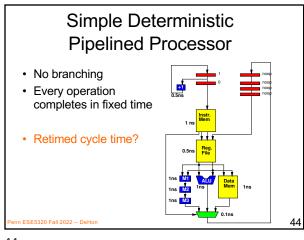

• Fixed-delay pipelines

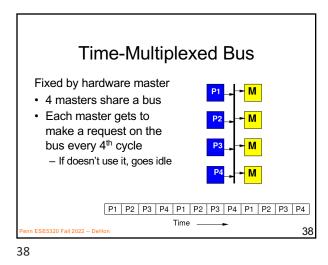

• Offline-scheduled resource sharing

• Multi-threaded

• Deadlines

34

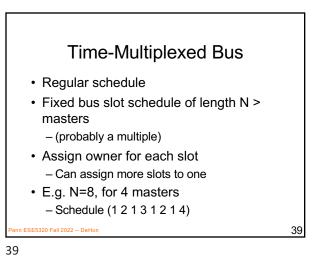

- Don't arbitrate

- Decide up-front when each shared resource can be used by each thread or processor

- Simple fixed schedule

- Detailed Schedule

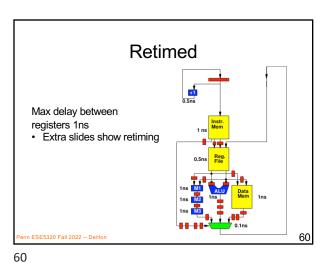

Simple Deterministic Processor with some Pipelining

No branching

Every operation completes in fixed time

Retimed cycle time?

Hint what are cycles?

How pipelines added change behavior?

Hint: what is sequence of addresses into Instr. Mem?

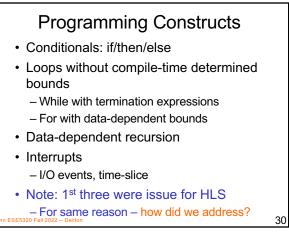

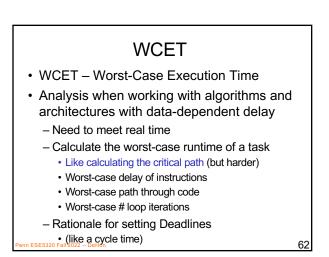

- Deal with algorithmic (branching) variability

- Set a hardware counter for thread

- · Decrement counter on each cycle

- Demand counter reach 0 before thread allowed to continue at deadline instruction

- · Model: fixed rate of attention

- Stall if get there early

- Similar to flip-flop on a logic path

- Wait for clock edge to change or sample value

- Model: fixed execution time

61

62

61

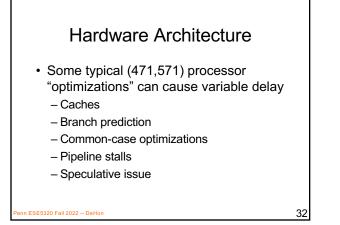

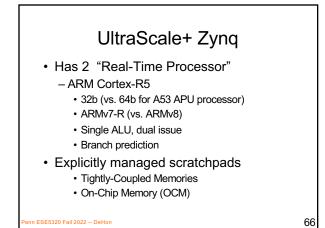

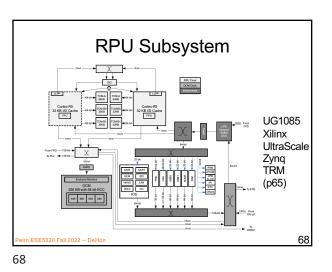

- Not how ARM, Intel (471, 571) processor are pipelined

- Those include operations that make timing variable

- dynamic data hazards, branch speculation

- Here, data becomes available after a predictable time

- Branches take effect at a fixed time

Likely delayed

- Schedule to delays to get correct data

66

Admin • Feedback • Reading for Wed. on web • Wolf Lecture Wednesday at 3pm - Tsu-Jae King Liu • Sustaining the Semiconductor Revolution • P4 due Friday