- · Harder than Boolean logic

- · Doesn't have unique canonical form

- Consider:

- state encoding not change behavior

- two "equivalent" FSMs may not even have the same number of states

- can deal with infinite (unbounded) input

- ...so cannot enumerate output in all cases

21

No direct correspondence of a truth table

n ESE534 Spring2010 -- DeHon

- · Possible?

- Finite state suggests there is a finite amount of checking required to verify behavior

In ESE534 Spring2010 -- DeHon

22

## Big Ideas [MSB Ideas]

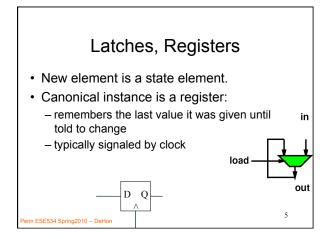

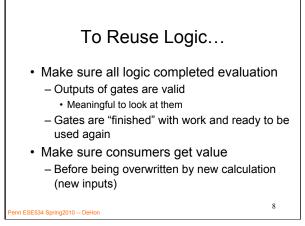

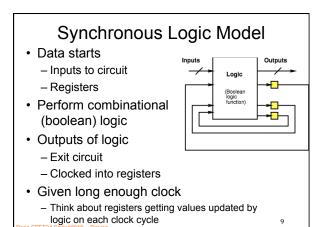

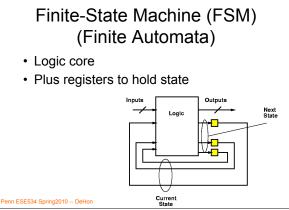

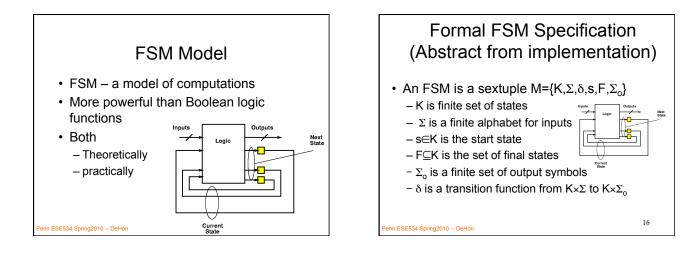

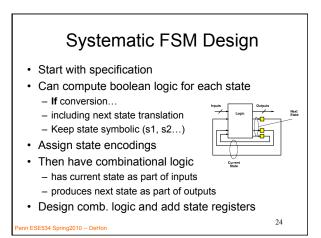

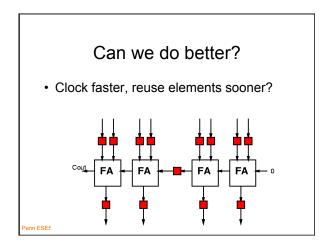

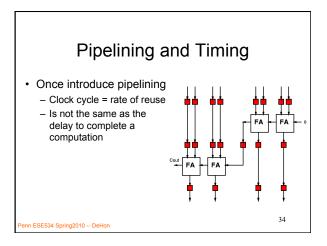

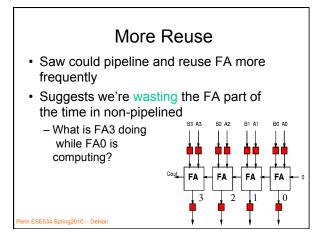

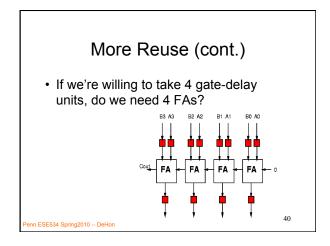

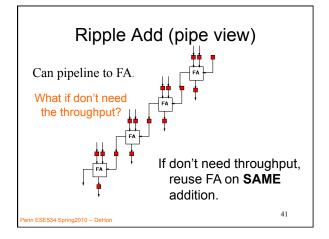

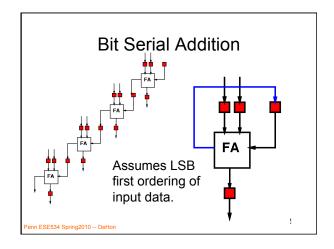

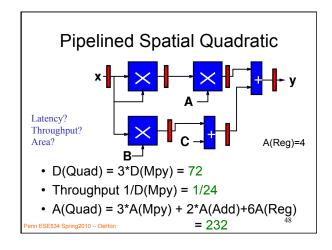

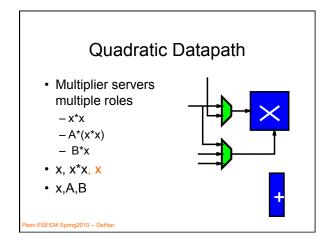

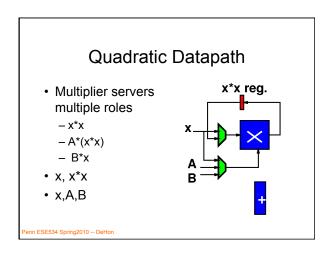

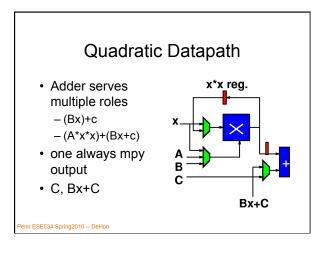

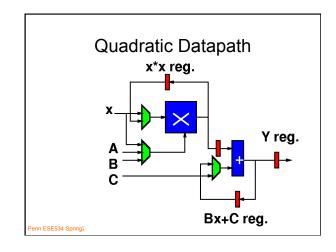

- Registers allow us to reuse logic

- Can implement any FSM with gates and registers

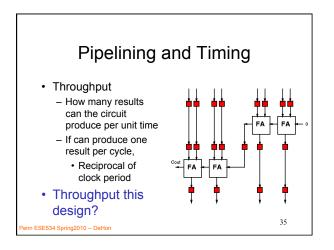

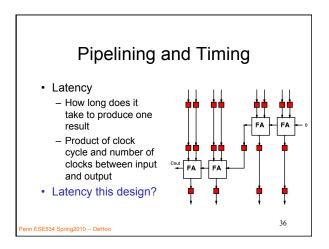

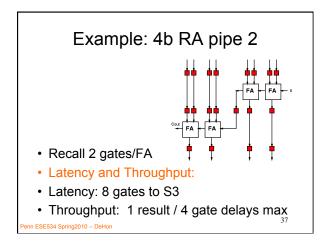

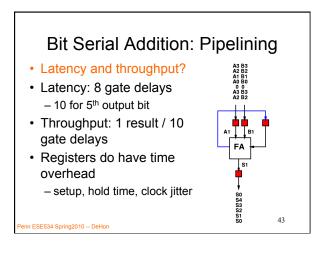

- Pipelining

- increases parallelism

- allows reuse in time (same function)

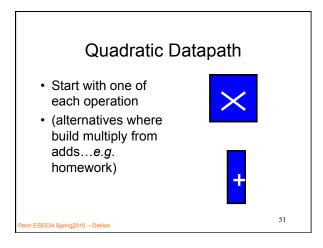

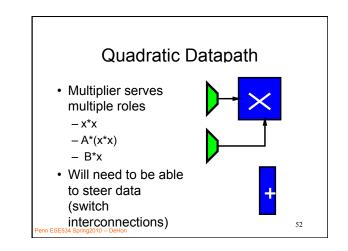

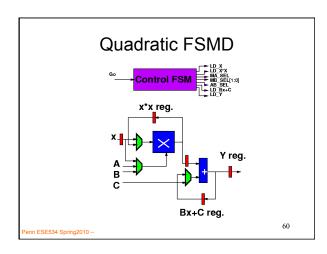

- Control and Sequencing

- reuse in time for different functions

65

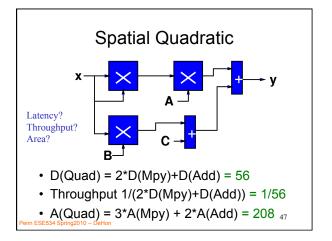

Can tradeoff Area and Time

## Penn ESE534 Spring2010 -- DeHon

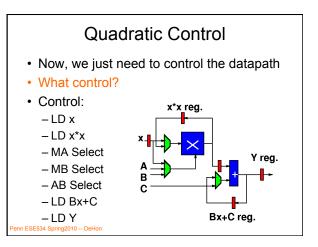

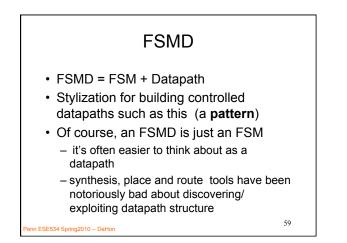

Big Ideas [MSB-1 Ideas] • RTL specification • FSMD idiom