#### **Combinational Logic** Introduction to Computer Systems, Fall 2022

**Instructor:** Travis McGaha

#### TAs:

Ali Krema Audrey Yang David LuoZhang Heyi Liu Katherine Wang Noam Elul Ria Sharma Andrew Rigas Craig Lee Eddy Yang Janavi Chadha Kyrie Dowling Patricia Agnes Sarah Luthra Anisha Bhatia Daniel Duan Ernest Ng Jason Hom Mohamed Abaker Patrick Kehinde Jr. Sofia Mouchtaris When poll is active, respond at **pollev.com/tqm**

📧 Text TQM to 37607 once to join

# How Many CU's are you taking? (including this class)

- 6 or more

- 5 or 5.5

- 4 or 4.5

- 3 or 3.5

- 2 or 2.5

- less than 2

Start the presentation to see live content. For screen share software, share the entire screen. Get help at pollev.com/app

# Logistics

- HW01 bits.c: This Friday 9/16 @ 11:59 pm

- Will require VM setup

- Has you "program" in C

- Should have everything you need

- Terminal & starting demo in Recitations this week

- HW02 Combinational Logic: to be released this week

- Written Homework, submitted to gradescope

- NO EXTENSIONS OVER 72 HOURS

- Check-in01: Due Monday @ 4:59 pm

- Coming out soon

## **Lecture Outline**

#### Incrementor

- Adder & Subtracter

- Mux

- Multiplier & Others

# **Combinational Logic**

- Boolean functions where the output is a pure function of the inputs

- There is no "memory" or "stored state"

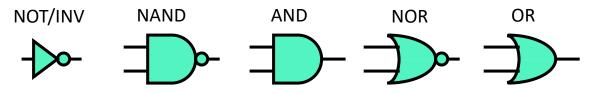

- ✤ So far, we have basic logic gates from last lecture:

- We can build more complex "gates" that we can use as building blocks for a processor

- This Lecture: start implementing binary arithmetic >:]

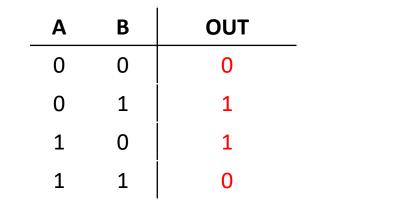

## Aside: XOR Gate

#### Performs the XOR operation

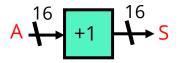

# **Creating an Incrementor**

- Let's create a 16-bit incrementor!

- Input: A (as a 16 bit 2C integer)

- Output: S = A + 1 (as a 16-bit 2C integer)

- Ignore the overflow case for now

- Theoretical Approach:

- Use a PLA-like technique to implement the circuit

- Problem: 2<sup>16</sup> or 65536 different inputs, 16-bit output

- This is impractical

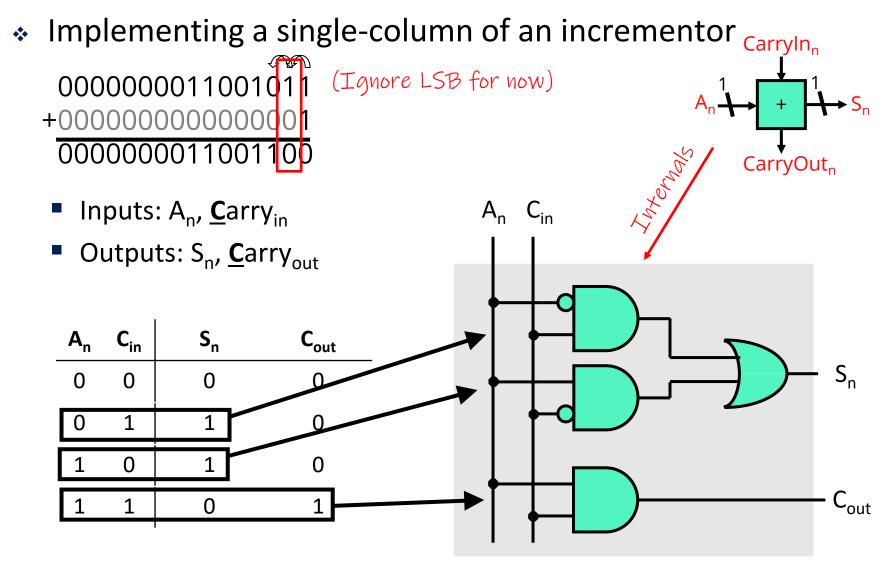

# **One Bit Incrementor "PLA"**

pollev.com/tqm

\* Which of the follow is an equivalent expression for  $S_n$ ?

| Α. | (A <sub>n</sub> & ~C <sub>in</sub> ) & (~A <sub>n</sub> & C <sub>in</sub> ) | A <sub>n</sub> | C <sub>in</sub> | S <sub>n</sub> |

|----|-----------------------------------------------------------------------------|----------------|-----------------|----------------|

| В. | (A <sub>n</sub>   ~C <sub>in</sub> ) & (~A <sub>n</sub>   C <sub>in</sub> ) | 0              | 0               | 0<br>1         |

|    |                                                                             | 0              | 1               | 1              |

| С. | ~(C <sub>in</sub> ^ A <sub>n</sub> )                                        | 1              | 0               | 1              |

| D. | A <sub>n</sub> ^ C <sub>in</sub>                                            | 1              | 1               | 1<br>0         |

E. I'm not sure

pollev.com/tqm

\* Which of the follow is an equivalent expression for  $S_n$ ?

| Α. | (A <sub>n</sub> & ~C <sub>in</sub> ) & (~A <sub>n</sub> & C <sub>in</sub> ) |  | A <sub>n</sub> | C <sub>in</sub> | S <sub>n</sub> |

|----|-----------------------------------------------------------------------------|--|----------------|-----------------|----------------|

| В. | $(A_n   ~C_{in}) \& (~A_n   C_{in})$                                        |  |                | 0               |                |

|    |                                                                             |  |                |                 | 1              |

| С. | ~(C <sub>in</sub> ^ A <sub>n</sub> )                                        |  | 1              | 0               | 1              |

| D. | A <sub>n</sub> ^ C <sub>in</sub> ^ is xor                                   |  | 1              | 1               | 0              |

E. I'm not sure

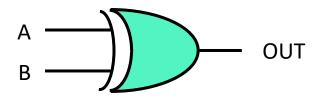

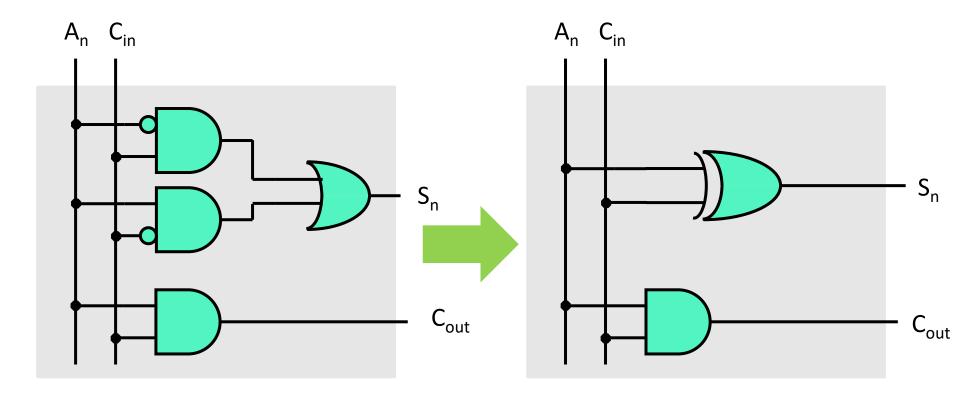

# **One Bit Incrementor Alternative**

Can implement with an XOR gate instead

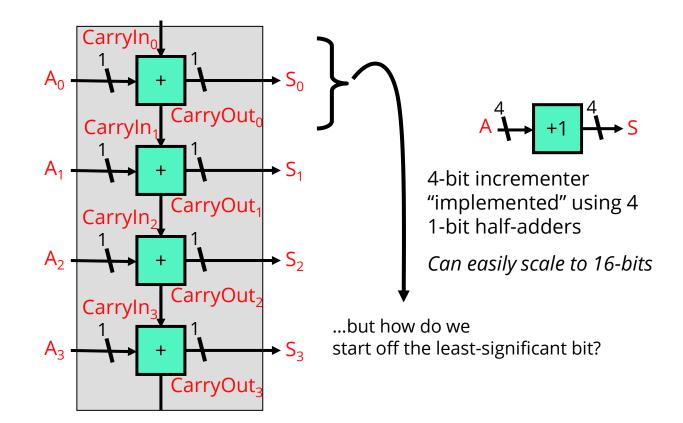

# **N-bit Incrementor**

- We can chain the 1-bit Incrementors together

- Carry-out for bit N, is Carry-in for bit N+1

- ✤ 4-bit Incrementor example:

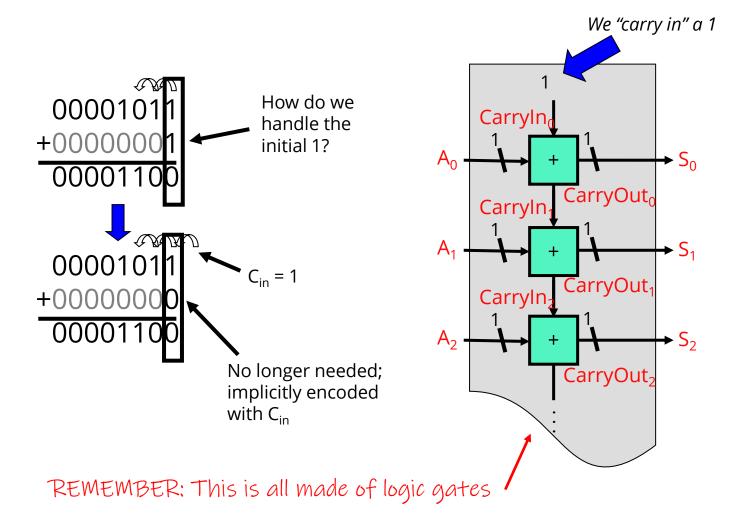

# **N-bit incrementor LSB**

How do we handle the Least significant bit?

## **Lecture Outline**

- Incrementor

- Adder & Subtracter

- Mux

- Multiplier & Others

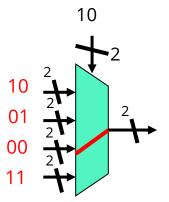

## Adder

- Similar to incrementor, but doesn't quite work:

- Incrementor only had to add 2 bits

- Works for the LSB, since there is no "carry in" for the LSB

- Bits other than the LSB may need to add two bits + carry in

Sum

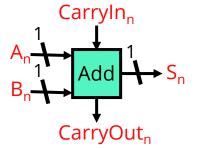

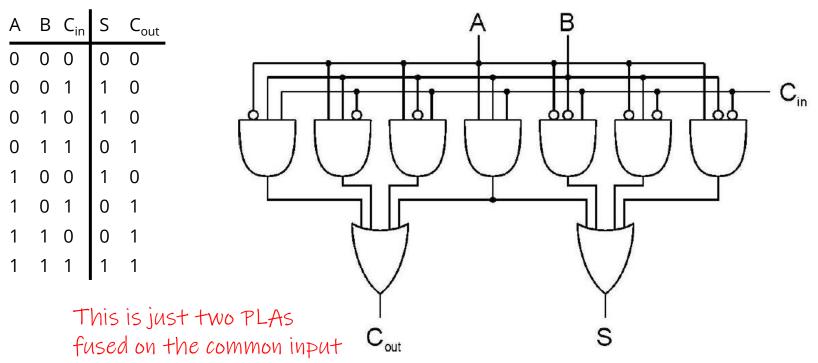

# **One-Bit Adder**

- Like incrementor, we will build a 1-bit component first

- Start from a truth table

- Create a PLA from it

Gate Level

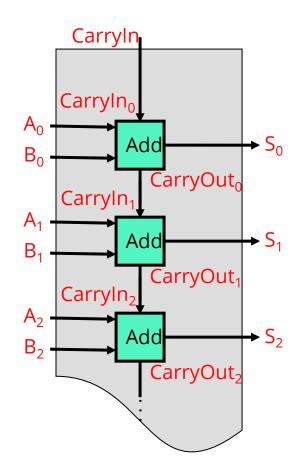

# **N-Bit Adder**

Abstraction  $A \xrightarrow{n} f \xrightarrow{n} f$

CarryOut: useful for detecting overflow

CarryIn: assumed to be zero if not present

# **Aside: Efficiency**

#### Full Disclosure:

- Our adder: Ripple-carry adder

- No one really uses ripple-carry adders

- Why? way too slow

- Latency proportional to n

#### We can do better:

- Many ways to create adders with latency proportional to log<sub>2</sub>(n)

- In theory: constant latency (build a big PLA)

- In practice: too much hardware, too many high-degree gates

- "Constant factor" matters, too

- If you continue to CIS 471, you'll encounter "carry look ahead adders", more efficient architecture

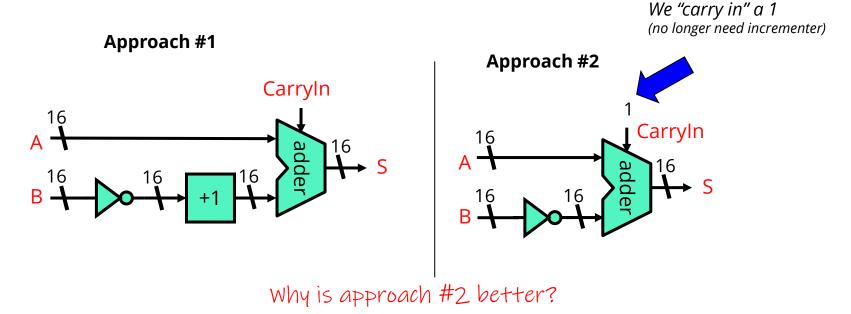

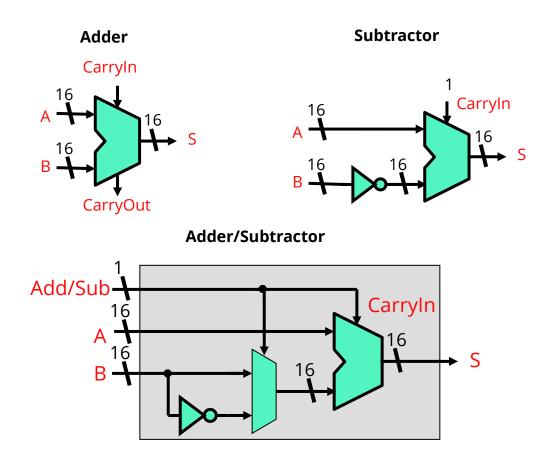

# **Subtractor**

- Build a subtractor from an adder

- Calculate A B = A + –B

- Negate B

- Recall –B = NOT(B) + 1

Can we combine this with the adder?

## **Lecture Outline**

- Incrementor

- Adder & Subtracter

- \* Mux

- Multiplier & Others

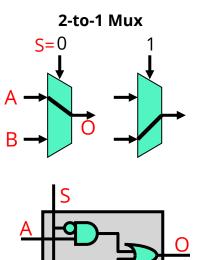

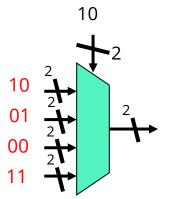

# **The Multiplexer**

- Selector/Chooser of signals

- Shorthand: "Mux"

B

Input "S" *selects* A or B to attach to "O" *output* Acts like an "IF/ELSE" statement

Note: selector bits map all "O" to he top input, and increment each input "down"

If you don't want to follow this ordering, label your MUX in the HW

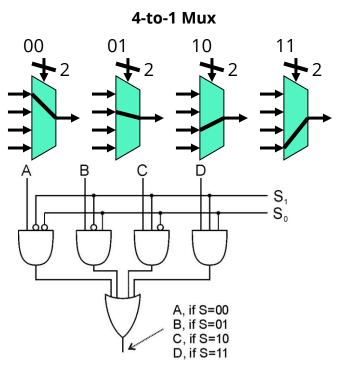

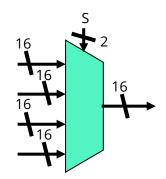

# **The Multiplexor In General**

#### In General

- N select bits chooses from 2<sup>N</sup> inputs

- An incredibly useful building block

- Multi-bit Muxes

- Can switch an entire "bus" or group of signals

- Switch n-bits with n muxes with the same select bits

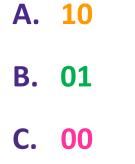

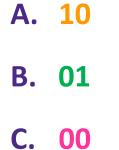

pollev.com/tqm

$\checkmark$  What is the output of the following mux with selector bits 10

D. 11

#### E. I'm not sure

pollev.com/tqm

$\, \ast \,$  What is the output of the following mux with selector bits 10

D. 11

# Adder/Subtractor - Approach #1

# **Adder/Subtractor - Approach #2**

## **Lecture Outline**

- Incrementor

- Adder & Subtracter

- Mux

- Multiplier & Others

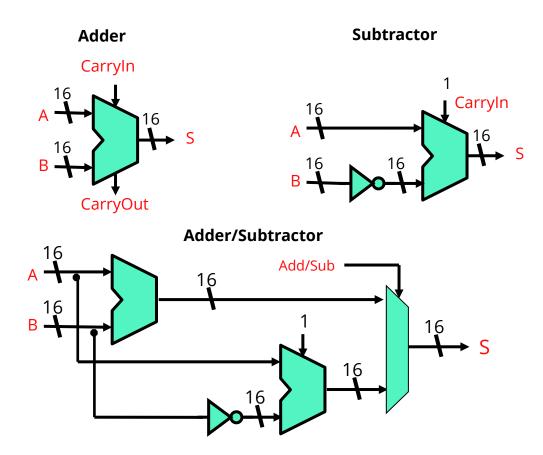

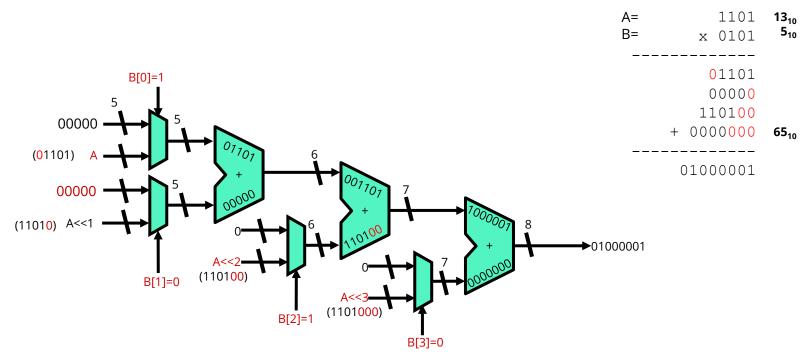

# **Creating a Multiplier**

- Combinational Multiplier using adders & muxes

- Let's build a 4-bit multiplier that makes an 8-bit product

- Recall: shifting is the same as multiplying by powers of 2

- Notation in this example: B[0], means LSB bit of B

# **Arithmetic Algos**

- Multiplication:

- More time efficient algos exist(Karatsuba and others)

- Divide/mod?

- Much harder than multiplication

- Most implementations are not combinational, but are sequential (more on sequential logic starting next lecture)

- Bitwise ops (AND, OR, XOR, ...)

- Easy

- Arbitrary left-right shift

- Can be done with just muxes (try it if you want!)