# **ECONOMIC TERMS**

× Production cost – expense to produce

ESE150 Spring 2019

ESE150 Spri

- Price what consume will pay for it + Value to consumer

- × Profit = Price cost

# OBSERVE

Creative / Intellectual work produces most of value

ESE150 Spri

At least in volume, physical costs of reproduction is small part of product price

# PRECLASS CONTINUED

- \* Cost to photocopy 200 page book at \$0.05/page?

- \* Cost to scan book at 10page/minute?

- \* Cost to retype book (50 words/minute type)?

- \* Cost to perform a 10s copy onto flash drive?

- \* Cost of portion of flash drive used + \$8 for 16GB drive, 0.5MB file

# OBSERVE

With digital representation

+ Cost of "physical" reproduction trends to 0

# Past

- Much of value in physical construction of objects

- + Bridge, house, car, screwdriver

- \* Expensive to reproduce / copy

- Reproductions imperfect

5<sup>th</sup> generation analog recording

4<sup>th</sup> generation photocopy of text

- × Inherent barrier to making copies

- + Value to buying original

# **DIGITAL REPRESENTATION**

- Can represent perfectly in bits + Including sound, words

- × Can make perfect copies

- Bits are cheap...and getting cheaper + Copying "free"

- Intellectual value disconnected from physical reproduction

# WHAT ELSE HAS THIS PROPERTY?

| Digital Intellectual Property | Physical IP Renderer         |

|-------------------------------|------------------------------|

| Novel                         | eReader                      |

| Song (MP3)                    | MP3 Player                   |

| JPEG Photo                    |                              |

|                               | Video Player                 |

| Video Game                    |                              |

|                               | Arduino or Personal Computer |

| Verilog digital circuit       |                              |

|                               | Web Server                   |

| STL (3D CAD drawing)          |                              |

| DNA Sequence                  | DNA Printer                  |

|                               |                              |

# INTELLECTUAL PROPERTY

- × Intangible creations of human intellect

- × Have value

- Don't necessarily have physical embodiment on their own

# INTELLECTUAL PROPERTY CREATORS

- × As Engineers

- + Program, develop algorithms, design circuits

- Almost everything we create will have this property

- + Value added is intellectual

- + Can be represented digitally in bits

- + Can (increasingly) be copied/reproduced cheaply

- \* Easy to have impact

- + Our solutions can reach millions, billions

- + Decreasing physical barriers to propagation of solutions

- Challenge to protect and reward IP creators

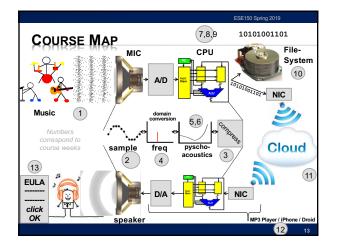

# OUTLINE

- × Setup Need / Opportunity What is IP

- × Where are we

- \* Rationale for IP Protection Why Protect

- How protect?

- + Patents

- CopyrightsOpen Source

- + NDA

- + Licensing

- + Licensing

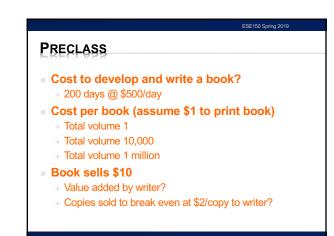

# **PRICING CHALLENGE**

- × When cost of copying  $\rightarrow 0$

- + Inventor/author must recover development cost × Price must include develop cost + copy cost

- Copier does not have development cost

- × Price = copy cost + epsilon

- $\times$  Competition of copiers will drive epsilon down near 0

- + Inventor/author not compensated for development × Remove incentive/reward for development

- Demand: developers need way to exclude others from copying to incentivize creation

# **ABROW'S INFORMATION PARADOX**

- \* Customer not know how to value information until see information (see details of product)

- Enough information to decide to buy

Enough information to decide what will pay for it

- Once show customer information, sufficient detail, they have enough information to reproduce + Could walk away and produce their own without paying for it

- Disclosure of what effectively transfers technology

- \* Demand: protection for developer

- Arrow, Kenneth J. Economic Welfare and the Allocation of Resources for Invention, in *The Rate and Direction of Inventive Activity*, 609 (Nat'l Bureau of Econ. Research ed. 1962).

# BALANCE INDIVIDUAL AND SOCIETAL GOOD

- \* Individual should benefit form their own effort

- Society advances with the accumulation of knowledge

# BEFORE COPYING WAS AN ISSUE

- Concern that new developments/ideas would be lost when inventor die

- + Techniques could remain secret for decades!

- Incentive to make inventions known

- Advance the general welfare

# **US CONSTITUTION**

# × Article 1, Section 8, Clause 8:

+ To promote the Progress of Science and useful Arts, by securing for limited Times to Authors and Inventors the exclusive Right to their respective Writings and Discoveries

# **MECHANISMS (TO SUPPORT)**

- × Patents

- + Cover inventions

- E.g., Flying Machine (US 821,393) ENIAC (US 3,120,606),

- × Copyrights

- + Creative expression

- + E.g., novel, song, movie

# **MECHANISMS FOR PROTECTION**

- \* Messy and imperfect

- × Haven't kept up with technology

- Likely need (and will need) innovation and refinement

SE150 So

INTERLUDE: NIL Nikolai Ivanovich Lobachevsky

# PATENT

- × Inventions

- \* Non-obvious to one "ordinary skill in art"

- \* Reduced to practice

- × Cannot patent

- + Abstract ideas

- + Laws of nature

- × US: First to file

- $\pm$  (prior to 2013 was first to invent)

- \* Exclusive rights 20 years from filing

# WHAT MIGHT BE TRICKY / NON-SATISFYING?

- \* First to file? (even invent?)

- × 20 year term?

# PATENT

## Identification of problem is part of invention

- × Claims

- Define the invention

- Technical coverage

- **Requires disclosure**

- If really believe no one else will figure it out...or can copy it, maybe better to keep as a trade secret

## License to litigate

- Recover damages is through litigation

- Establish violation

- Validity of many patents overturned in litigation

# **PATENT PROCESS**

- US have one year from first-public disclosure to file Many places - public disclosure prevent patent https://www.uspto.gov/web/offices/pac/mpep/s2153.html

- May file provisional patent to get filing date

- File patent with claims

- Reviewed by examiner

- Examiner reports on what may be allowable

- As-is

- With tighter qualifications Not-at-all

- On a per-claim basis

- Typically requires several iterations

- Often year(s) before patent issues

- Filing costs thousands of dollars

- With lawyer/legal fees tens to hundreds of thousands

#### (10) Patent No.: US 10,261,794 B2 (45) Date of Patent: Apr. 16, 2019 (12) United States Patent (54) TECHNIQUES FOR METADATA PROCESSING (56) References Cited U.S. PATENT DOCUMENTS (71) Applicant: The Charles Stark Draper Laboratory, Inc., Cambridge, MA (US) 5,201,056 A 4/1993 Daniel et al. 6,298,432 B1 10/2001 Goto (Continued) (72) Inventor: Andre' DeHon, Philadelphia, PA (US) FOREIGN PATENT DOCUMENTS (73) Assignce: The Charles Stark Draper Laboratory, Inc., Cambridge, MA (US) GB WO 2519608 A 4/2015 2010028316 A1 3/2010 (Continued) (\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days. OTHER PUBLICATIONS (21) Appl. No.: 15/695,541 Udit Dhawan, et al., "PUMP: A Programmable Unit for Metadata Processing. In Proceedings of the 3rd International Workshop on Hardware and Architectural Support for Security and Privacy", Jun. 2014. (22) Filed: Sep. 5, 2017 (65) Prior Publication Data US 2018/0011708 A1 Jan. 11, 2018 (Continued) Primary Examiner — Sharon S Lynch (74) Attorney, Agent, or Firm — Hamilton, Brook, Smith & Reynolds, P.C. Related U.S. Application Data (60) Division of application No. 15/426,098, filed on Feb. 7, 2017, now Pat. No. 9,785,440, which is a (Continued) (57)

(51) Int. Cl

ABSTRACT described for metadata processing that can ode an arbitrary number of security policies

## What is claimed is:

- 1. A method of processing computer instructions on a computer processor comprising:

- receiving a current instruction for metadata processing performed in a metadata processing domain that is isolated from a code execution domain including the current instruction;

- determining, by the metadata processing domain in con-nection with metadata for the current instruction, whether to allow execution of the current instruction in accordance with a set of one or more policies, wherein the one or more policies include a set of rules that enforce execution of a complete sequence of instructions in a specified order from a first instruction of the complete sequence to a last instruction of the complete sequence, the set of rules including a first rule and a second rule:

- performing metadata processing of the first rule for the first instruction, wherein the metadata processing of the first rule includes setting a program counter tag of a program counter used for a next instruction following runtime execution of the first instruction to a special tag value indicating that the next instruction is part of the complete sequence of instructions;

|                                                                                                                                                                                                                                                                                                                                     |             |                                                                                                                                                                                                                                                                                                                                                                                        |                                              | US005742180A                                                                                 |                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Un                                                                                                                                                                                                                                                                                                                                  | nited S     | States Patent [19]                                                                                                                                                                                                                                                                                                                                                                     | [11]                                         | Patent Number:                                                                               | 5,742,180                                                                                                                                   |

| DeHon et al.                                                                                                                                                                                                                                                                                                                        |             |                                                                                                                                                                                                                                                                                                                                                                                        | [45]                                         | Date of Patent:                                                                              | Apr. 21, 1998                                                                                                                               |

| <ul> <li>[54] DYNAMICALLY PROGRAMMABLE GATE<br/>ARRAY WITH MULTIPLE CONTEXTS</li> <li>[75] Inventors: André Delfon, Cambridge; Thomas F.<br/>Night, Jr., Beunon: Edward Tau,<br/>Boston; Michael Bolotski, Somerville;<br/>Ian Edick, Cambridge; Derrek, Chen,<br/>Cambridge; Jereny Brown,<br/>Cambridge; Jereny Brown,</li> </ul> |             | Denneau, M.M., "The Yorktown Simulation Engine," IEEE<br>19th Design Automation Conference, pp. 55-59 (1982).<br>Razdan, R., et al., "A High Performance Microarchitecture<br>with Hardware-Programmable Functional Utilit,"<br>Micro-27Proceedings of the 27th Annual International Sym-<br>posium on Microarchitecture, San Jone, Cullerinia, pp.<br>172–180 (Nov. 30-Dec. 2, 1994). |                                              |                                                                                              |                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                     |             |                                                                                                                                                                                                                                                                                                                                                                                        |                                              |                                                                                              |                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                     |             | [73]                                                                                                                                                                                                                                                                                                                                                                                   | Assignee:                                    | Massachusetts Institute of Technology, Cambridge, Mass.                                      | Primary Examiner—Edward P. Westin<br>Assistant Examiner—Jon Santamauro<br>Attorney, Agent, or Firm—Hamilton, Brook, Smith<br>Revnolds, P.C. |

| [21]                                                                                                                                                                                                                                                                                                                                | Appl. No.   | 386,851                                                                                                                                                                                                                                                                                                                                                                                | [57]                                         | ABSTRACT                                                                                     | r                                                                                                                                           |

| [22]                                                                                                                                                                                                                                                                                                                                | Filed:      | Feb. 10, 1995                                                                                                                                                                                                                                                                                                                                                                          | 1                                            |                                                                                              |                                                                                                                                             |

| [51]<br>[52]<br>[58]                                                                                                                                                                                                                                                                                                                | U.S. Cl     | H03K 19/177<br>326/40; 326/38<br>earch                                                                                                                                                                                                                                                                                                                                                 | These gates can be implemented as look up ta |                                                                                              | f programmable gates<br>as look up tables builde interconnections are<br>es receives plural input                                           |

| [56]                                                                                                                                                                                                                                                                                                                                |             | References Cited                                                                                                                                                                                                                                                                                                                                                                       | logic si                                     | nals from plural other gates                                                                 | s. Consequently, a broad                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                     | U           | S. PATENT DOCUMENTS                                                                                                                                                                                                                                                                                                                                                                    | include                                      | logic combinations are po-<br>locally stored multiple con                                    | texts dictating differen                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                     | 4.354.228 1 | 5/1982 Tanaka                                                                                                                                                                                                                                                                                                                                                                          | combin<br>context:                           | atorial logic operations perfo<br>increase the logic operations the fact that the contexts a | ormed by the gates. The<br>ons performable by the                                                                                           |

# We claim: 1. An integrated dynamically programmable logic array, comprising: at least a two dimensional array of programmable logic elements, each one of the logic elements receiving plural input logic signals from plural other logic elements and including locally stored multiple contexts dictating different combinatorial logic operations performed by the logic elements; and a context signal source that provides a context signal, indicating an active one of the contexts, commonly to the programmable logic elements are individually accessible so that a new context can be loaded into the logic elements. A programmable logic energy wherein the context signal source provides the context signal up to every cycle of the programmable logic elements. A programmable logic array as described in claim 1, wherein the context signal source generates plural context signals that dictate contexts for regions of the array of the logic array.

# WHAT'S PATENTABLE × Not law's of nature × Not abstract ideas

- × Cannot patent pi ( $\pi$ )

- × Software?

- + Originally not

- With reference to machine, can often manage

- » Genetic sequences?...

- × ...evolving...

| ESE150 Spring 2019              | ESE150 Spring 2019                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                 | EINOL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ARMINISTRATIXE INTERLURE: EINAL | <ul> <li>Final Office Hours:         <ul> <li>Saturday 6pm</li> <li>Sunday 4pm and 5pm</li> </ul> </li> <li>Final: Monday (5/6) 3-5pm in Moore 212         <ul> <li>Same Rules as midterm</li> <li>Calculators allowed (work that out in advance)</li> <li>Closed book, notes</li> <li>15% of grade</li> <li>Comprehensive</li> <li>Last year final and answers linked to Spring 2018 syllabus             <ul> <li>Probably mix ideas from first and second half</li> </ul> </li> </ul></li></ul> |

### **FINAL TOPICS** Pre Midterm Post midterm Combinational Logic Data representation in bits × Sounds waves Finite-State Machines \* Stored-Program Processors × Sampling COPYRIGHT × Quantization \* Processing Requirements \* Process Virtualization × Nyquist × Lossy/lossless compression \* Persistent Storage × Common case × File Systems Frequency domain × Networking Psychoacoustics User Interface Perceptual coding × Intellectual Property

# 6

# COPYRIGHT

- Cover particular, original expression

+ Including software

- Technically don't need to register + But should...

- + Must register before sue for infringement

- + \$35

- + No review, just registration

- × Life of author + 70 years

- × Work for hire: 95 years from publication

# TRADITIONALLY: TRANSFER COPYRIGHT ...

## · Publish in ACM, IEEE journal

Transfer copyright to them, they license you back rights for derived work and post on person web site.

Copyright (c) 1996 by the Association for Computing Machinery, Inc. Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that new copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Request Permissions from Publications Dept, ACM Inc., Fax +1 (212) 869-0481, or compermissions@acm.org>.

# RECENT: LICENSE TO ACM, IEEE

## × Author retain copyright, license to publisher

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than the author(s) must be honored. Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from permissions@acm.org.

FPGA '17, February 22 - 24, 2017, Monterey, CA, USA

© 2017 Copyright held by the owner/author(s). Publication rights licensed to ACM. ISBN 978-1-4503-4354-1/17/02...\$15.00

${\rm DOI: http://dx.doi.org/10.1145/3020078.3026124}$

# LICENSE

\* Where have you seen licenses?

# LICENSES

- How get right to use

+ Something patented, copyrighted by someone else

- Between companies

- Get IP need to build a product

- × To consumers

- + Technically, most software is licensed, not sold

- + ...shrink-wrap licensing agreements...

- Define terms of use

- + What you are paying for (one copy, many, resale...)

- What uses (dis)allowed

- Selling a product require huge infrastructure and up-front capital costs

- + Manufacture (physical things)

- Marketing

- + Distribution

- + Sales

× Examples?

\* Demand large business to support infrastructure

DIRECT IP BUSINESSES TODAY

× Not easy for individual

# TODAY (EMERGING)

# Eliminate infrastructure needs with ubiquitous networking, IP products, service businesses

- + Manufacture (physical things) → not issue for IP × ...or licensed manufacturing

- + Marketing → still need to get the word out

× ...can use web at low cost

- + Distribution → not an issue for IP × ...leverage common carriers

- × ....e + Sales

- × Handle online, eBusiness support

- Becomes possible for individuals/small businesses to sell IP directly to consumers

- businesses to sell IP directly to consumers

ESE150 Spring 201

# DIRECT IP BUSINESSES TODAY

- × Kindle Direct Publishing

- × App Store

- × AWS Marketplace

- × Café Press

- × Shapeways

**OPEN SOURCE / CREATIVE COMMONS**

# SHARING

# × Sometimes we want to share

- + Isn't it great doesn't cost us anything to give away digital products?

- + Isn't it great can build on work of others without necessary cost?

- + Cooperation on standards create opportunities for everyone, for an industry

# CHALLENGE

- \* Patents cost money

- Business (people making money) will spend money to patent things

- $\scriptstyle + \hdots$  ...and typically incentivized to patent everything they can

- Company (individual) could patent something and grant free license

- How does individual, non-profit, etc.

+ Create something and protect right to share?

- \* Variety of Open-Source/Public Domain licenses

NON-DISCLOSURE AGREEMENT (NDA)

# **CREATIVE COMMONS**

- Framework and set of licenses for clearly expressing intent

- × Issues

- + Attribution

- Share-Alike (Non-)commercial

()

(cc)

- (No)Derivatives

- Apps to choose, logos to show, legal backing to define precisely

- https://creativecommons.org/share-yourwork/licensing-types-examples/

# NDA

- × Tool for protecting IP

- Legal agreement that you won't disclose someone information shared with you

Prevent loss of IP

- **x** Typical for collaborating companies

- \* Typical for employers

- In part to make sure sharing with you doesn't count as "disclosure" to preclude patents

- × Define scope of disclosure

|                                    |                   |                                                                                                              |                                                                                                                                                                                                | US010261794B2                                             |  |

|------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--|

| (12) United States Patent<br>DeHon |                   |                                                                                                              | Patent No.: US 10,261,794 B2<br>Date of Patent: Apr. 16, 2019                                                                                                                                  |                                                           |  |

| (54)                               | TECHNIC<br>PROCES | QUES FOR METADATA<br>SING                                                                                    | (56)                                                                                                                                                                                           | References Cited<br>U.S. PATENT DOCUMENTS                 |  |

| (71)                               | Applicant:        | The Charles Stark Draper<br>Laboratory, Inc., Cambridge, MA (US)                                             |                                                                                                                                                                                                | 01,056 A 4/1993 Daniel et al.<br>98,432 B1 10/2001 Goto   |  |

| (72)                               | Inventor:         | Andre' DeHon, Philadelphia, PA (US)                                                                          |                                                                                                                                                                                                | (Continued)                                               |  |

| (73)                               | Assignee:         | The Charles Stark Draper<br>Laboratory, Inc., Cambridge, MA (US)                                             | GB                                                                                                                                                                                             | FOREIGN PATENT DOCUMENTS<br>2519608 A 4/2015              |  |

| (*)                                | Notice:           | Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days. |                                                                                                                                                                                                | 2010028316 A1 3/2010<br>(Continued)<br>OTHER PUBLICATIONS |  |

| (21)                               | Appl. No.:        | 15/695.541                                                                                                   | Lide Dhe                                                                                                                                                                                       |                                                           |  |

| (22)                               | Filed:            | Sep. 5, 2017                                                                                                 | Udit Dhawan, et al., "PUMP: A Programmable Unit for Metada<br>Processing. In Proceedings of the 3rd International Workshop<br>Hardware and Architectural Support for Security and Privacy", Ju |                                                           |  |

| (65)                               |                   | Prior Publication Data                                                                                       | 2014.                                                                                                                                                                                          | (Continued)                                               |  |

|                                    | US 2018/0         | 011708 A1 Jan. 11, 2018                                                                                      |                                                                                                                                                                                                |                                                           |  |

|                                    | Rel               | ated U.S. Application Data                                                                                   | Primary Examiner — Sharon S Lynch<br>(74) Attorney, Agent, or Firm — Hamilton, Brook, Smi                                                                                                      |                                                           |  |

| (60)                               |                   | f application No. 15/426,098, filed on Feb                                                                   | ,                                                                                                                                                                                              | olds, P.C.                                                |  |

|                                    | 7, 2017,          | now Pat. No. 9,785,440, which is a<br>(Continued)                                                            | (57)                                                                                                                                                                                           | ABSTRACT                                                  |  |

| (51)                               | Int. Cl.          | (                                                                                                            | Techniques are described for metadata processing that can<br>be used to encode an arbitrary number of security policies<br>for code running on a processor. Metadata may be added to           |                                                           |  |

|                      |             |                                                                                                                                                                                                                |                                      | ESE150                                                                                                                                                                         | ) Spring 2019                                                                    |

|----------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

|                      |             |                                                                                                                                                                                                                | US005742180A                         |                                                                                                                                                                                |                                                                                  |

| Un                   | ited S      | States Patent [19]                                                                                                                                                                                             | [11]                                 | Patent Number:                                                                                                                                                                 | 5,742,180                                                                        |

| DeF                  | Ion et al   |                                                                                                                                                                                                                | [45]                                 | Date of Patent:                                                                                                                                                                | Apr. 21, 1998                                                                    |

| [54]                 |             | CALLY PROGRAMMABLE GATE<br>WITH MULTIPLE CONTEXTS                                                                                                                                                              | 19th De                              | , M.M., "The Yorktown Sin<br>sign Automation Conference<br>R., et al., "A High Perform                                                                                         | , pp. 55-59 (1982).                                                              |

| [75]                 | Inventors:  | André DeHon, Cambridge; Thomas F.<br>Knight, Jr., Belmont; Edward Tau,<br>Boston; Michael Bolotski, Somerville;<br>Ian Eslick, Cambridge; Derrick Chen,<br>Cambridge; Jerewy Brown,<br>Cambridge, all of Mass. | with<br>Micro-2<br>posium            | R. et al., Argan Fully Fully and<br>Hardware-Programmable<br>7Proceedings of the 27th Ani<br>on Microarchitecture, San<br>0 (Nov. 30-Dec. 2, 1994).<br>(List continued on net) | Functional Units,"<br>nual International Sym-<br>Jose, California, pp.           |

| [73]                 | Assignee:   | Massachusetts Institute of Technology, Cambridge, Mass.                                                                                                                                                        | Assistan                             | Examiner—Edward P. Wes<br>t Examiner—Jon Santamaur<br>Agent, or Firm—Hamilu                                                                                                    | 0                                                                                |

| [21]                 | Appl. No.   | : 386,851                                                                                                                                                                                                      | [57]                                 | ABSTRACT                                                                                                                                                                       |                                                                                  |

| [22]                 | Filed:      | Feb. 10, 1995                                                                                                                                                                                                  | 1                                    |                                                                                                                                                                                |                                                                                  |

| [51]<br>[52]<br>[58] | U.S. Cl     |                                                                                                                                                                                                                | 7 prises a<br>8 These p<br>6 hardwir | grated dynamically program<br>two dimensional array of<br>tates can be implemented<br>ed gates with programmab<br>ssible. Each one of the gate                                 | f programmable gates.<br>as look up tables but<br>le interconnections are        |

| [56]                 | -           | References Cited<br>S. PATENT DOCUMENTS                                                                                                                                                                        | logic si<br>range o<br>include       | nals from plural other gates<br>logic combinations are pos-<br>locally stored multiple con-                                                                                    | . Consequently, a broad<br>sible. The gates further<br>texts dictating different |

|                      | 4.354.228 1 | 6/1982 Tanaka                                                                                                                                                                                                  | 0 context                            | atorial logic operations performed and the logic operations and the fact that the contexts at                                                                                  | ons performable by the                                                           |

# WORK SCENARIOS

- Hired/paid by company to invent

Belongs to company

- Invent on side on free time

- + ...may depend on employment agreement

- + ...whether or not subject matter overlaps with company

- × Consultant

- By default yours, but consulting agreement may define

# UNIVERSITY

- Based on grant funds and resources

- + Typically goes to university and funding source

- Right of first refusal...won't always pursue

- Undergraduate

- + Invent in class, senior-design  $\rightarrow$  yours

- Graduate students paid RA from grant

Typically funded by grant and go to University

- Undergraduate paid research (employee)

+ Typically funded by grant and go to University

- Graduate students in class, using class resources

- Goes to University

# LAB DUE

- Note: Lab due Today (by midnight)

+ Last day of classes (not have due during reading period)

- + Final office hours now to 8pm

# **BIG IDEAS**

- We (engineers...particularly in computing space) are knowledge workers, producing IP

- IP carries great value

+ That is less and less tied to physical objects

- Need to equitably reward and encourage IP creation

- \* Patents, Copyrights, Licenses ...

- + Attempts to provide framework for IP ownership, sharing, monetization

- + ...probably not the final answer, particularly as technology landscape continues to evolve.

# LEARN MORE

\* EAS 507 – IP and Business Law for Engineers

ESE150 Spring 2019

ESE150 Spring 2019

\* EAS 545 – Engineering Entrepreneurship + Has sections on IP

| Торіс               | CIS               | CMPE                         | EE ESE150         | Spring 2019<br>SSE |

|---------------------|-------------------|------------------------------|-------------------|--------------------|

| Analog Circuits     |                   | ESE215                       | ESE215            |                    |

| Compress            | CIS121            | CIS121                       |                   |                    |

| Nyquist,<br>Fourier |                   |                              | ESE224,<br>ESE325 | ESE224,<br>ESE325  |

| Optimization        | CIS320            | (many)                       |                   | ESE204             |

| Digital Logic       | CIS240            | CIS240,<br>ESE370,<br>ESE532 |                   |                    |

| Processor           | CIS371            | CIS371                       |                   |                    |

| OS                  | CIS380            | CIS380                       |                   |                    |

| File System         | CIS380,<br>CIS121 | CIS380,<br>CIS121            |                   |                    |

| IP                  |                   | EAS545                       | ESE545            | ESE545             |

| Networking          |                   | ESE407 or<br>CIS553          | ESE407            | ESE407             |

| Embedded            |                   | ESE350<br>CIS441             | ESE350            | ESE350             |

| UI                  |                   |                              |                   | ESE543             |

|                     |                   |                              |                   | 62                 |

# (NOTES FOR PREVIOUS SLIDE)

- × Bold required

- \* Not bold restricted elective

- \* Simplified to fit on one slide

- + (e.g. should show many more analog circuits courses as restricted-electives for EE)