STORER-PROGRAM PROCESSOR

"STORED PROGRAM" COMPUTER

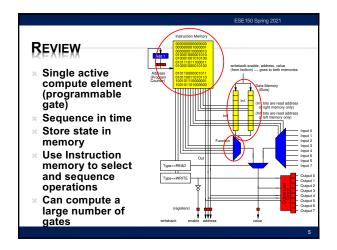

- Can build physical machines that perform any computation.

- Can be built with limited hardware that is reused in time.

- Historically: this was a key contribution of Penn's Moore School

- ENIAC→ EDVAC

- Computer Engineers:

Eckert and Mauchly

- + (often credited to Von Neumann)

**BASIC IDEA**

Express computation in terms of a few primitives

- + E.g. Add, Multiply, OR, AND, NAND

- \* Provide one of each hardware primitive

- Store intermediates in memory

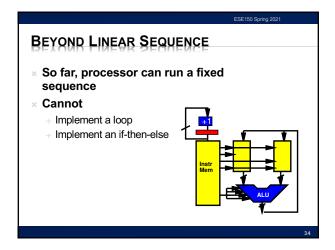

- Sequence operations on hardware to perform larger computation

- Store description of operation sequence in memory as well – hence "Stored Program"

- By filling in memory, can program to perform any computation

\_

ESE150 Spring 2021

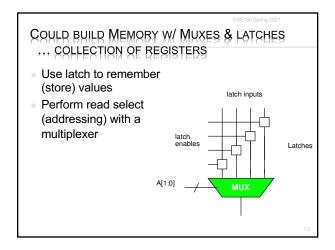

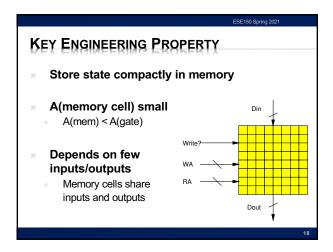

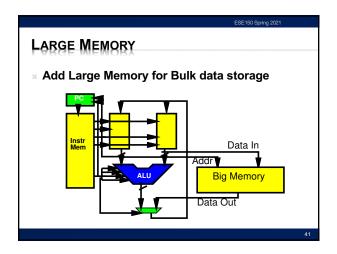

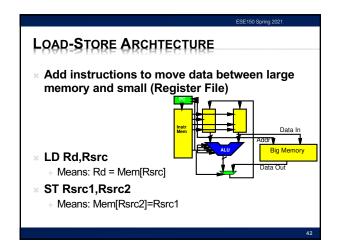

MEMORY

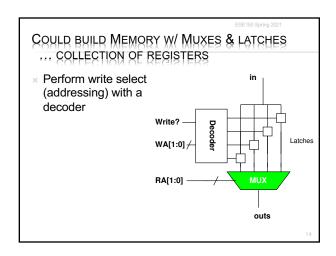

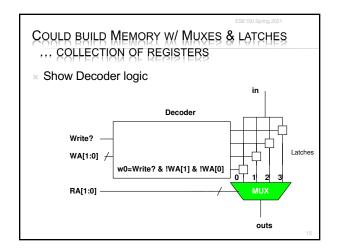

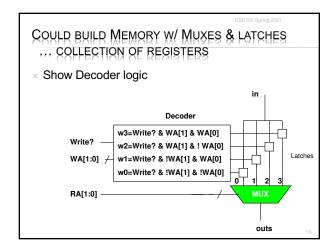

RANDOM ACCESS MEMORY

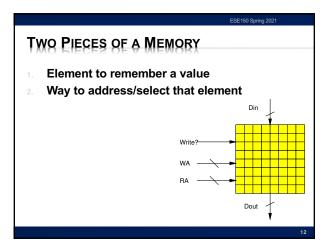

\*\* A Memory:

- Series of locations (slots)

- Can write values a slot (specified by address, WA)

- Read values from (by address, RA)

- Return last value written

Notation:

slash on wire

means multiple bits wide

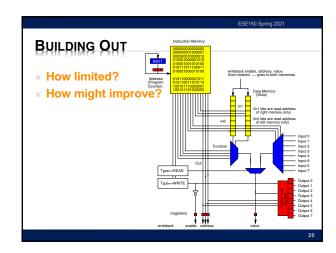

PROCESSORS

\*\*Single gate extreme to make the high-level point

- Except in some particular cases, not practical

\*\*Usually reuse larger blocks

- Multi-bit Adders

- Multipliers

\*\*Get more done per cycle than one gate

\*\*Now it's a matter of engineering the design point

- Where do we want to be between one gate and full circuit extreme?

- How many gate evaluations should we physically compute each cycle?

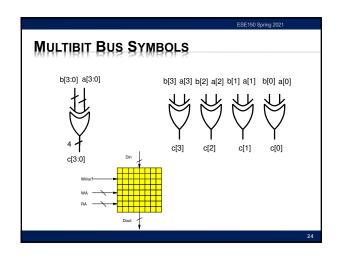

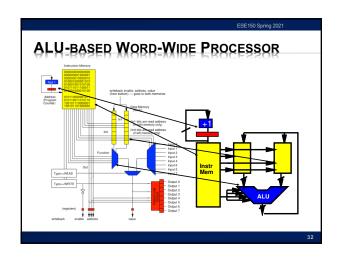

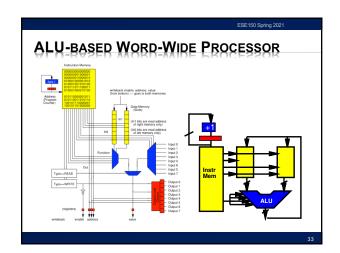

WORD-WIDE PROCESSORS

\* Common to compute on multibit words

+ Add two 16b numbers

+ Multiply two 16b numbers

+ Perform bitwise-XOR on two 32b numbers

\* More hardware

+ 16 full adders, 32 XOR gates

\* All programmable gates doing the same thing

+ So don't require more instruction bits

4

ARITHMETIC AND LOGIC UNIT (ALU)

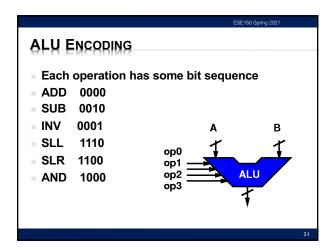

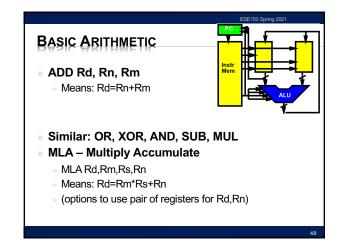

\* A common logic primitive is the ALU

- Can perform any of a number of operations on a series of words (strings of bits)

- Operations: Add, subtract, shift-left, shift-right, bitswise xor, and, or, invert, ....

- Operates on "words"

\* Identify a set of control bits that select the operation it forms

- Makes it "programmable"

ALU OPS (ON 8BIT WORDS)

\* ADD 00011000 00010100 =

- Add 0x18 to 0x14 result is:

- Add 24 to 20

SE150 Spring 202<sup>-</sup>

## **ALU OPS (ON 8BIT WORDS)**

ADD 00011000 00010100 = 00101100

+ Add 0x18 to 0x14 =0x2C0

Add 24 to 20 =44

SUB 00011000 00010100 = 00000100

Subtract 0x14 from 0x18 .. 0x04

INV 00011000 XXXXXXXX =

+ Invert the bits in 0x18 ...gives us:

SE150 Spring 202

## **ALU OPS (ON 8BIT WORDS)**

XOR 00011000 00010100 = 0001100

$\times$  xor 0x18 to 0x14 = 0x0C

× ADD 00011000 00010100 = 00101100

+ Add 0x18 to 0x14 =0x2C0

+ Add 24 to 20 =44

× SUB 00011000 00010100 = 00000100

+ Subtract 0x14 from 0x18 .. 0x04

× INV 00011000 XXXXXXXX = 11100111

+ Invert the bits in 0x18 ...0xD7

SRL 00011000 XXXXXXXX =

+ Shift right 0x18 ... gives us:

21

ESE150 Spring 202

## **ALU OPS (ON 8BIT WORDS)**

× ADD 00011000 00010100 = 00101100

+ Add 0x18 to 0x14 =0x2C0

+ Add 24 to 20 =44

\* SUB 00011000 00010100 = 00000100

+ Subtract 0x14 from 0x18 .. 0x04

× INV 00011000 XXXXXXXX = 11100111

+ Invert the bits in 0x18 ...0xD7

SRL 00011000 XXXXXXXX = 00001100

Shift right 0x18 ...0x0C

ESE150 Spring

## **ALU OPS (ON 8BIT WORDS)**

× ADD 00011000 00010100 = 00101100

+ Add 0x18 to 0x14 =0x2C0

+ Add 24 to 20 =44

SUB 00011000 00010100 = 00000100

+ Subtract 0x14 from 0x18 .. 0x04

INV 00011000 XXXXXXXX = 11100111

+ Invert the bits in 0x18 ...0xD7

× SRL 00011000 XXXXXXXX = 00001100

+ Shift right 0x18 ...0x0C

× XOR 00011000 00010100 = 0001100

xor 0x18 to 0x14 = 0x0C

30

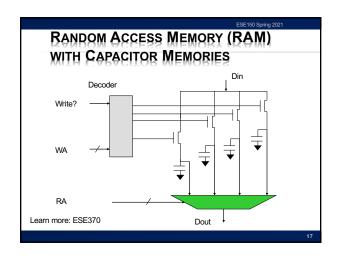

LEARN MORE

CIS240 – processor organization and assembly

CIS471 – implement and optimize processors

Including FPGA mapping in Verilog

ESE370 – implement memories (and gates)

using transistors

REMINDERS

\* Feeback

\* Lab 8 due on Friday

8