1

Creative / Intellectual work produces most of

ESE150 Spring 20

At least in volume, physical costs of reproduction is small part of product price

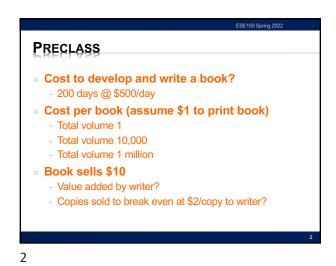

## **PRECLASS CONTINUED**

- \* Cost to photocopy 200 page book at \$0.05/page?

- \* Cost to scan book at 10page/minute?

- \* Cost to perform a 10s copy onto flash drive?

- \* Cost of portion of flash drive used + \$4 for 32GB drive, 0.5MB file

## **OBSERVE**

\* With digital representation + Cost of "physical" reproduction trends to 0

ESE150 Sr

## Past

- Much of value in physical construction of objects

- + Bridge, house, car, screwdriver

- x Expensive to reproduce / copy

- Reproductions imperfect

5<sup>th</sup> generation analog recording

- + 4<sup>th</sup> generation photocopy of text

Inherent barrier to making copies

- + Value to buying original

### **DIGITAL REPRESENTATION**

- Can represent perfectly in bits

+ Including sound, words

- \* Can make perfect copies

- Bits are cheap...and getting cheaper

+ Copying "free"

- Intellectual value disconnected from physical reproduction

8

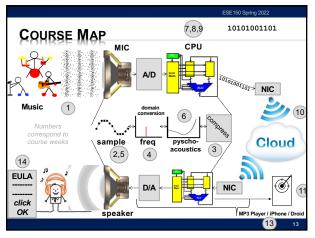

Digital Intellectual Property

Physical IP Renderer

Novel

eReader

Song (MP3)

MP3 Player

JPEG Photo

Video Player

Video Game

Arduino or Personal Computer

Verilog digital circuit

STL (3D CAD drawing)

DNA Sequence

DNA Printer

#### 9

7

# INTELLECTUAL PROPERTY

- \* Intangible creations of human intellect

- × Have value

- Don't necessarily have physical embodiment on their own

10

## INTELLECTUAL PROPERTY CREATORS

### × As Engineers

- + Program, develop algorithms, design circuits

- Almost everything we create will have this property

- + Value added is intellectual

- + Can be represented digitally in bits

- + Can (increasingly) be copied/reproduced cheaply

- × Easy to have impact

- + Our solutions can reach millions, billions

- + Decreasing physical barriers to propagation of solutions

- \* Challenge to protect and reward IP creators

### OUTLINE

- × Setup Need / Opportunity What is IP

- × Where are we

- \* Rationale for IP Protection Why Protect

- How protect?

- + Patents

- + Copyrights

- Unen Source

- ⊥ NDA

- Liconeir

- LICCHOIN

13

14

## PRICING CHALLENGE

- $\times$  When cost of copying  $\rightarrow$  0

- Inventor/author must recover development cost

Price must include develop cost + copy cost

- Copier does not have development cost

- × Price = copy cost + epsilon

- $\times$  Competition of copiers will drive epsilon down near 0

- + Inventor/author not compensated for development

× Remove incentive/reward for development

- Demand: developers need way to exclude others from copying to incentivize creation

15

# ARROW'S INFORMATION PARADOX Customer not know how to value information until

- see information (see details of product)

- + Enough information to decide to buy

- Enough information to decide what will pay for it

- Once show customer information, sufficient detail, they have enough information to reproduce + Could walk away and produce their own without paying for it

- Disclosure of what effectively transfers technology

- × Demand: protection for developer

- Arrow, Kenneth J. Economic Welfare and the Allocation of Resources for Invention, in *The Rate and Direction of Inventive Activity*, 609 (Nat'l Bureau of Econ. Research ed. 1962).

16

# BALANCE INDIVIDUAL AND SOCIETAL GOOD

- \* Individual should benefit form their own effort

- Society advances with the accumulation of knowledge

INTERLURE; NIL NIKOLAI IVANOVICH LOBACHEVSKV https://www.youtube.com/watch?v=gXilXirQF3A

#### ESE150 Spring 2022

## BEFORE COPYING WAS AN ISSUE

- Concern that new developments/ideas would be lost when inventor die

- + Techniques could remain secret for decades!

- × Incentive to make inventions known

- + Advance the general welfare

## **US CONSTITUTION**

#### \* Article 1, Section 8, Clause 8:

To promote the Progress of Science and useful Arts, by securing for limited Times to Authors and Inventors the exclusive Right to their respective Writings and Discoveries

ESE150 Spring 202

#### 20

19

21

| Engineering | ESE |

|-------------|-----|

|             |     |

|             |     |

|             |     |

| Part 3      |     |

| PATENTS     |     |

| BVIEVILG    |     |

|             | 23  |

## **MECHANISMS FOR PROTECTION**

- × Messy and imperfect

- × Haven't kept up with technology

- Likely need (and will need) innovation and refinement

22

## PATENT

- × Inventions

- \* Non-obvious to one "ordinary skill in art"

- Reduced to practice

- × Cannot patent

- + Abstract ideas

- + Laws of nature

- × US: First to file

- + (prior to 2013 was first to invent)

- × Exclusive rights 20 years from filing

ESE150 Spring 202

\* Identification of problem is part of invention

it, may be better to keep as a trade secret

Validity of many patents overturned in litigation

Recover damages through litigation

If really believe no one else will figure it out...or can copy

## WHAT MIGHT BE TRICKY / NON-SATISFYING?

- \* First to file? (even invent?)

- × 20 year term?

25

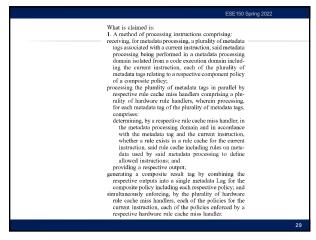

#### PATENT PROCESS (12) United States Patent (10) Patent No.: US 10,725,778 B2 (45) Date of Patent: Jul. 28, 2020 US have one year from first-public disclosure to file PROCESSING METADATA, POLICIES, AND (56) COMPOSITE TAGS References Cited U.S. PATENT DOCUMENTS HTE TAGS EThe Charles Stark Draper Laboratory, Inc., Cambridge, MA (US); The Trustees of the University of Pennsylvania Penn Center for Innovation, Philadelphia, PA (US) Many places – public disclosure prevents patent https://www.uspto.gov/web/offices/pac/mpep/s2153.html (Continued) Innovation, Philadelphia, PA (US) Inventors: André Dellon, Cambridge, MA (US); Udit Dhawan, New Delhi (UN) Assignees: The Charles Stark Drager Laboratory. Inc. Cambridge, MA (US); The Trustees of the University of Pennsylvania Penn Center for Innovation, Philadelphia, PA (US) May file provisional patent to get filing date FOREIGN PATENT DOCUMENTS GB 2519608 A 4/2015 2010028316 A1 3/2010 File patent with claims OTHER PUBLICATIONS Reviewed by examiner nded or adjusted un by 0 days. Zeldovich et. al, Hardware Enforcemen Policies Using Tagged Memory, Procees conference on Operating systems design 225-240 (2008).\* Subject to any patent is exter U.S.C. 154(b) : 16802.642 Examiner reports on what may be allowable Security USEND cm As-is Filed: Jun. 7, 2018 Prior Public rrinwary Examiner — Sharon S Lyuch (74) Attorney; Agent, or Firm — Hamilt & Reynolds, P.C. With tighter qualifications Prior Publication Data US 2018/0336031 A1 Nov. 22, 2018 Related U.S. Application Data Not-at-all ABSTRACT Continuation of application No. 15/695,541, filed on Sep. 5, 2017, now Pat. No. 10,261,794, which is a (Continued) A sensitive function is featured by the first study for the sensitive process of the sensitive p On a per-claim basis Typically requires several iterations (51) Int. Cl. G06F 9/30 G06F 9/38 (2018.01) (2018.01) Continued) Often year(s) before patent issues (52) U.S. CL CPC ...... G06F 9/30101 (2013.01); G06F 9/30072 (2013.01); G06F 9/30098 (2013.01); Filing costs thousands of dollars With lawyer/legal fees tens to hundreds of thousands

28

PATENT

× Claims

$\mathbf{x}$

26

Define the invention

Technical coverage

Requires disclosure

License to litigate

Establish violation

|                      |            |                                                                                                                                                                                                                |                                                                                                                                                                                                                                           | ESE150 Spring 2022                                                                                                                                                                |                                                                                                           |  |

|----------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--|

|                      |            |                                                                                                                                                                                                                |                                                                                                                                                                                                                                           | US005742180A                                                                                                                                                                      |                                                                                                           |  |

| Ur                   | nited S    | States Patent [19]                                                                                                                                                                                             | [11]                                                                                                                                                                                                                                      | Patent Number:                                                                                                                                                                    | 5,742,180                                                                                                 |  |

| DeF                  | Ion et al  | •                                                                                                                                                                                                              | [45]                                                                                                                                                                                                                                      | Date of Patent:                                                                                                                                                                   | Apr. 21, 1998                                                                                             |  |

| [54]                 |            | CALLY PROGRAMMABLE GATE<br>VITH MULTIPLE CONTEXTS                                                                                                                                                              | 19th De:                                                                                                                                                                                                                                  | Denneau, M.M., "The Yorktown Simulation Engine," <i>IEEE</i><br>19th Design Automation Conference, pp. 55-59 (1982).<br>Razdan, R., et al., "A High Performance Microarchitecture |                                                                                                           |  |

| [75]                 | Inventors: | André DeHon. Cambridge; Thomas F.<br>Knight, Jr., Belmont: Edward Tau,<br>Boston; Michael Bolotski, Somerville;<br>Ian Eslick, Cambridge; Derrick Chen,<br>Cambridge; Jeremy Brown,<br>Cambridge; all of Mass. | with Hardware-Programmable Functional Units,"<br>Micro-27Proceedings of the 27th Annual International Sym-<br>posium on Microarchitecture, San Jose, California, pp.<br>172–180 (Nov. 30–Dec. 2, 1994).<br>(List continued on next page.) |                                                                                                                                                                                   |                                                                                                           |  |

|                      | -          | Massachusetts Institute of Technology, Cambridge, Mass.                                                                                                                                                        | Assistan                                                                                                                                                                                                                                  | Examiner—Edward P. Wes<br>t Examiner—Jon Santamaun<br>Agent, or Firm—Hamilus, P.C.                                                                                                | 10                                                                                                        |  |

| [21]                 | Appl. No.  |                                                                                                                                                                                                                | [57]                                                                                                                                                                                                                                      | ABSTRACT                                                                                                                                                                          |                                                                                                           |  |

| [22]                 | Filed:     | Feb. 10, 1995                                                                                                                                                                                                  | An inte                                                                                                                                                                                                                                   | erated dynamically program                                                                                                                                                        | mable gate array com-                                                                                     |  |

| [51]<br>[52]<br>[58] | U.S. Cl    | H03K 19/17<br>326/40; 326/3<br>earch                                                                                                                                                                           | 7 prises a<br>8 These g<br>6 hardwir                                                                                                                                                                                                      | two dimensional array of<br>fates can be implemented<br>ed gates with programmab<br>sible. Each one of the gate                                                                   | f programmable gates.<br>as look up tables but<br>le interconnections are                                 |  |

|                      | 4,336,601  | References Cited           S. PATENT DOCUMENTS           5/1982 Tanaka         364/93           3/1982 Moore et al.         364/92                                                                             | logic sig<br>range of<br>include<br>0 combine                                                                                                                                                                                             | some for plural other gates<br>alogic combinations are pos-<br>locally stored multiple con-<br>torial logic operations perfo-<br>s increase the logic operations                  | Consequently, a broad<br>sible. The gates further<br>texts dictating different<br>ormed by the gates. The |  |

|                      |            | 1982 More et al                                                                                                                                                                                                | o contexts                                                                                                                                                                                                                                | increase the logic operation                                                                                                                                                      |                                                                                                           |  |

|        | ESE150 Spring 2022                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLAIMS | <ul> <li>We claim: <ol> <li>An integrated dynamically programmable logic array,</li> <li>comprising:</li> <li>at least a two dimensional array of programmable logic elements, each one of the logic elements receiving plural input logic signals from plural other logic elements and including locally stored multiple contexts dictating different combinatorial logic operations performed by the logic elements; and</li> <li>a context signal source that provides a context signal, indicating an active one of the contexts, commonly to the programmable logic elements of the array; and</li> <li>wherein the contexts for each one of the logic elements are individually accessible so that a new context can be loaded into the logic elements while another context is gnal up to every cycle of the programmable logic array as described in claim 1, wherein the context signal source provides the context signal up to every cycle of the programmable logic array.</li> <li>A programmable logic array as described in claim 1, wherein the context signal source generates plural context signals that dictate contexts for regions of the array of the logic alements.</li> </ol></li></ul> |

|        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

33

ENIAC US 3,120,606 1. MEANS FOR PRODUCING ELECTRIC PULSES IN SEQUENCE, 1. MEANS FOR PRODUCING ELECTRIC PULSES IN SEQUENCE, ELECTRONIC MEANS FOR ALTERNATELY TRANSMITTING CERTAIN ONES OF SAID PULSES AS RECURRENT DIFFERENTIATED GROUPS, ELECTRONIC MEANS FOR SELECTING PARTICULAR PULSES FROM ONE OF SAID DIFFERENTIATED GROUPS TO REPRESENT QUANTITATIVE VALUES, ELECTRONIC MEANS FOR SELECTING PARTICULAR PULSES FROM ANOTHER OF SAID DIFFERENTIATED GROUPS TO REPRESENT CERTAIN QUALITATIVE VALUES, READING MEANS RESPONSIVE TO PULSES REPRESENTING BOTH THE QUALITATIVE AND QUANTITATIVE VALUES REPRESENTING BOTH THE QUALITATIVE AND QUANTITATIVE VALUES REPRESENTING BOTH THE QUALITATIVE AND QUANTITATIVE VALUES FOR READING DATA TO BE PROCESSED UPON COMMAND OF AT LEAST ONE OF SAID QUALITATIVE PULSES, STORING THE DATA THUS LEAST ONE OF SAID COACTION AND A DESCRIPTION OF THE FORM OF DATA PULSES IN RESPONSE TO AT LEAST ONE OTHER OF SAID QUALITATIVE PULSES, AND ELECTRONIC MEANS FOR RECEIVING SAID DATA PULSES, AND RESPONSIVE THERE TO FOR PERFORMING ELECTRICAL SWITCHING DEPENDING OF A NATURE DETERMINED BY SELECTED ONES OF SAID OF SAID QUALITATIVE VALUES AND OF A DEGREE DETERMINED BY SELECTED ONES OF SAID QUANTITATIVE VALUES. https://www.computerhistory.org/revolution/birth-of-the-computer/4/99/387

35

## XILINX FPGA US 4,870,302

#### ABSTRACT

[57] ABSTRACT A configurable logic array comprises a plurality of configurable logic elements variably interconnected in response to control signals to perform a selected logic function. Each configurable logic element in the array is in itself capable of performing any one of a plurality of logic functions depending upon the control information placed in the configurable logic element. Each configu-rable logic element can have its function varied even after it is installed in a system by changing the control information placed in that element. Structure is pro-vided for storing control information to allow each configurable logic element to be properly configured prior to the initiation of operation of the system of which the array is a part. Novel interconnection struc-tures are provided to facilitate the configuring of each logic element.

# I claim: 1. An interconnect structure for programmably inter-connecting lines within an integrated circuit compris-

ESE150 Spring 20

connecting lines within an integrated circuit compris-ing: at least three sets of interconnect line including a first set, a second set, and a third set; programmable means, not including said sets of inter-connect lines, for connecting at least one of said lines in said second set, and a third set; said second set, for connecting at least one of said said shift set, and for connecting at least one of said lines in said second set to at least one of said lines in said second set to at least one of said lines in said second set to at least one of said lines in said second set to at least one of said lines in said third set. A narray of interconnect structures, each said in-terconnect structure in said array having its own selected sumber of interconnect lines and its own programmable means for connecting interconnect lines in its own first, second and third sets.

https://patents.google.com/patent/US4870302A/en?oq=us+4870302

34

[57]

# WHAT'S PATENTABLE

- Not law's of nature

- Not abstract ideas

- × Cannot patent pi  $(\pi)$

- × Software?

- Originally not

- With reference to machine, can often manage

- Genetic sequences?...

- ...evolving...

36

## COPYRIGHT

- Cover particular, original expression Including software

- Technically don't need to register

- But should...

- Must register before sue for infringement

- \$35

- No review, just registration

- Life of author + 70 years ×

- Work for hire: 95 years from publication

## TRADITIONALLY: TRANSFER COPYRIGHT ...

#### × Publish in ACM, IEEE journal

+ Transfer copyright to them, they license you back rights for derived work and post on person web site.

Copyright (c) 1996 by the Association for Computing Machinery, Inc. Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that new copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Request Permissions from Publications Dept, ACM Inc., Fax +1 (212) 869-0481, or cermissions@acm.org>.

39

#### ESE150 Spring 2022

### **BIG IDEAS**

- We (engineers...particularly in computing space) are knowledge workers, producing IP

- IP carries great value

- That is less and less tied to physical objects

- Need to equitably reward and encourage IP creation

- Patents, Copyrights...two of the things that

Attempts to provide framework for IP ownership, sharing, monetization

- + ...probably not the final answer, particularly as technology landscape continues to evolve.

## RECENT: LICENSE TO ACM, IEEE

#### × Author retain copyright, license to publisher

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than the author(s) must be honored. Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from permissions@acm.org.

FPGA '17, February 22 - 24, 2017, Monterey, CA, USA

© 2017 Copyright held by the owner/author(s). Publication rights licensed to ACM. ISBN 978-1-4503-4354-1/17/02...\$15.00

${\tt DOI: http://dx.doi.org/10.1145/3020078.3026124}$

40

#### REMEMBER

- \* Feedback including Lab

- × Lab 11 due today

- × Lab 12 Wednesday