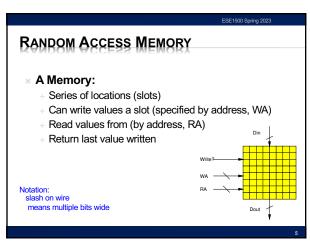

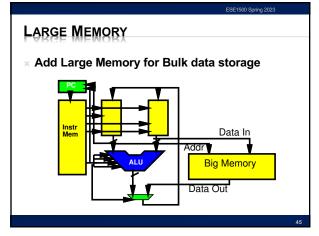

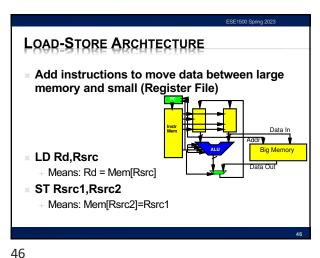

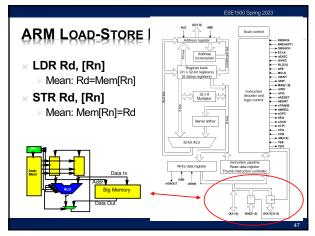

KEY ENGINEERING PROPERTY Store state compactly in memory A(memory cell) small A(mem) < A(gate) Depends on few inputs/outputs Memory cells share inputs and outputs

5 12

REVIEW

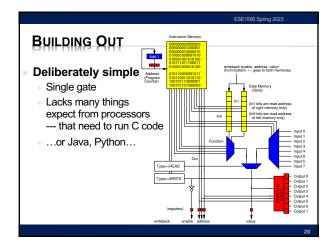

\* Can compute a large number of gates – by

\* Single active compute element (programmable gate)

\* Sequence in time

\* Store state in memory

\* Use Instruction memory to select and sequence operations

13 14

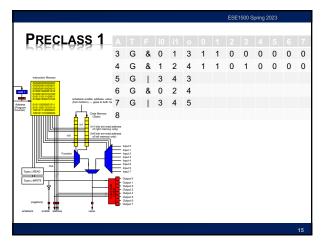

STORER-PROGRAM PROCESSOR

15 16

## "STORED PROGRAM" COMPUTER Can build physical machines that perform any computation.

- Can be built with limited hardware that is reused in time.

- Historically: this was a key contribution of Penn's Moore School

- + ENIAC→ EDVAC

- Computer Engineers:Eckert and Mauchly

- + (often credited to Von Neumann)

Express computation in terms of a few primitives

E.g. Add, Multiply, OR, AND, NAND

Provide one of each hardware primitive

Store intermediates in memory

Sequence operations on hardware to perform larger computation

Store description of operation sequence in memory as well – hence "Stored Program"

By filling in memory, can program to perform any computation

17 18

20

**PROCESSORS**

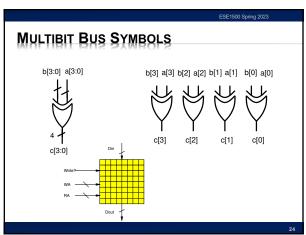

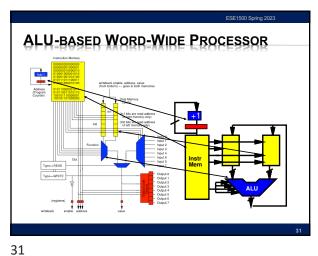

**BEYOND SINGLE GATE** Single gate extreme to make the high-level point Except in some particular cases, not practical » Usually reuse larger blocks Multi-bit Adders Multipliers Get more done per cycle than one gate \* Now it's a matter of engineering the design point Where do we want to be between one gate and full circuit How many gate evaluations should we physically compute each cycle?

21 22

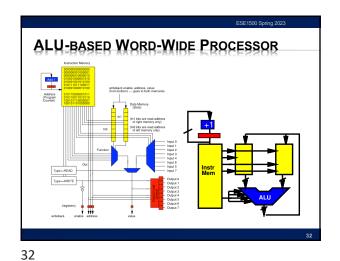

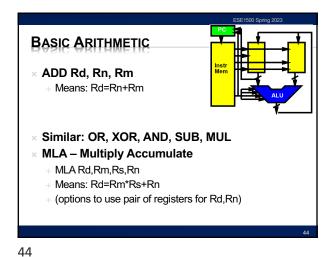

WORD-WIDE PROCESSORS Common to compute on multibit words Add two 16b numbers Multiply two 16b numbers Perform bitwise-XOR on two 32b numbers More hardware + 16 full adders, 32 XOR gates \* All programmable gates doing the same thing So don't require more instruction bits

23 24

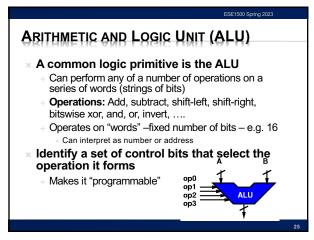

ALU OPS (ON 8BIT WORDS)

\* ADD 00011000 00010100 =

+ Add 0x18 to 0x14 result is:

+ Add 24 to 20

25 26

ALU OPS (ON 8BIT WORDS)

\* ADD 00011000 00010100 = 00101100

+ Add 0x18 to 0x14 = 0x2C0

+ Add 24 to 20 = 44

\* SUB 00011000 00010100 = 00000100

+ Subtract 0x14 from 0x18 ... 0x04

\* INV 00011000 XXXXXXXXX =

+ Invert the bits in 0x18 ... gives us:

ALU OPS (ON 8BIT WORDS)

\*\* ADD 00011000 00010100 = 00101100

+ Add 0x18 to 0x14 = 0x2C0

+ Add 24 to 20 = 44

\*\* SUB 00011000 00010100 = 00000100

+ Subtract 0x14 from 0x18 ...0x04

\*\* INV 00011000 XXXXXXXXX = 11100111

+ Invert the bits in 0x18 ...0xD7

\*\* SRL 00011000 XXXXXXXXX = 00001100

+ Shift right 0x18 ...0x0C

27 28

ALU OPS (ON 8BIT WORDS)

\*\*ADD 00011000 00010100 = 00101100

+ Add 0x18 to 0x14 = 0x2C0

+ Add 24 to 20 = 44

\*\*SUB 00011000 00010100 = 00000100

+ Subtract 0x14 from 0x18 ... 0x04

\*\*INV 00011000 XXXXXXXXX = 11100111

+ Invert the bits in 0x18 ... 0xD7

\*\*SRL 00011000 XXXXXXXXX = 00001100

+ Shift right 0x18 ... 0x0C

\*\*XOR 00011000 00010100 = 000001100

\*\* xor 0x18 to 0x14 = 0x0C

**ALU ENCODING** x Each operation has some bit sequence × ADD 0000 × SUB 0010 × INV 0001 × SLL 1110 op0 × SRL 1100 op1 op2 × SRA 1101 × AND 1000

29 30

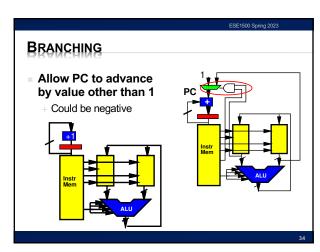

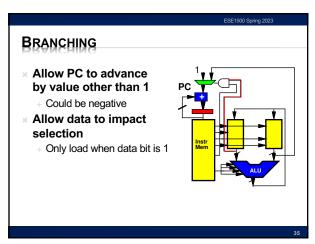

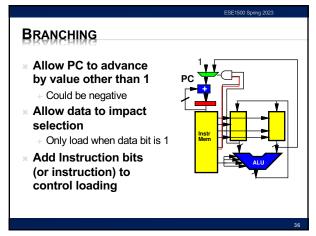

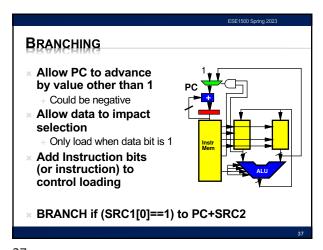

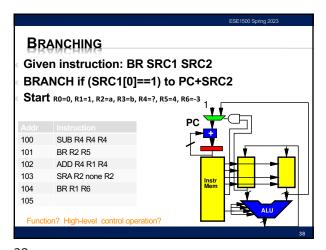

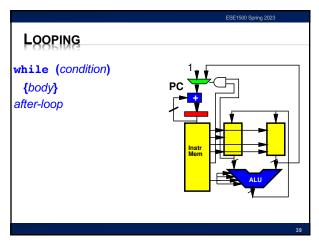

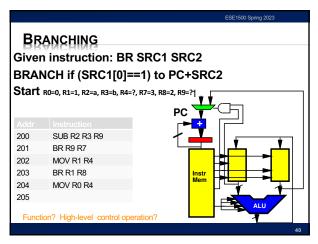

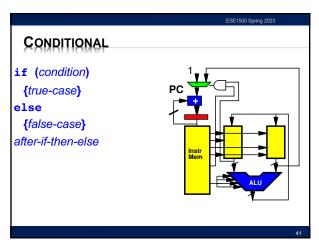

**BEYOND LINEAR SEQUENCE** x So far, processor can run a fixed sequence × Cannot + Implement a loop + Implement an if-then-else

33 34

35 36

3/27/23

37 38

39 40

41 42

45

**BIG IDEAS** Memory stores data compactly Can implement large computations on small hardware by reusing hardware in time Storing computational state in memory x Can store program control in instruction memory Change program by reprogramming memory + Universal machine: Stored-Program Processor

47 48

ESE1500 :

## LEARN MORE

- CIS2400 processor organization and assembly

- CIS4710 implement and optimize processors

Including FPGA mapping in Verilog

- ESE3700 implement memories (and gates) using transistors

REMINDERS

- × Feeback

- × Lab 7 due today

- x Lab 8 today

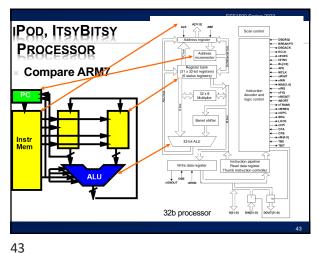

- + Back to using ItsyBitsy

- Prelab on Arduino software you installed on your computer for Lab 1

- Bring kit to lab

50