#### ESE532: System-on-a-Chip Architecture

Day 18: October 31, 2018 Design Space Exploration

### Penn

#### Message

- The universe of possible implementations (design space) is large

Many dimensions to explore

- · Formulate carefully

ESE532 Fall 2018 -- DeH

n ESE532 Fall 2018 -- DeHor

- Approach systematically

- Use modeling along the way for guidance

#### **Design Space**

- · Have many choices for implementation

- Alternatives to try

- Parameters to tune

- Mapping options

- Our freedom to impact implementation costs

- Area, delay, energy

#### Penn ESE532 Fall 2018 -- DeHon

## Design Space Ideally – Each choice orthogonal axis in high

- Each choice orthogonal axis in highdimensional space

- Want to understand points in space

- Find one that bests meets constraints and goals

- Practice

- Seldom completely orthogonal

- Requires cleverness to identify dimensions

- Messy, cannot fully explore

- ESE532 Fail 2018 behom understand, prioritize, guide

6

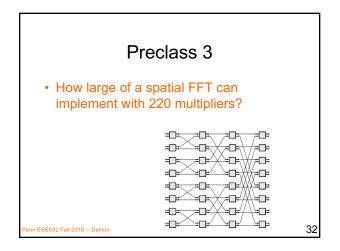

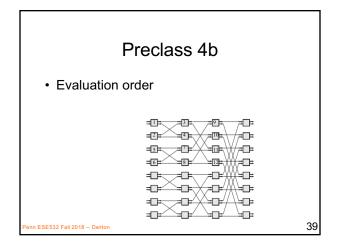

#### Preclass 1

- What choices (design-space axes) can we explore in mapping a task to an SoC?

- What showed up in homework so far?

Penn ESE532 Fall 2018 -- DeHon

#### From Homework?

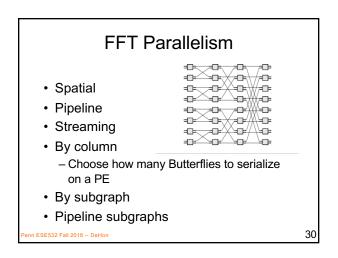

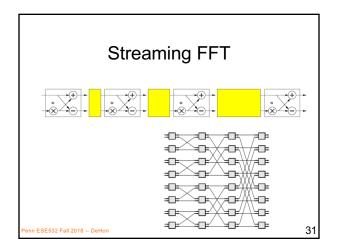

- · Types of parallelism

- Mapping to different fabrics / hardware

- How manage memory, move data

- DMA, streaming

- Data access patterns

- · Levels of parallelism

- Pipelining, unrolling, II, array partitioning and packing

8

nn ESE532 Fall 2018 -- DeHon

#### **Design-Space Choices**

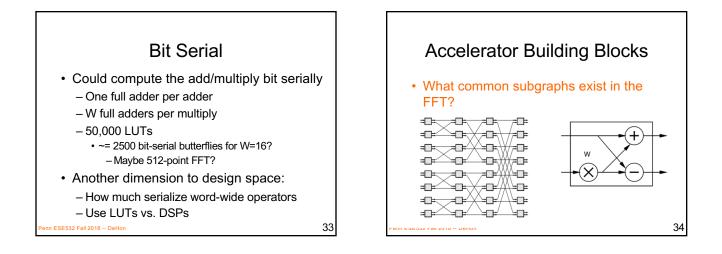

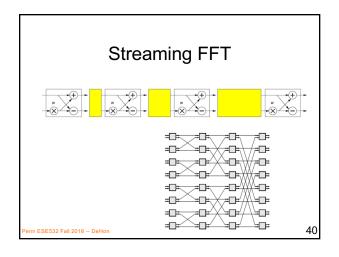

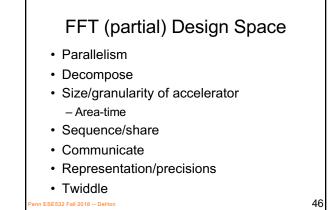

- · Type of parallelism

- How decompose / organize parallelism

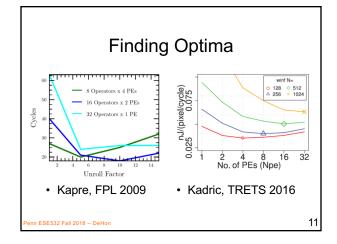

- · Area-time points (level exploited)

- What resources we provision for what parts of computation

- · Where to map tasks

- · How schedule/order computations

- How synchronize tasks

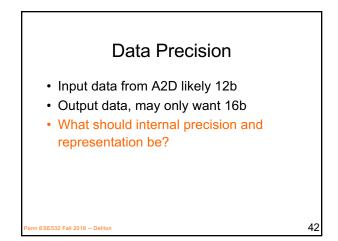

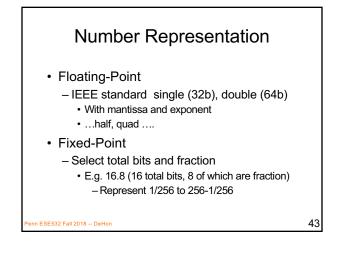

- How represent data

- Where place data; how manage and move

- What precision use in computations

#### Elaborate Design Space

- Refine design space as you go

- · Ideally identify up front

- · Practice bottlenecks and challenges

- will suggest new options / dimensions

If not initially expect memory bandwidth to be a bottleneck...

- Some options only make sense in particular sub-spaces

- Bitwidth optimization not a big issue on the 64b processor

- More interesting on vector, FPGA

# Tools Sometimes tools will directly help you explore design space What SDSoC/Vivado HLS support? Often they will not What might you want that does not support?

14

13

in ESE532 Fall 2018 -- DeHon

nn ESE532 Fall 2018 -- De

#### **Heterogeneous** Precision

· May not be same in every stage

===

====

=

====

===

===

===

=

n ESE532 Fall 2018 -- De

- W factors less than 1

÷

:

=∏=

====

===

===

-

≓∏≓

≓ि≓

¥∎=

≍∎⊧∖

=∎=^

≠⊒≠∕

:**--**--

÷

₌□=

===

≓∏≓

'=⊡=

≓∎=

∖≒⊡≓

÷

44

#### **Big Ideas:**

- · Large design space for implementations

- · Worth elaborating and formulating systematically

- Make sure don't miss opportunities

- · Think about continuum for design axes

- · Model effects for guidance and understanding

ESE532 Fall 2018 -- DeHo

47