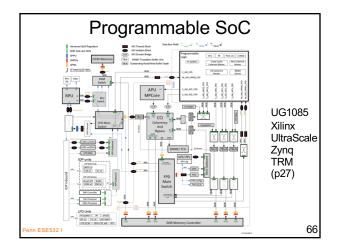

#### ESE532: System-on-a-Chip Architecture Day 14: October 16, 2019 Real Time Day 14: October 16, 2019 Construction Real Time Disciplines to achieve Methods Meth

3

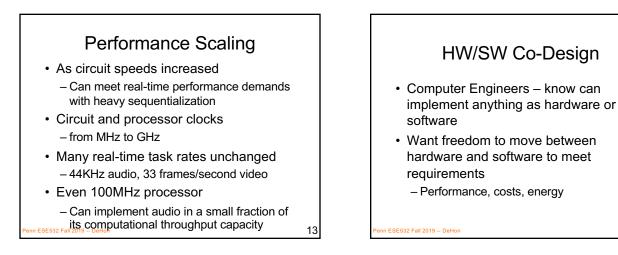

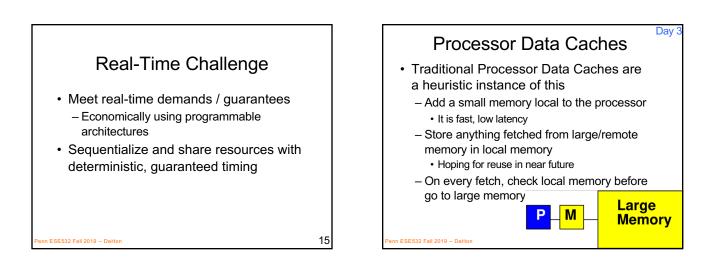

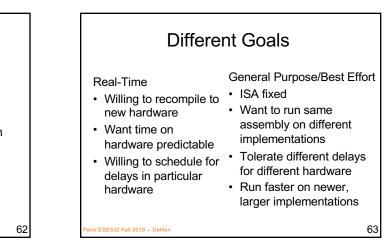

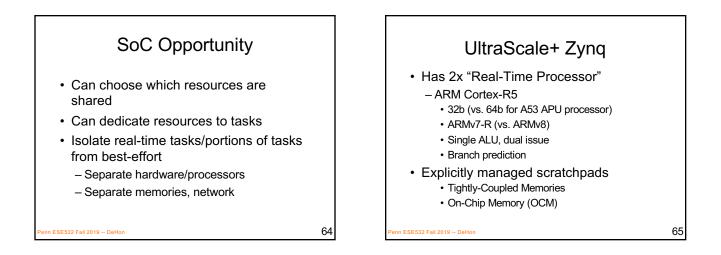

- Real-Time applications demand different discipline from best-effort tasks

- · Look more like synchronous circuits

- · Can sequentialize, like processor

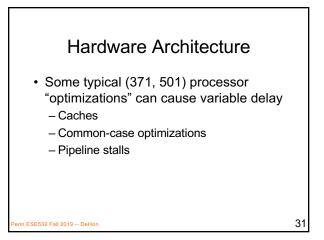

- But must avoid/rethink typical generalpurpose processor common-case optimizations

# Real Time

- "Real" refers to physical time – Connection to Real or Physical World

- · Contrast with "virtual" or "variable" time

- Handles events with absolute guarantees on timing

#### Real-Time Tasks

- What timing guarantees might you like for the following tasks?

- Turn steering wheel on a drive-by-wire car

Delay to recognized and car turns

- Self-driving car detects an object in its path

- Delay from object appearing to detection

- Pacemaker stimulates your heart

- Video playback (frame to frame delay)

#### Penn ESE532 Fall 2019 -- DeHon

ESE532 Fall 2019 -- DeH

- Both: schedule to act and complete action

- Bounded response time

- Respond to keypress within 20 ms

- Detect object within 100 ms

- Return search results within 200 ms

nn ESE532 Fall 2019 -- DeHon

ESE532 Fall 2019 -- DeH

ESE532 Fall 2019 -- DeHo

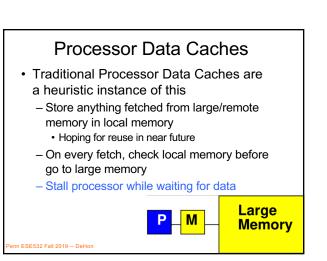

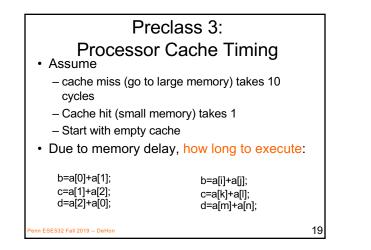

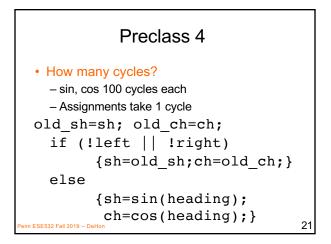

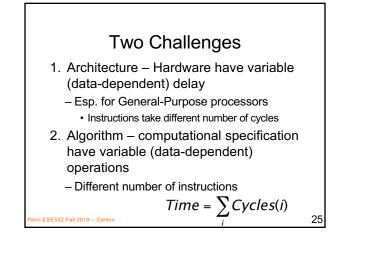

#### Processor Variable Delay

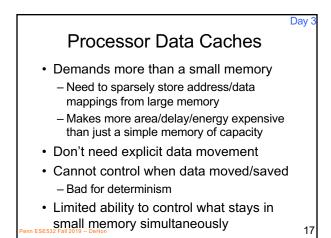

- Caches

- Dynamic arbitration for shared resources

- Bus, I/O, Crossbar output, memory,  $\ldots$

- Data hazards

SE532 Fall 2019 -- DeHor

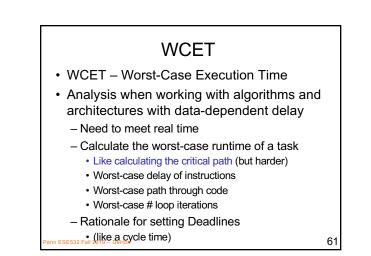

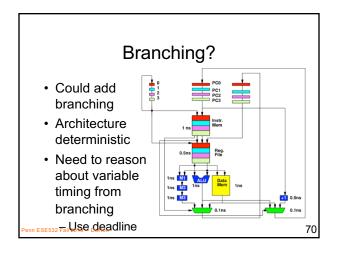

- Data-dependent branching / branch delays

- Speculative issue

- Out-of-Order, branch prediction

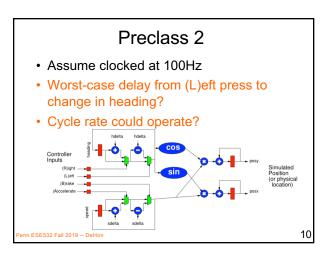

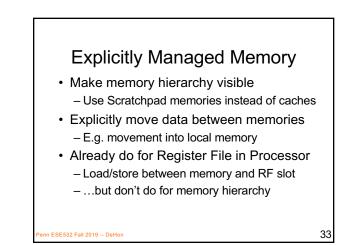

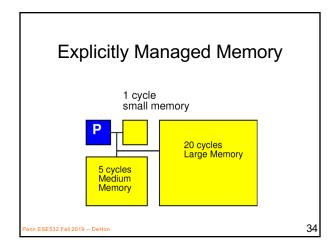

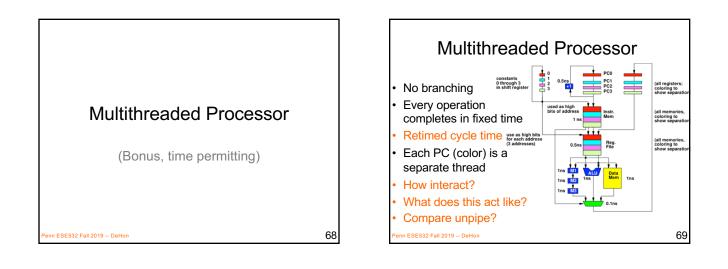

#### What can we do to make architecture more deterministic?

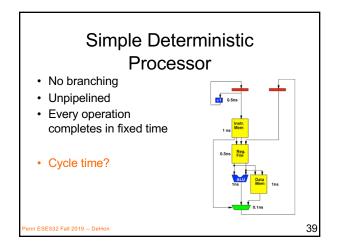

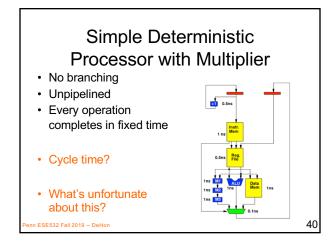

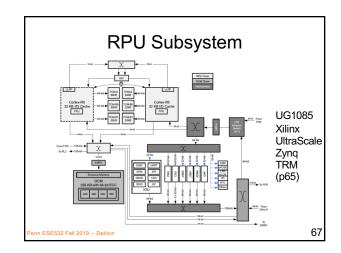

- Explicitly managed memory

- Eliminate Branching (too severe?)

- Unpipelined processors

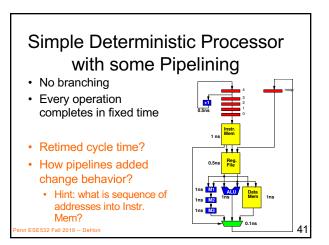

- · Fixed-delay pipelines

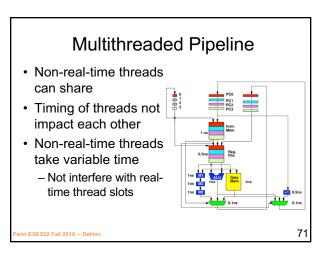

- Offline-scheduled resource sharing

Multi-threaded

32

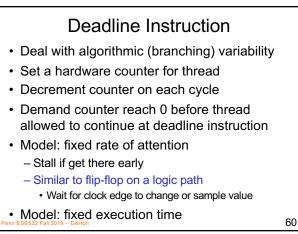

- Deadlines

- nn ESE532 Fall 2019 -- DeHon

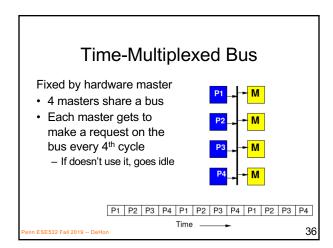

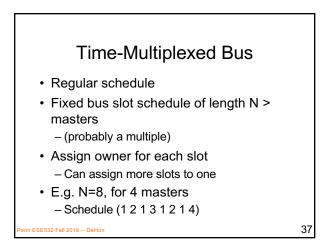

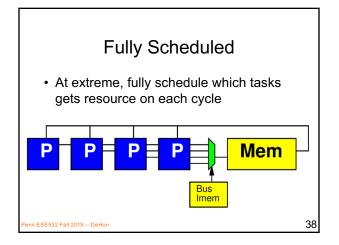

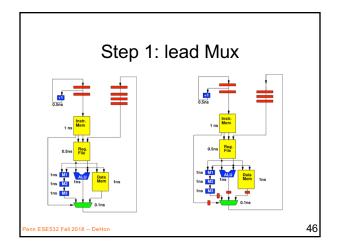

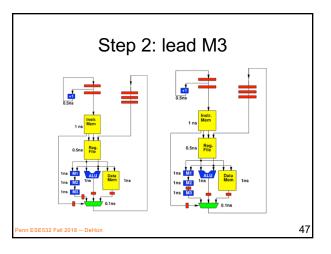

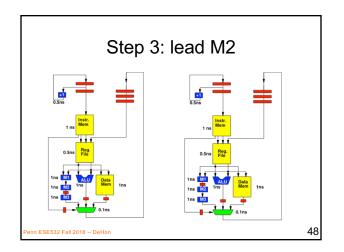

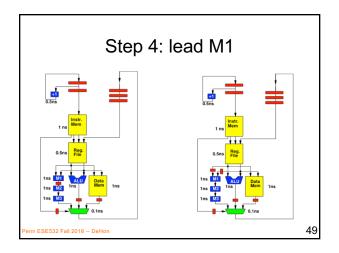

## Offline Schedule Resource Sharing • Don't arbitrate

- Decide up-front when each shared resource can be used by each thread or processor

Simple fixed schedule

- Detailed Schedule

- What

SE532 Fall 2019 -- DeHor

– Memory bank, bus, I/O, network link, ...

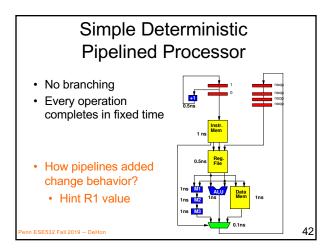

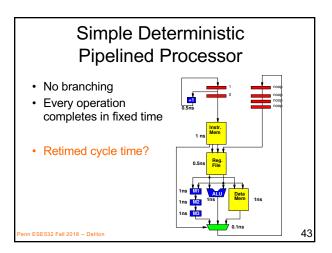

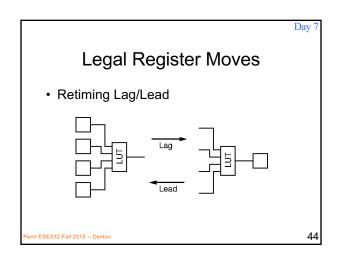

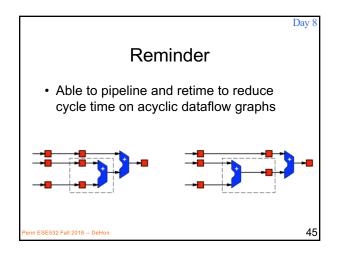

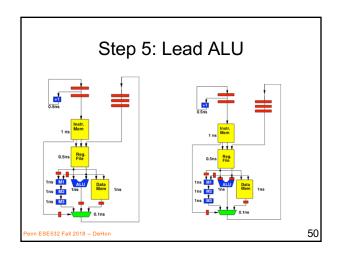

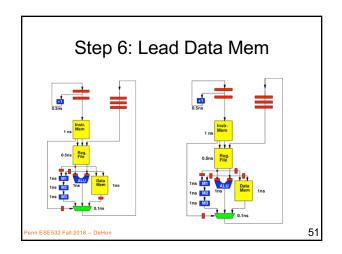

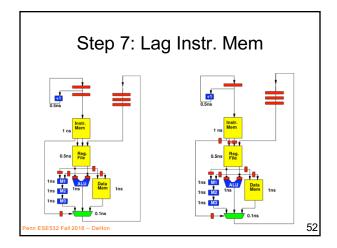

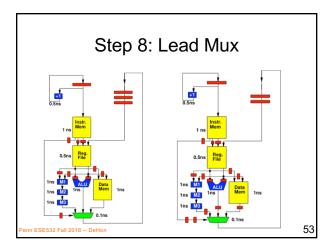

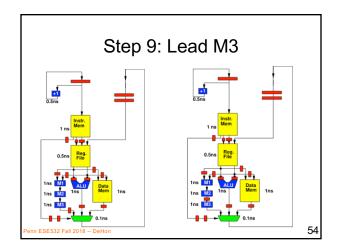

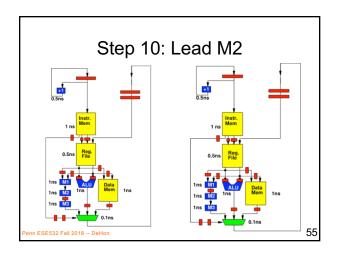

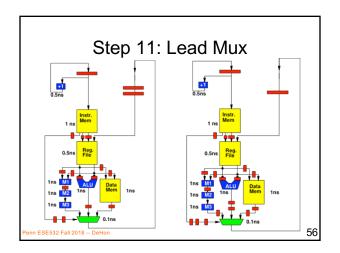

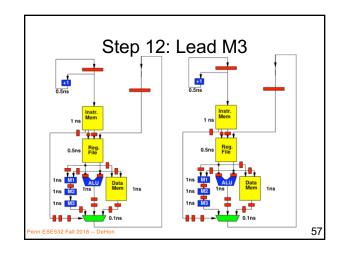

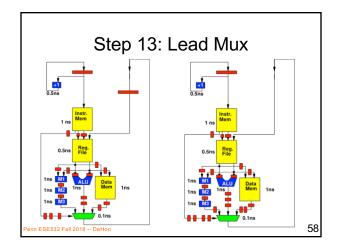

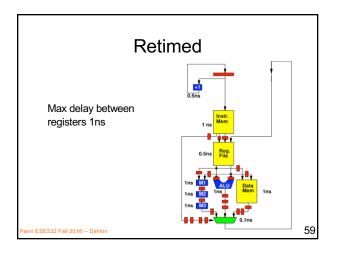

## **Deterministic Pipelines**

- Not how ARM, Intel (371, 501) processor are piplined

- Those include operations that make timing variable

- dynamic data hazards, branch speculation

- Here, data becomes available after a predictable time

- Branches take effect at a fixed time

Likely delayed

- Schedule to delays to get correct data

# Big Ideas:

- Real-Time applications demand different discipline from best-effort tasks

- Look more like synchronous circuits and hardware discipline

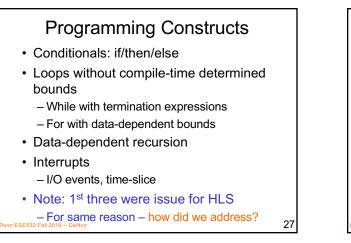

- Avoid or use care with variable delay programming constructs

- Can sequentialize, like processor

But must avoid/rethink typical processor common-case optimizations

- Offline calculate static schedule for computation and sharing