# ESE532: System-on-a-Chip Architecture

Day 5: September 21, 2020 **Dataflow Process Model**

nn ESE532 Fall 2020 -- DeHon

## Today

**Dataflow Process Model**

- Terms (part 1)

- Issues

- Abstraction

- Performance Prospects (part 2)

- · Basic Approach

- As time permits (part 3)

- Dataflow variants

- Motivations/demands for variants

2

# Message

- · Parallelism can be natural

- · Expression can be agnostic to substrate

- Abstract out implementation details

- Tolerate variable delays may arise in implementation

- · Divide-and-conquer

- Start with coarse-grain streaming dataflow

- · Basis for performance optimization and parallelism exploitation

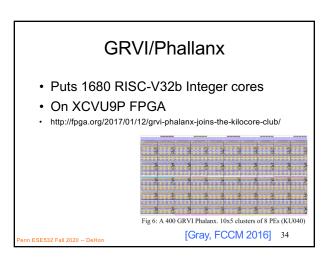

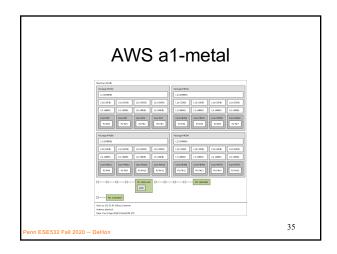

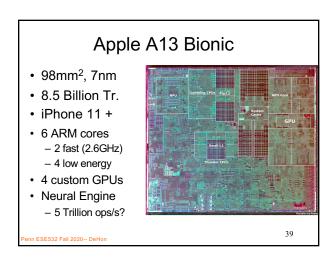

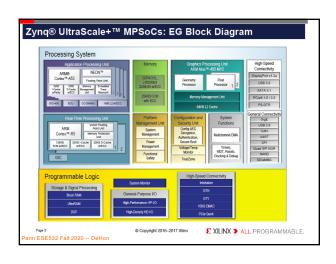

# Programmable SoC Implementation Platform for innovation - This is what you target (avoid NRE) - Implementation vehicle

# Reminder Goal: exploit parallelism on heterogeneous PSoC to achieve desired performance (energy) nn ESE532 Fall 2020 -- DeHon

#### Term: Process

- · Abstraction of a processor

- · Looks like each process is running on a separate processor

- · Has own state, including

- Program Counter (PC)

- Memory

- Input/output

- · May not actually run on processor

- Could be specialized hardware block

- May share a processor

#### **Thread**

- Has a separate locus of control (PC)

- May share memory (contrast process)

- Run in common address space with other threads

- May not actually run on processor

- Could be specialized hardware block

- May share a processor

nn ESE532 Fall 2020 -- DeHon

#### **Process**

- · Processes (threads) allow expression of independent control

- · Convenient for things that advance independently

- · Process (thread) is the easiest way to express some behaviors

- Easier than trying to describe as a single process

- Can be used for performance optimization to improve resource utilization

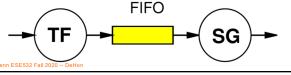

#### Preclass 2

- Average time for TF, SG?

- 1 cycle 99% of time, 100 cycles 1% of time

- Throughput no FIFO?

- Hint: what must wait on TF miss? SG miss?

- Throughput with FIFO?

- How is FIFO changing?

- What benefit from FIFO and processes?

#### Preclass 2

- · Independent probability of miss

- $-P_f, P_q$

- Concretely

- 1 cycle in map

- 100 run function and put in map

- · If each runs independently (in isolation)

- T~= 1\*(1-P)+P\*100

- · If run together in lock step

- Either can stall: P=P<sub>f</sub>+P<sub>a</sub>-P<sub>f</sub>P<sub>a</sub>

- T~= 1\*(1-P)+(P)\*100

11

# Model (from Day 4) Communicating Threads

- Computation is a collection of sequential/control-flow "threads"

- · Threads may communicate

- Through dataflow I/O

- (Through shared variables)

- · View as hybrid or generalization

- CSP Communicating Sequential Processes → canonical model example

ESE532 Fall 2020 -- DeHor

#### Issues

- Communication how move data between processes?

- What latency does this add?

- Throughput achievable?

- Synchronization how define how processes advance relative to each other?

- Determinism for the same inputs, do we get the same outputs?

Penn ESE532 Fall 2020 -- DeHon

13

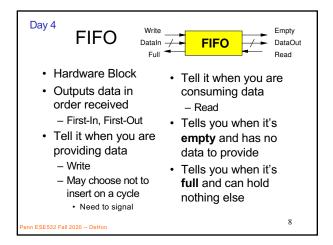

## Today's Stand

- · Communication FIFO-like channels

- Synchronization dataflow with FIFOs

- Determinism how to achieve

- ...until you must give it up.

Penn ESE532 Fall 2020 -- DeHon

14

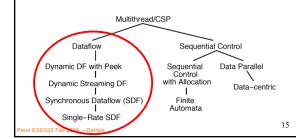

#### **Dataflow Process Model**

### Operation/Operator

- Operation logical computation to be performed

- A process that communicates through dataflow inputs and outputs

- Operator physical block that performs an Operation

- E.g. processor, hardware block

Penn ESE532 Fall 2020 -- DeHon

16

#### Dataflow / Control Flow

#### Dataflow

- Program is a graph of operations

- Operation consumes tokens and produces tokens

- All operations run concurrently

- All processes

nn ESE532 Fall 2020 -- DeHon

#### Control flow (e.g. C)

- Program is a sequence of operations

- Operation reads inputs and writes outputs into common store

- One operation runs at a time

- defines successor

17

Day 4

Day 4

#### Token

- · Data value with presence indication

- May be conceptual

- · Only exist in high-level model

- Not kept around at runtime

- Or may be physically represented

- · One bit represents presence/absence of data

Penn ESE532 Fall 2020 -- DeHon

18

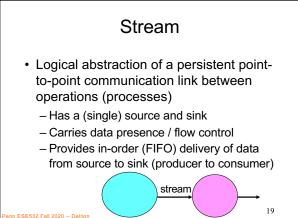

#### Streams

- · Captures communications structure

- Explicit producer→consumer link up

- · Abstract communications

- Physical resources or implementation

- Delay from source to sink

- Contrast

- C: producer->consumer implicit through memory

- Verilog/VHDL: cycles visible in implementation

- (can add **on top of** either C or Verilog)

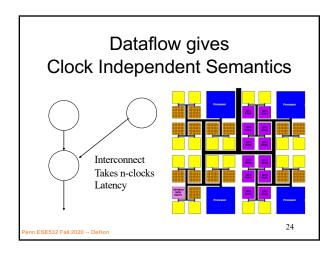

# Variable Delay Source to Sink

· How would placement of source and sink operator impact delay?

· How could sharing of interconnect between source and sink impact delay?,

# **Communication Latency** Once map to multiple processors Need to move data between processors That costs time

# Day 3 **On-Chip Delay** · Delay is proportional to distance travelled · Make a wire twice the length - Takes twice the latency to traverse - (can pipeline) Modern chips - Run at 100s of MHz to GHz - Take 10s of ns to cross the chip 23 nn ESE532 Fall 2020 -- DeHon

#### **Dataflow Process Network**

- · Collection of Operations

- · Connected by Streams

- · Communicating with Data Tokens

- (CSP restricted to stream communication)

25

Penn ESE532 Fall 2020 -- DeHo

# **Dataflow Abstracts Timing**

- · Doesn't say

- on which cycle calculation occurs

- · Does say

- What order operations occur in

- How data interacts

- · i.e. which inputs get mixed together

- Permits

- Scheduling on different # and types of resources

- Operators with variable delay

- Variable delay in interconnect

26

# Dataflow Graphs Parallel Performance Prospect

Part 2

enn ESE532 Fall 2020 -- DeHon

27

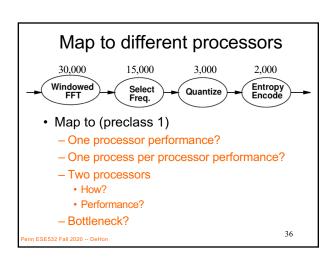

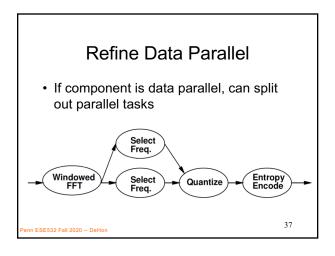

# Some Task Graphs Windowed Select Quantize Entropy Encode FFT Scale Filter Differentiate Compresss Sensor 1 Control Motor 1 Sensor 2 Build Plan Control Moter 2 Penn ESE532 Fall 2020 - DeHon

# Synchronous Dataflow (SDF) with fixed operators

- · Particular, restricted form of dataflow

- · Each operation

- Consumes a fixed number of input tokens

- Produces a fixed number of output tokens

- Operator performs fixed number of operations (in fixed time)

- When full set of inputs are available

- · Can produce output

- Can fire any (all) operations with inputs

nn ESE532 Fall available at any point in time

29

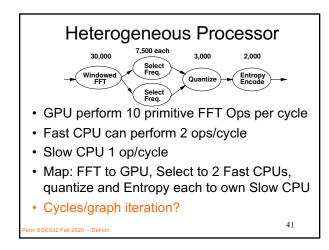

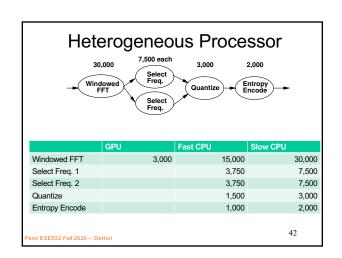

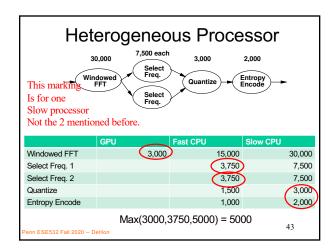

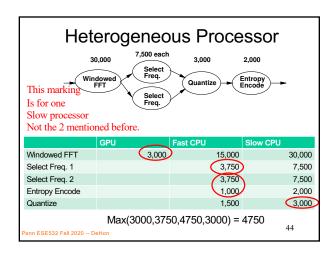

# SDF Operator FFT • 1024 inputs • 1024 outputs • 10,240 multiplies • 20,480 adds • (or 30,720 primitive operations) Windowed FFT Select Quantize Entropy Encode Pean ESE532 Fall 2020 - Delton

#### **Processor Model**

- Simple (for today's lecture)

- Assume one primitive operation per cycle

- · Could embelish

- Different time per operation type

- E.g. adds: 1 cycle, multiply: 3 cycles

- Multiple memories with different timings

Penn ESE532 Fall 2020 -- DeHon

31

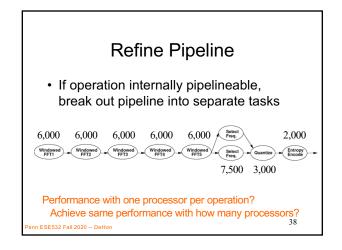

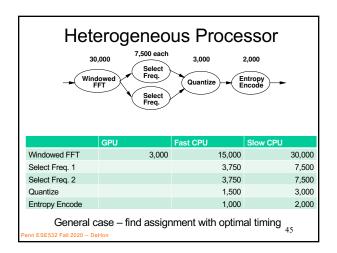

# Time for Graph Iteration on Processors

- Single processor  $T_{one} = \sum_{i} Nops_{i}$

- One processor per Operation (process)

□ T<sub>each</sub> = max(Nop<sub>1</sub>,Nop<sub>2</sub>,Nop<sub>3</sub>,...)

- General

$$T_{map} = max \left( \sum_{i} c(1, i) \times Nops_{i}, \sum_{i} c(2, i) \times Nops_{i}, \sum_{i} c(3, i) \times Nops_{i}, \dots \right)$$

$$c(x, y) - 1 \text{ if Processor x runs task y } 32$$

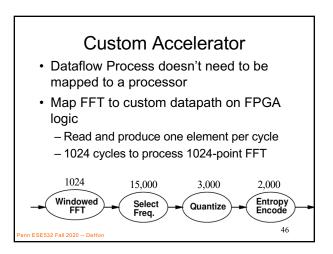

# Operations

- Can be implemented on different operators with different characteristics

- Small or large processor

- Hardware unit

- Different levels of internal

- Data-level parallelism

- · Instruction-level parallelism

- · Pipeline parallelism

- · May itself be described as

- Dataflow process network, sequential,

- hardware register transfer language

#### **Streams**

- Stream: logical communication link

- · How might we implement:

- Two threads running on a single processor (sharing common memory)?

- Two processes running on different processors on the same chip?

- Two processes running on different hosts

- E.g. one at Penn, one on Amazon cloud

Penn ESE532 Fall 2020 -- DeHon

47

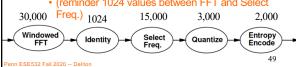

### Add Delay

- · What does it do to computation if add an operation that copies inputs to outputs with some latency?

- Impact on function?

- What is throughput impact when Identity operation has

- Latency 10, throughput 1 value per cycle?

- (reminder 1024 values between FFT and Select

## Semantics (meaning)

- · Need to implement semantics

- -i.e. get same result as if computed as indicated

- · But can implement any way we want

- That preserves the semantics

- Exploit freedom of implementation

nn ESE532 Fall 2020 -- DeHoi

50

# **Basic** Approach

51

# Approach (1)

- · Identify natural parallelism

- · Convert to streaming flow

- Initially leave operations in software

- Focus on correctness

- · Identify flow rates, computation per operator, parallelism needed

- Refine operations

- Decompose further parallelism?

- E.g. data parallel split, ILP implementations

- model potential hardware

# Approach (2)

- · Refine coordination as necessary for implementation

- · Map operations and streams to resources

- Provision hardware

- Scheduling: Map operations to operators

- Memories, interconnect

- · Profile and tune

• Refine

53

#### **Dataflow Variants**

#### Part 3:

(coverage here depends on time available)

# **Turing Complete**

- Can implement any computation describable with a Turing Machine

- (theoretical model of computing by Alan Turing)

- Turing Machine captures our notion of what is computable

- If it cannot be computed by a Turing Machine, we don't know how to compute it

Penn ESE532 Fall 2020 -- DeHon

55

#

Penn ESE532 Fall 2020 -- DeHon

DDF blocking

56

# Synchronous Dataflow (SDF) with fixed operators

- · Particular, restricted form of dataflow

- · Each operation

- Consumes a fixed number of input tokens

- Produces a fixed number of output tokens

- Operator performs fixed number of operations (in fixed time)

- When full set of inputs are available

- · Can produce output

- Can fire any (all) operations with inputs

- available at any point in time

57

# Synchronous Dataflow (SDF)

- · Particular, restricted form of dataflow

- Each operation

- Consumes a fixed number of input tokens

- Produces a fixed number of output tokens

- (can take variable computation for operator)

- When full set of inputs are available

- · Can produce output

- Can fire any (all) operations with inputs available at any point in time

58

# Multirate Synchronous Dataflow

- · Rates can be different

- Allow lower frequency operations

- Communicates rates to tools

- Use in scheduling, provisioning

- Rates must be constant

- · Data independent

# **Dynamic Dataflow**

- · (Less) restricted form of dataflow

- Each operation

- Conditionally consume input based on data value

- Conditionally produce output based on data value

- When full set of inputs are available

- Can (optionally) produce output

- Can fire any (all) operations with data-specified necessary inputs available at any point in time

Penn ESE532 Fall 2020 -- DeHon

# **Blocking**

- Key to determinism: behavior doesn't depend on timing

- Cannot ask if a token is present

- If (not\_empty(in))

- Out.put(3);

- Else

- Out.put(2);

Penn ESE532 Fall 2020 -- DeHon

61

#

# Motivations and Demands for Options

Time Permitting

enn ESE532 Fall 2020 -- DeHon

63

## Variable Delay Operators

- Why might a multiplier have variable delay?

- Hint: consider shift-and-add multiply

- Why might square root have variable delay?

- Why might memory lookup on a processor have variable delay?

Penn ESE532 Fall 2020 -- DeHon

64

66

# Variable Delay Operators

- Operators with Variable Delay

- Cached memory or computation

- Shift-and-add multiply

- Iterative divide or square-root

nn ESE532 Fall 2020 -- DeHon

65

# GCD (Preclass 3)

- What is delay of GCD computation?

- while(a!=b)

- t=max(a,b)-min(a,b)

- a=min(a,b)

- b=t

- return(a);

F-II 0000 P-II--

# **Dynamic Rates?**

- · What is implication of static rates

- on compression?

- Filtering?

- (e.g. discard all spam packets)

Penn ESE532 Fall 2020 -- DeHon

67

71

# **Dynamic Rates?**

- · Static Rates limiting

- Compress/decompress

- Lossless

- · Even Run-Length-Encoding

- Filtering

- · Discard all packets from spamRus

- Anything data dependent

Penn ESE532 Fall 2020 - DeHon

68

## When non-blocking necessary?

- What are cases where we need the ability to ask if a data item is present?

- Consider an IP packet router:

#### Non-Blocking

- · Removed model restriction

- Can ask if token present

- · Gained expressive power

- Can grab data as shows up

- · Weaken our guarantees

- Possible to get non-deterministic behavior

Penn ESE532 Fall 2020 -- DeHon

70

# **Process Network Roundup**

| Model                        | Deterministic<br>Result | Deterministic<br>Timing | Turing<br>Complete |

|------------------------------|-------------------------|-------------------------|--------------------|

| SDF+fixed-delay operators    | Y                       | Y                       | N                  |

| SDF+variable delay operators | Y                       | N                       | N                  |

| DDF blocking                 | Y                       | N                       | Y                  |

| DDF non-<br>blocking         | N                       | N                       | Y                  |

nn ESE532 Fall 2020 -- DeHon

# Big Ideas

- Capture gross parallel structure with Process Network

- Use dataflow synchronization for determinism

- Abstract out timing of implementations

- Give freedom of implementation

- Exploit freedom to refine mapping to optimize performance

- Minimally use non-determinism as necessary

# Admin

- Remember feedback

- Today's lecture and HW2

- Reading for Day 6 on web

- HW3 due Friday

- Implementing multiprocessor solutions on homogeneous (ARM) processor cores

Penn ESE532 Fall 2020 -- DeHon