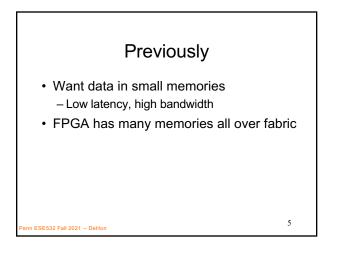

## Previously

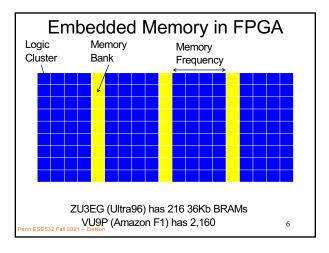

- Want data in small memories – Low latency, high bandwidth

- FPGA has many memories all over fabric

- · Want C arrays in small memories

- Partitioned so can perform enough reads (writes) in a cycle to avoid memory bottleneck

7

9

### Penn ESE532 Fall 2021 -- DeHon

ESE532 Fall 2021 -- DeHo

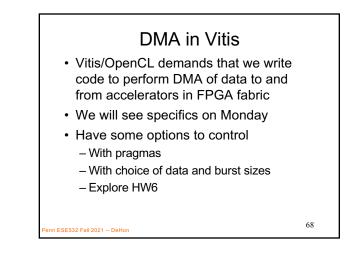

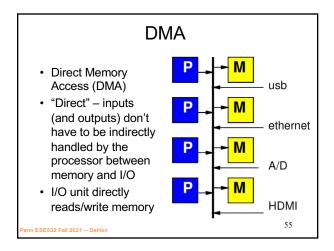

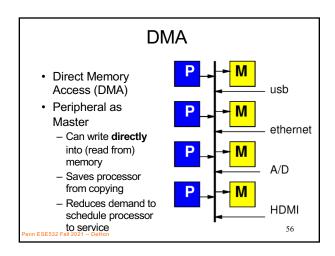

# Today Interconnect Infrastructure (Part 1) Peripherals (Part 2) Data Movement Threads (Part 3) DMA -- Direct Memory Access (Part 4)

ann ESE532 Fall 2021 -- DeHo

ESE532 Fall 2021 -- DeH

8

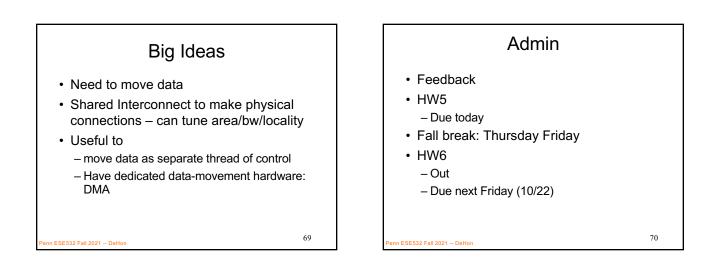

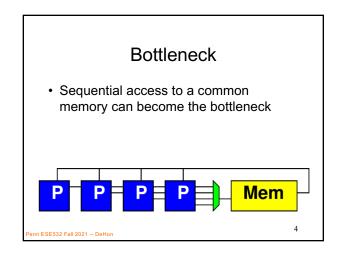

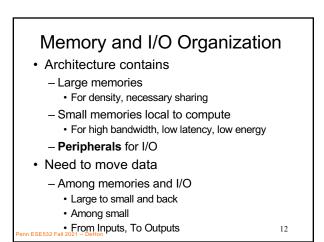

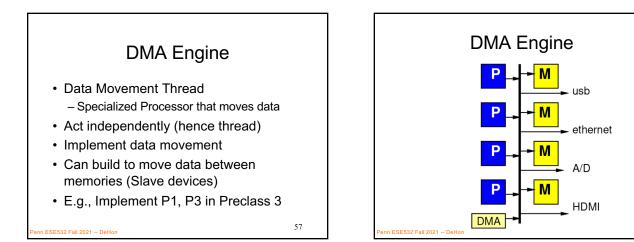

## Message

- · Need to move data

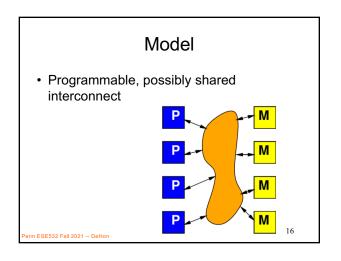

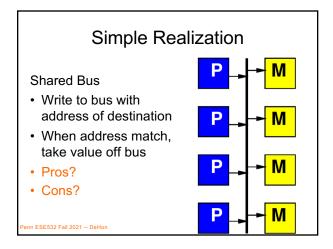

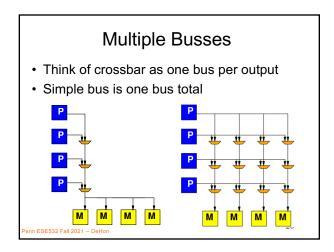

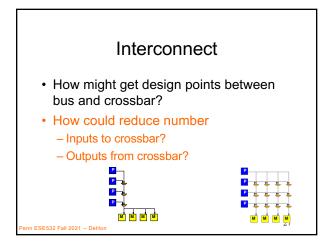

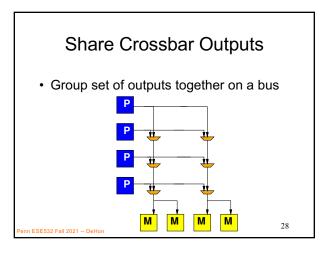

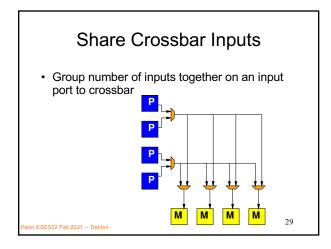

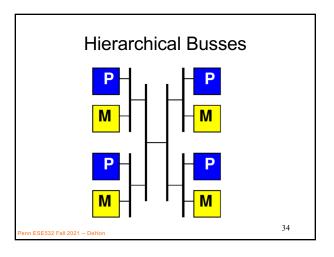

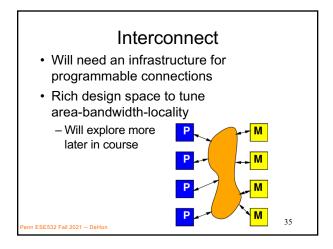

- Often use shared interconnect to make physical connections

- Useful to move data as separate thread of control

- Dedicating a processor is inefficient

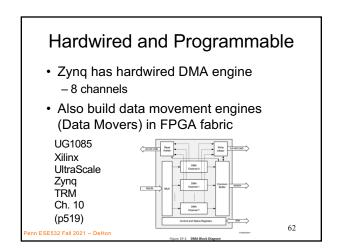

- Useful to have dedicated data-movement hardware: Direct Memory Access (DMA)

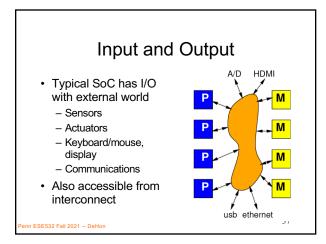

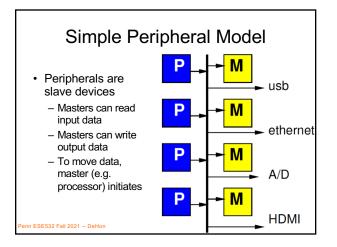

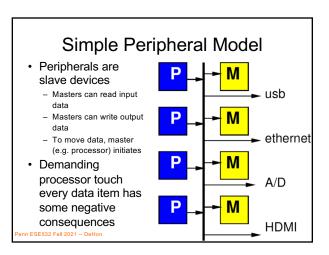

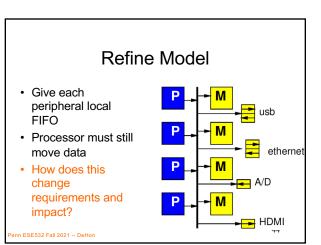

## "On the edge (or perhiphery) of something" Peripheral device – device used to put information onto or get information off of a computer E.g. Keyboard, mouse, modem, USB flash drive, ...

**Term:** Peripheral

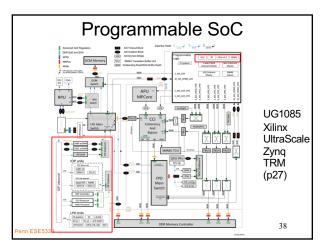

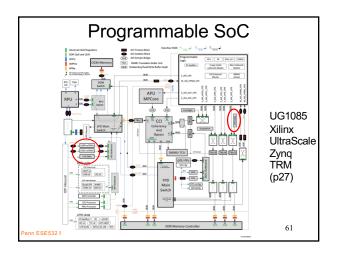

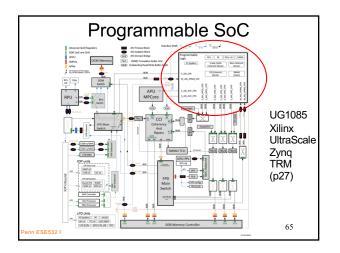

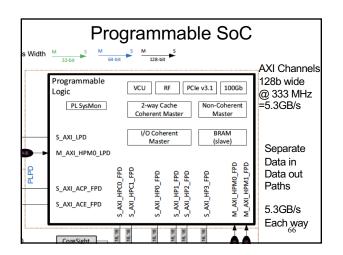

Programmable SocImage: Distribution of the state of the state

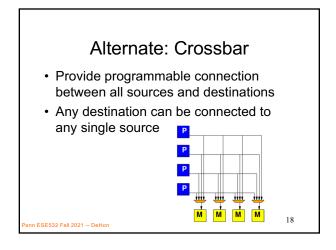

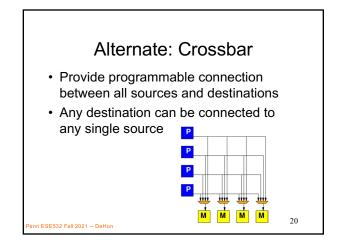

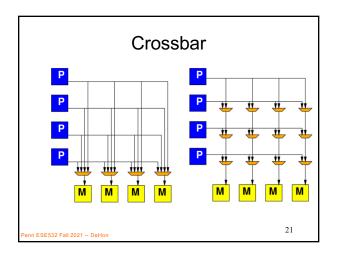

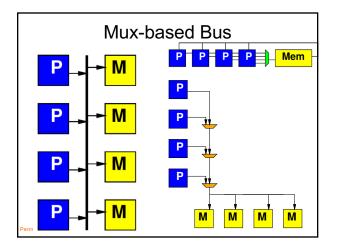

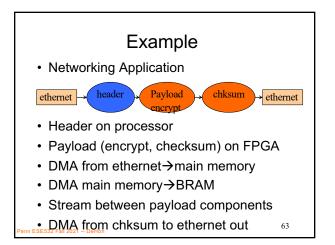

## How move data?

- Abstractly, using stream links.

- Connect stream between producer and consumer.

13

• Ideally: dedicated wires

enn ESE532 Fall 2021 -- DeHon

## **Timing Demands**

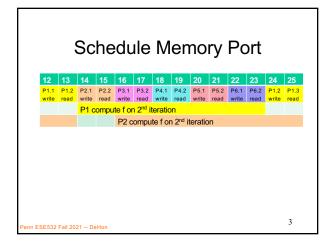

- · Must read each input before overwritten

- Must write each output within real-time window

- Must guarantee processor scheduled to service each I/O at appropriate frequency

- How many cycles between 32b input words for 1Gb/s network and 32b, 1GHz processor?

- Consider input data shifted into register 1b per ns

Must read out 32b register before overwritten

43

ann ESE532 Fall 2021 -- DeHon

##

nn ESE532 Fall 2021 -- Deno

| s Width M Solution So |                                    |                                                                     |                           |                                                                     |                      |                            |                                                                          |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|---------------------------------------------------------------------|---------------------------|---------------------------------------------------------------------|----------------------|----------------------------|--------------------------------------------------------------------------|--|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Programmable<br>Logic<br>PL SysMon |                                                                     | U<br>2-way Ca<br>herent M | ache                                                                |                      | 100Gb<br>Coherent<br>aster | AXI Channels<br>128b wide<br>@ 333 MHz<br>=5.3GB/s<br>Per direction      |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | S_AXI_LPD<br>M_AXI_HPM0_LPD        |                                                                     | /O Cohe<br>Maste          | er                                                                  | (s                   | Mu_FPD War                 | Per channel<br>S_ act as<br>master for PL<br>(connects to<br>slave ports |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | S_AXI_ACP_FPD<br>S_AXI_ACE_FPD     | 16.16         S_AXI_HPC0_FPD           16.16         S_AXI_HPC1_FPD | 16, 16 S_AXI_HP0_FPD      | 16. 16         S_AXI_HP1_FPD           16. 16         S_AXI_HP2_FPD | 16, 16 S_AXI_HP3_FPD | M_AXI_HPM0_FPD             | in PS)<br>M_as slave<br>for PL                                           |  |  |