# ESE532: System-on-a-Chip Architecture

Day 24: November 29, 2021 Real Time

n ESE532 Fall 2021 -- DeHor

ESE532 Fall 2021 -- DeH

# Penn

3

### Message

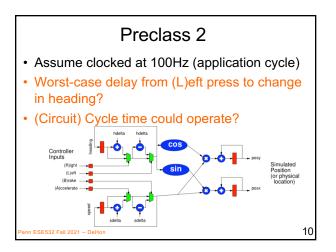

- Real-Time applications demand different discipline from best-effort tasks

- · Look more like synchronous circuits

- · Can sequentialize, like processor

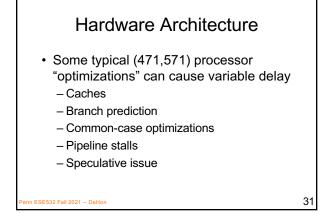

- But must avoid/rethink typical generalpurpose processor common-case optimizations

## Real Time

- "Real" refers to physical time – Connection to Real or Physical World

- · Contrast with "virtual" or "variable" time

- Handles events with absolute guarantees on timing

# Real-Time Tasks

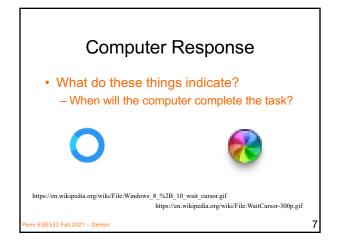

- What timing guarantees might you like for the following tasks?

- Turn steering wheel on a drive-by-wire car

Delay to recognized and car turns

- Self-driving car detects an object in its path

- Delay from object appearing to detection

- Pacemaker stimulates your heart

- Video playback (frame to frame delay)

#### Penn ESE532 Fall 2021 -- DeHon

- Produce new frame every 30 ms

- $-\operatorname{Both}:$  schedule to act and complete action

- Bounded response time

- Respond to keypress within 20 ms

- Detect object within 100 ms

- Return search results within 200 ms

nn ESE532 Fall 2021 -- DeHon

ESE532 Fall 2021 -- DeH

enn ESE532 Fall 2021 -- DeHon

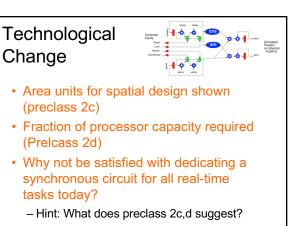

– Can implement audio in a small fraction of its computational throughput capacity

#### HW/SW Co-Design

14

- Computer Engineers know can implement anything as hardware or software

- Want freedom to move between hardware and software to meet requirements

- Performance, costs, energy

nn ESE532 Fall 2021 -- DeHon

13

15

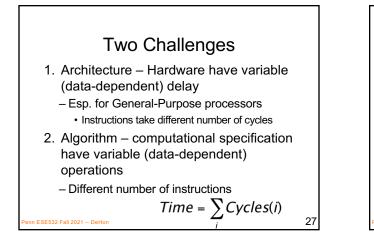

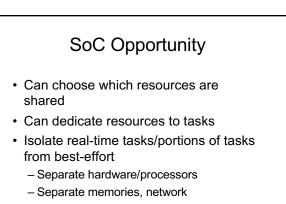

# **Real-Time Challenge**

- Meet real-time demands / guarantees

Economically using programmable architectures

- Sequentialize and share resources with deterministic, guaranteed timing

- Spatial (all hardware, HLS synthesized) implementations are good at meeting real-time guarantees, but may be bigger than necessary

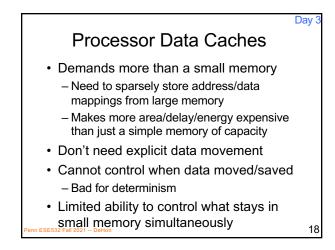

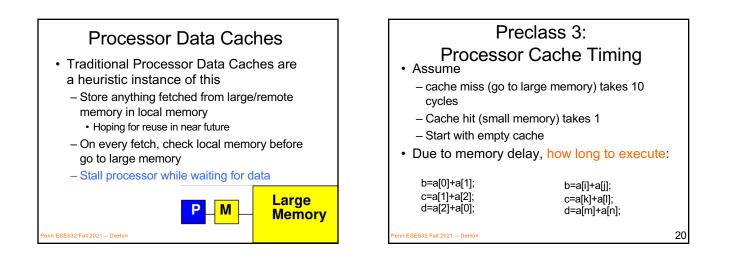

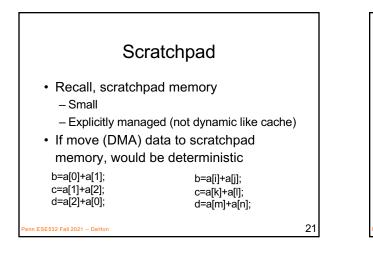

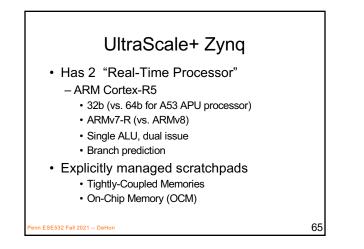

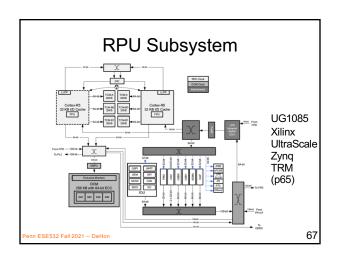

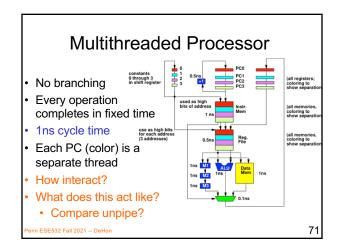

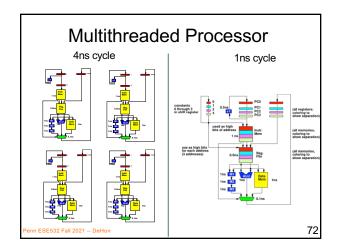

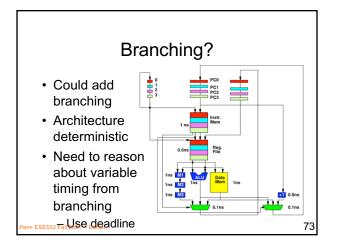

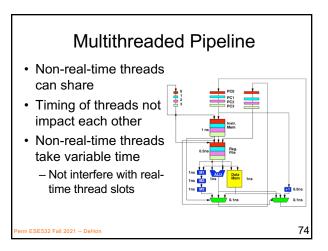

# What can we do to make architecture more deterministic?

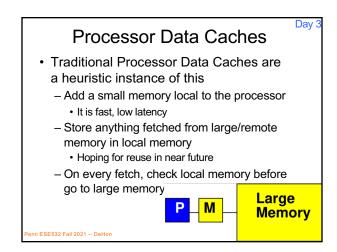

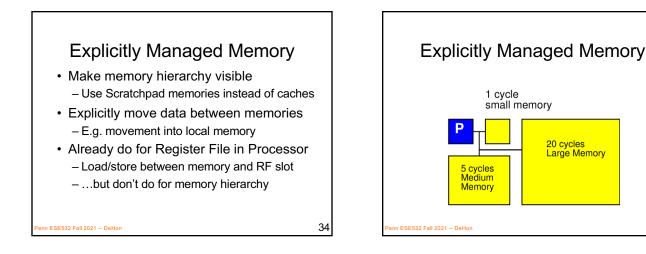

- · Explicitly managed memory

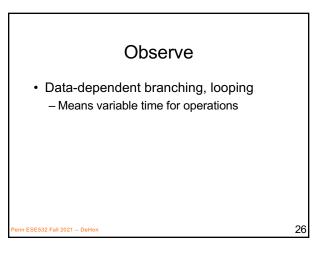

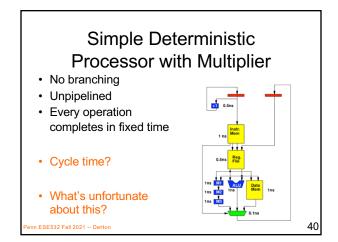

- Eliminate Branching (too severe?)

- Unpipelined processors

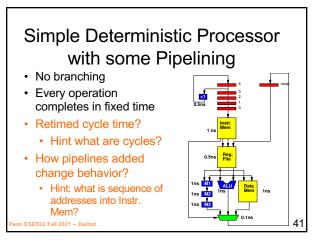

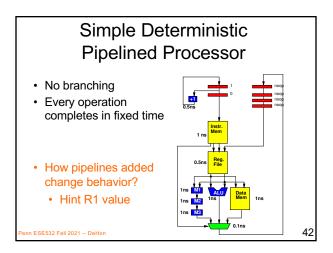

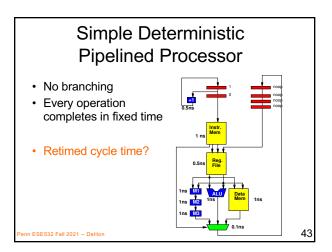

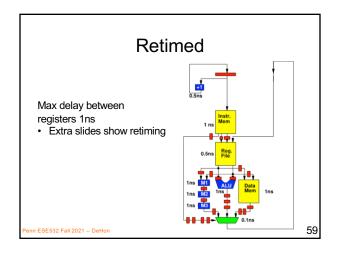

- Fixed-delay pipelines

- Offline-scheduled resource sharing

33

35

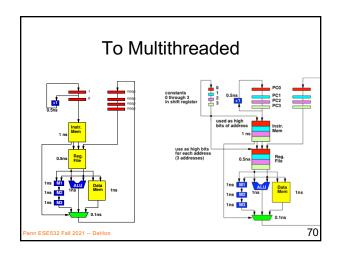

- Multi-threaded

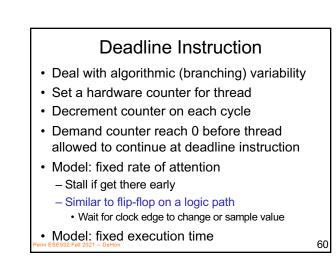

- Deadlines

- n ESE532 Fall 2021 -- DeHon

36

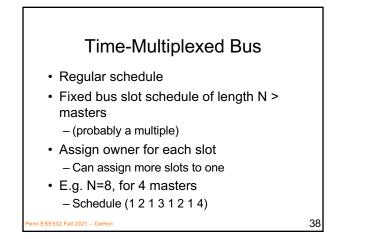

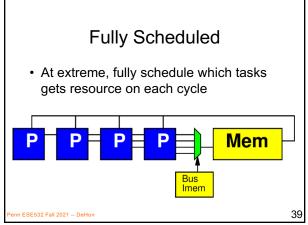

# Offline Schedule Resource Sharing

- Don't arbitrate

- Decide up-front when each shared resource can be used by each thread or processor

- Simple fixed schedule

- Detailed Schedule

- What

- Memory bank, bus, I/O, network link, ...

nn ESE532 Fall 2021 -- DeHon

<section-header>

ESE532 Fall 2021 -- DeHor

# Big Ideas:

- Real-Time applications demand different discipline from best-effort tasks

- Look more like synchronous circuits and hardware discipline

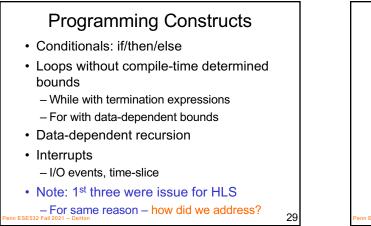

- Avoid or use care with variable delay programming constructs

- Can sequentialize, like processor

But must avoid/rethink typical processor common-case optimizations

- Offline calculate static schedule for computation and sharing