## ...but

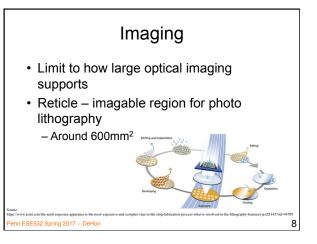

- Limits to how big we can make chips – Manufactures are prepared to create

- Can be reliably manufactured

- $\ldots$  and how small we can make chips

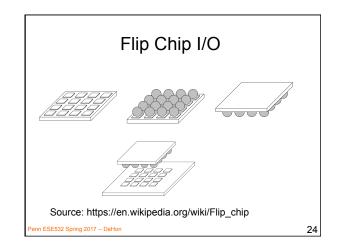

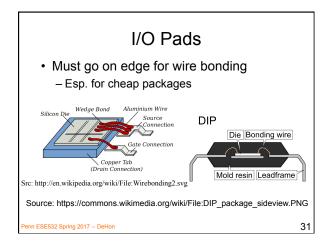

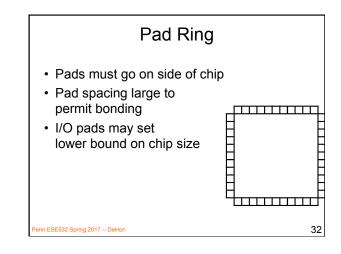

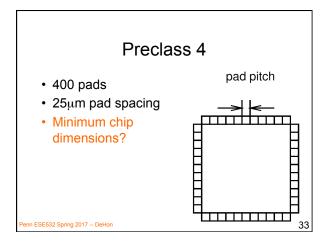

I/O pads

- Cutting/handling/marking

Penn ESE532 Spring 2017 -- DeHon

7

## Zynq Component Estimates

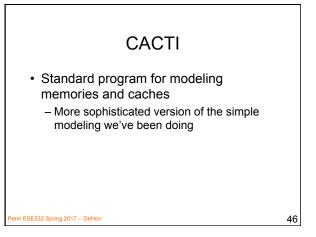

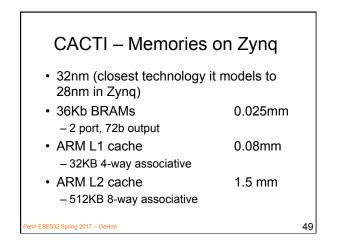

| • 6-LUT                           | 0.0005 mm <sup>2</sup> |

|-----------------------------------|------------------------|

| DSP Block                         | 0.1 mm <sup>2</sup>    |

| 36Kb BRAMs                        | 0.025mm <sup>2</sup>   |

| <ul> <li>ARM L1 cache</li> </ul>  | 0.08mm <sup>2</sup>    |

| <ul> <li>ARM L2 cache</li> </ul>  | 1.5 mm <sup>2</sup>    |

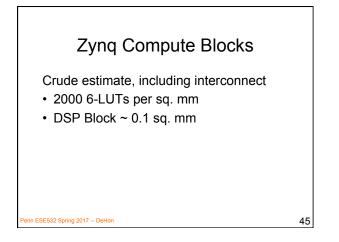

| <ul> <li>ARM Cortex A9</li> </ul> | 1.0 mm <sup>2</sup>    |

|                                   |                        |

|                                   |                        |

| enn ESE532 Spring 2017 – DeHon    | 50                     |

|                                   |                        |

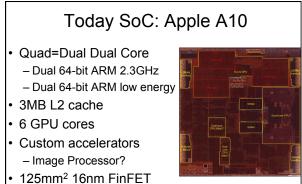

- 3.3B transistors

- enn ESE532 Spring 2017 -- DeHon