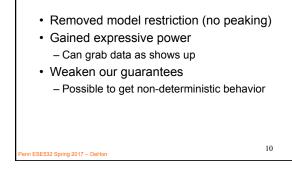

| Process Network Roundup      |                         |                         |                    |

|------------------------------|-------------------------|-------------------------|--------------------|

| Model                        | Deterministic<br>Result | Deterministic<br>Timing | Turing<br>Complete |

| SDF+fixed-delay operators    | Y                       | Y                       | N                  |

| SDF+variable delay operators | Y                       | N                       | N                  |

| DDF no peak                  | Y                       | N                       | Y                  |

| DDF w/ peak                  | N                       | N                       | Y                  |

|                              |                         |                         |                    |

| enn ESE532 Spring 2017 D     | leHon                   |                         | 11                 |

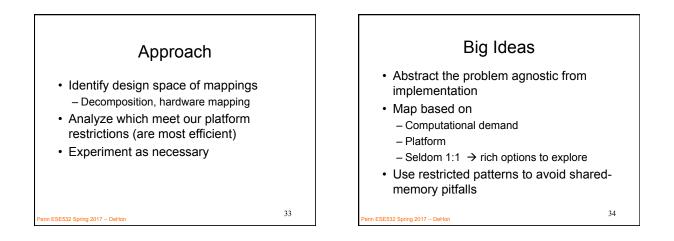

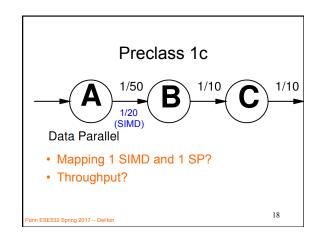

## Approach (1)

- · Identify natural parallelism

- Convert to streaming flow

Initially leave operators software

Focus on correctness

- Identify flow rates, computation per operator, parallelism needed

- Refine operators

- Decompose further parallelism?

- E.g. SIMD changes making hw3

- model potential hardware

- Refine coordination as necessary for implementation

- Map operators and streams to resources

- Provision hardware

- Scheduling: Map operations to operators

14

- Memories, interconnect

## Profile and tune

Penn ESE532 Spring 2017 -- DeHon

13

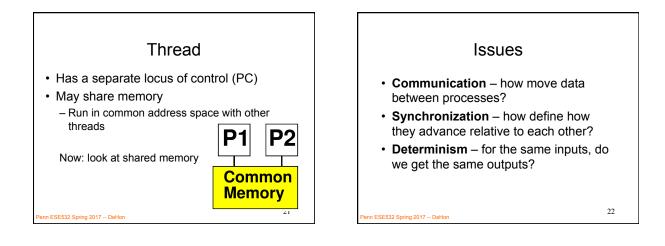

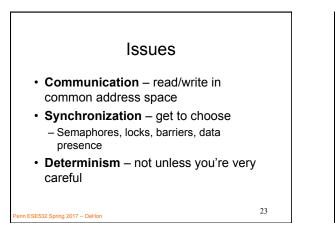

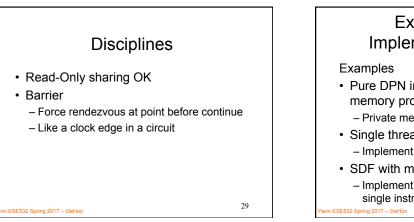

## Expression and Implementation not 1:1

- Pure DPN implemented on sharedmemory processors

- Private memory, implement buffers in SM

- Single threaded DP with conditionals

Implement in multiple threads

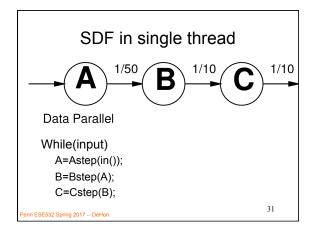

- SDF with many tasks

Implement schedule of operations on

single instruction stream