# ESE 568: Mixed Signal Circuit Design and Modeling

Lec 11: October 7th, 2019 Sampling Circuits (con't), Switched Capacitor Circuits

- Elementary track-and-hold

- Nonidealities (con't)

- First order improvements

- Advanced techniques

- Clock bootstrapping (for reference only)

- Bottom plate sampling

- Switched Capacitor Circuits

- Charge Redistribution Track-and-hold

- Elementary track-and-hold circuit and its nonidealities

- First order improvements to elementary track-andhold (finish today)

- □ kTC noise

- □ Finite acquisition time

- Tracking nonlinearity

- Signal dependent hold instant

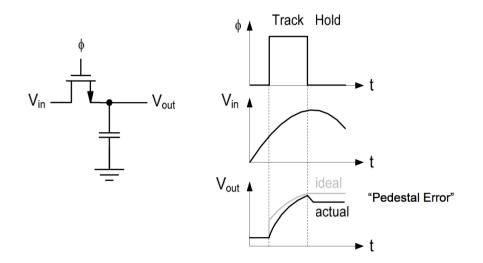

- Charge injection and clock feedthrough

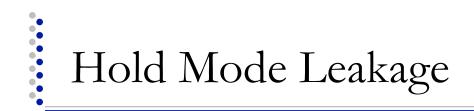

- Hold mode feedthrough and leakage

- Clock jitter

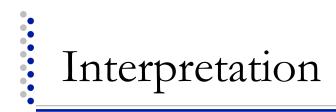

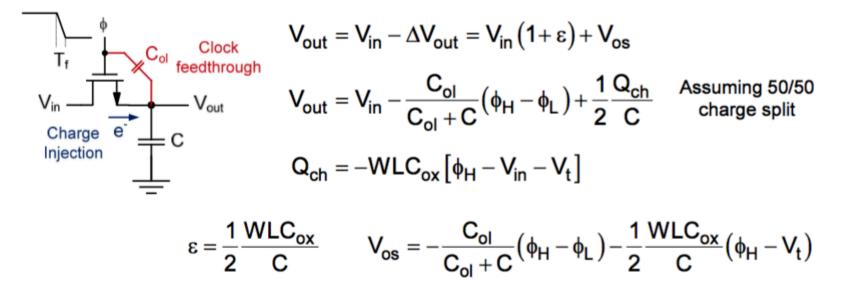

Charge Injection and Clock Feedthrough

- □ Analyze two cases

- Very Large T<sub>f</sub> (slow-gating)

- Very Small T<sub>f</sub> (fast-gating)

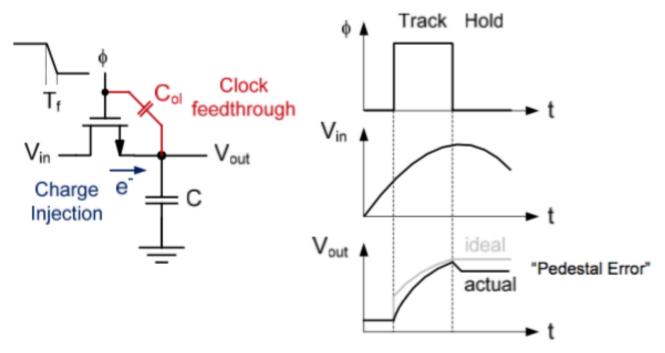

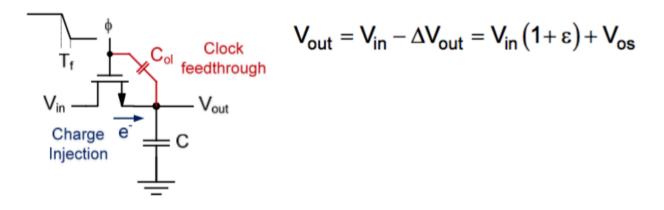

Slow Gating Model for t>t<sub>off</sub>

$$\begin{array}{c} \phi & V_{out} = V_{in} - \Delta V_{out} \\ \hline C_{ol} & Clock \\ \hline feedthrough \\ \hline C \\ \hline C \\ \hline \end{array} \\ \begin{array}{c} V_{out} \\ \hline C \\ \hline \end{array} \\ \begin{array}{c} c \\ \hline \end{array} \\ \end{array} \\ \begin{array}{c} c \end{array} \\ \end{array} \\ \begin{array}{c} c \\ \end{array} \\ \begin{array}{c} c \\ \end{array} \end{array} \\ \begin{array}{c} c \\ \end{array} \end{array} \\ \begin{array}{c} c \\ \end{array} \\ \end{array} \\ \begin{array}{c} c \end{array} \\ \end{array} \\ \end{array} \\ \end{array}$$

\\ \begin{array}{c} c \end{array} \\ \end{array} \\ \end{array} \\ \end{array} \\ \end{array} \\ \end{array} \\ \begin{array}{c} c \end{array} \end{array} \\ \end{array} \\ \end{array} \\ \end{array} \\ \end{array} \\ \end{array} \\ \begin{array}{c} c \end{array} \\ \\ \end{array} \\ \\ \end{array} \\ \end{array} \\ \\ \end{array} \\ \end{array} \\ \\ \end{array} \\ \\ \end{array} \\ \bigg \\ \bigg \\ \\ \end{array} \\ \end{array} \\ \end{array} \\ \\ \end{array} \\ \end{array} \\ \bigg \\ \bigg \\ \\ \end{array} \\ \bigg \\ \\ \end{array} \\ \bigg \\ \\ \end{array} \\ \bigg \\ \\ \end{array} \\ \\ \bigg \\ \bigg \\ \\ \bigg \\ \bigg

• Example:

C=1pF,  $\phi_L$ =0V, V<sub>t</sub>=0.45V, W=20µm, C<sub>ol</sub>'=0.1fF/µm, C<sub>ol</sub>=2fF  $\epsilon = -0.2\%$  V<sub>os</sub> = -0.9mV

- Channel charge cannot change instantaneously

- Resulting surface potential decays via charge flow to source and drain (charge injection)

- Charge divides between source and drain

- This means that in practice split will have dependence on impedances seen on either side of transistors

- Remember: Slightly more charge will go to side with lower impedance (higher capacitance)

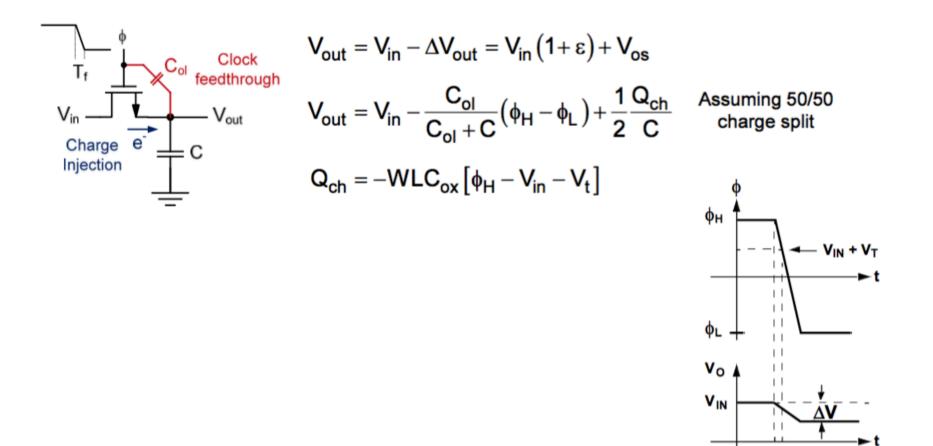

• Example:

C=1pF,

$$\phi_H - \phi_L = 1.8V$$

, V<sub>t</sub>=0.45V, W=20µm, LC<sub>ox</sub>=2fF/µm C<sub>ol</sub>'=0.1fF/µm, C<sub>ol</sub>=2fF

$$\varepsilon = +2\%$$

$V_{os} = -30.6mV$

• Example:

C=1pF,

$$\phi_{H}-\phi_{L}$$

=1.8V, V<sub>t</sub>=0.45V, W=20µm, LC<sub>ox</sub>=2fF/µm C<sub>ol</sub>'=0.1fF/µm, C<sub>ol</sub>=2fF

$$\epsilon = +2\%$$

$V_{os} = -30.6mV$ Slow gating $\epsilon = -0.2\%$  $V_{os} = -0.9mV$

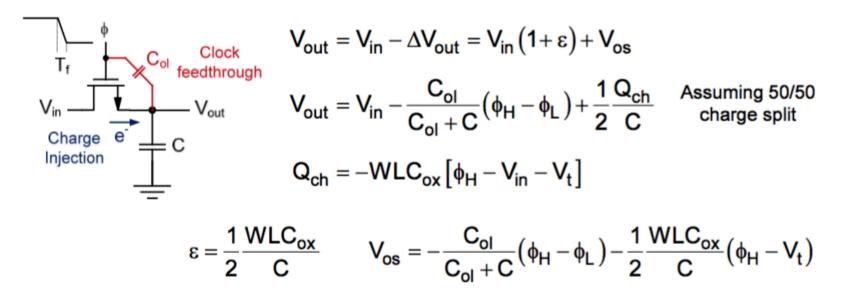

Transition Fast/Slow Gating

- $\begin{tabular}{ll} \hline $\mathbf{\mathcal{E}}$ & and $|V_{OS}|$ decrease as the clock fall time increases and approaches the limit of slow gating $\mathbf{\mathcal{E}}$ & and $|V_{OS}|$ approaches the limit of slow gating $\mathbf{\mathcal{E}}$ & and $|V_{OS}|$ & approaches the limit of slow gating $\mathbf{\mathcal{E}}$ & and $|V_{OS}|$ & approaches the limit of slow gating $\mathbf{\mathcal{E}}$ & approaches the limit of slow gating $\mathbf{\mathcal{E}}$ & and $|V_{OS}|$ & approaches the limit of slow gating $\mathbf{\mathcal{E}}$ & approaches the limit of $\mathbf{\mathcal{E}}$ & approaches the limit $\mathbf{\mathcal{E}}$ & appro$

- Practical cases are closer to fast-gating side

Impact of Technology Scaling

Charge injection error to speed ratio benefits from short channels and increases in mobility

$$\Delta V \cong \frac{1}{2} \frac{Q_{ch}}{C} \qquad \frac{1}{2f_s} = \frac{T_s}{2} = N \cdot RC$$

$$R \cong \frac{1}{\mu C_{ox}} \frac{W}{L} (V_{GS} - V_t)$$

Impact of Technology Scaling

Charge injection error to speed ratio benefits from short channels and increases in mobility

$$\Delta V \cong \frac{1}{2} \frac{Q_{ch}}{C} \qquad \frac{1}{2f_s} = \frac{T_s}{2} = N \cdot RC$$

$$R \cong \frac{1}{\mu C_{ox}} \frac{W}{L} \left( V_{GS} - V_t \right) = \frac{L^2}{\mu Q_{ch}}$$

#### First order improvements

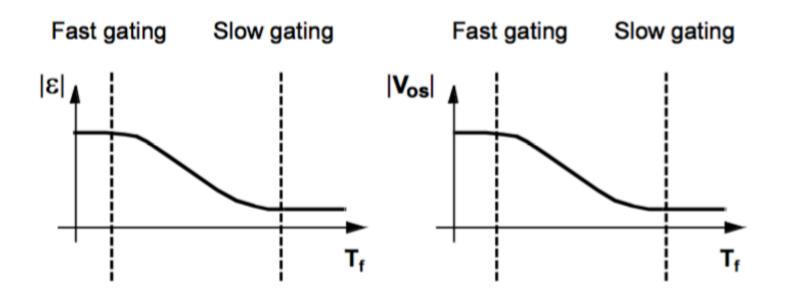

- CMOS switch

- Try to balance nonidealities of nMOS with parallel pMOS

- □ Charge cancelation

- Try to cancel charge injection with dummy switch

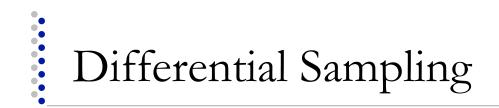

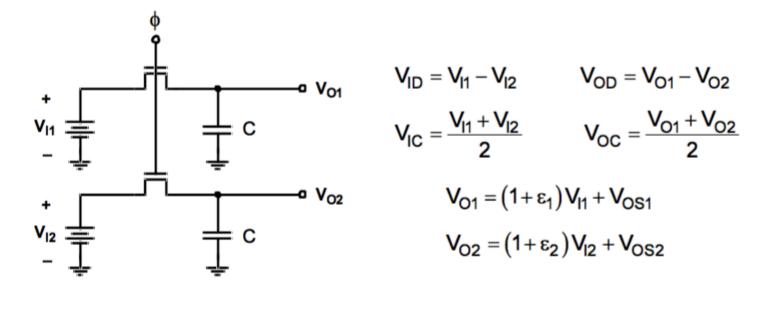

- Differential Sampling

- Differential signaling to suppress offset

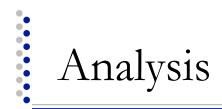

CMOS Switch Resistance

- In principle, adding PMOS helps with signal dependent R<sub>on</sub> in track mode

- Parallel resistance of MOS devices roughly constant

$$\begin{split} R &\cong \frac{1}{\mu_{n}C_{ox}\left[\frac{W}{L}\right]_{n}\left(V_{GSn} - V_{tn}\right)} \left| \begin{array}{c} 1\\ \mu_{p}C_{ox}\left[\frac{W}{L}\right]_{p}\left(\left|V_{GSp}\right| - \left|V_{tp}\right|\right) \end{array} \right. \\ R &\cong \frac{1}{\mu_{n}C_{ox}\left[\frac{W}{L}\right]_{n}\left(V_{DD} - V_{tn}\right) - \left(\mu_{n}C_{ox}\left[\frac{W}{L}\right]_{n} - \mu_{p}C_{ox}\left[\frac{W}{L}\right]_{p}\right)v_{in} - \mu_{p}C_{ox}\left[\frac{W}{L}\right]_{p}\left|V_{tp}\right| \\ R &\cong \frac{1}{\mu_{n}C_{ox}\left[\frac{W}{L}\right]_{n}\left(V_{DD} - V_{tn} - \left|V_{tp}\right|\right)} \quad \text{if} \quad \mu_{n}\left[\frac{W}{L}\right]_{n} = \mu_{p}\left[\frac{W}{L}\right]_{p} \end{split}$$

- □ Independent of  $V_{in}$  → too good to be true!

- Missing factors

- Backgate effect

- Short channel effects

Design

• Size P/N ratio to minimize change in R over input range

PMOS bring limited benefit unless the input signal range is large or centered near V<sub>DD</sub>

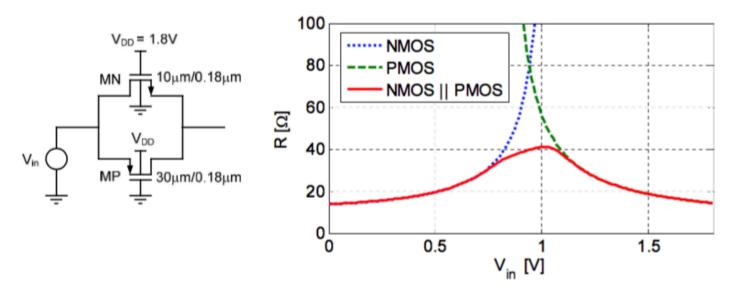

Charge Cancellation: CMOS Switch

- Partial cancellation of offset error

- Assuming fast gating, 50/50 charge split and  $W_nL_n = W_pL_p$

• Charges full cancel for  $V_{in} = (V_H - V_L)/2 = V_{DD}/2$  and  $V_{tn} = -V_{tp}$

• Still signal dependent residual injection

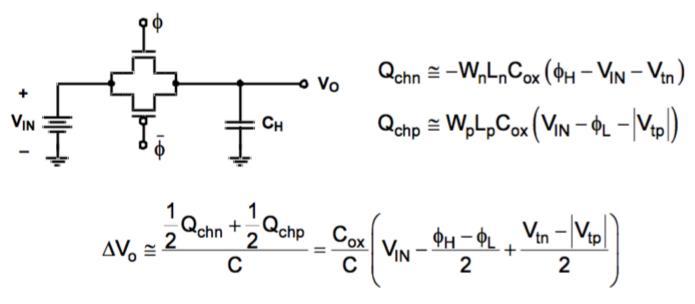

Charge Cancellation: Dummy Switch

[Eichenberger and Guggenbűhl, JSSC 8/89]

- Cancellation is never perfect, since channel charge of M1 will not be 50/50 split

- If R<sub>s</sub> small, most of charge will flow toward the input voltage source

- $\sim 80\%$  cancellation

- Not precision technique, just a partial clean-up attempt

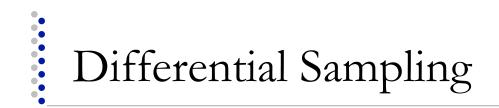

$$V_{ID} = V_{I1} - V_{I2} \qquad V_{OD} = V_{O1} - V_{O2}$$

$$V_{IC} = \frac{V_{I1} + V_{I2}}{2} \qquad V_{OC} = \frac{V_{O1} + V_{O2}}{2}$$

$$V_{O1} = (1 + \epsilon_1)V_{I1} + V_{OS1}$$

$$V_{O2} = (1 + \epsilon_2)V_{I2} + V_{OS2}$$

$$V_{OD} = \left(1 + \frac{\varepsilon_1 + \varepsilon_2}{2}\right) V_{ID} + \left(\varepsilon_1 - \varepsilon_2\right) V_{IC} + \left(V_{OS1} - V_{OS2}\right) \cong \left(1 + \frac{\varepsilon_1 + \varepsilon_2}{2}\right) V_{ID}$$

$$\begin{split} V_{OD} = & \left(1 + \frac{\epsilon_1 + \epsilon_2}{2}\right) V_{ID} + \left(\epsilon_1 - \epsilon_2\right) V_{IC} + \left(V_{OS1} - V_{OS2}\right) \cong \left(1 + \frac{\epsilon_1 + \epsilon_2}{2}\right) V_{ID} \\ V_{OC} = & \left(\frac{\epsilon_1 - \epsilon_2}{4}\right) V_{ID} + \left(1 + \frac{\epsilon_1 + \epsilon_2}{2}\right) V_{IC} + \left(\frac{V_{OS1} + V_{OS2}}{2}\right) \cong \left(1 + \frac{\epsilon_1 + \epsilon_2}{2}\right) V_{IC} + \left(\frac{V_{OS1} + V_{OS2}}{2}\right) \end{split}$$

- Assuming good matching between the two half circuits, we have all benefits of differential signaling

- Small residual offset in  $V_{OD}$

- Good rejection of coupling noise, supply noise, ...

- Small common-mode to differential-mode gain

- Unfortunately, V<sub>OD</sub> has same gain error as basic single-ended circuit

- Also have nonlinear terms

- Simplistic models assume channel charge linearly related to V<sub>in</sub> (ignoring higher order effects, e.g. backgate effect)

- Expect to see nonlinear distortion along with gain error

#### Advanced Techniques

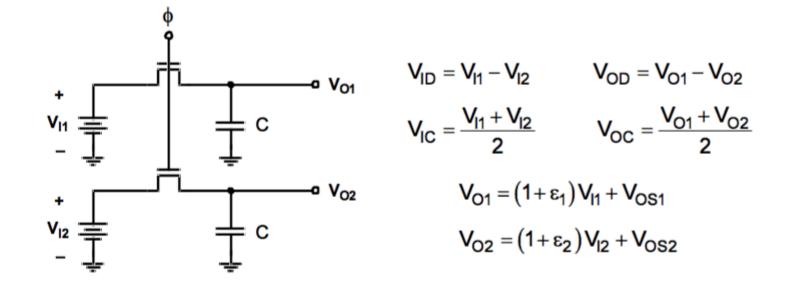

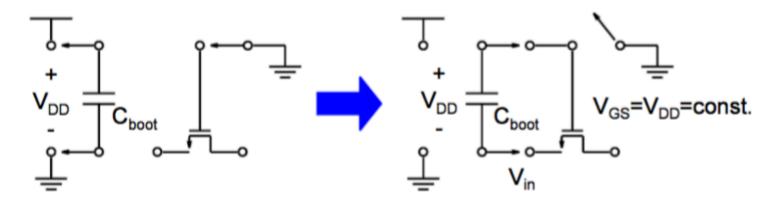

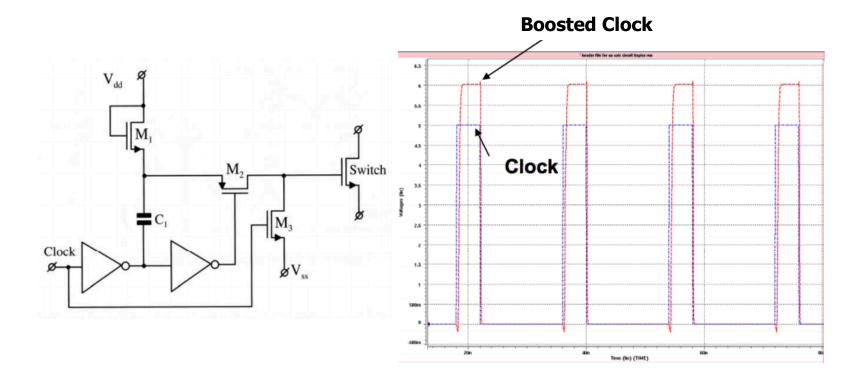

Clock Bootstrapping (Reference)

A. Abo, "Design for Reliability of Low-voltage, Switched-capacitor Circuits," PhD Thesis, UC Berkeley, 1999.

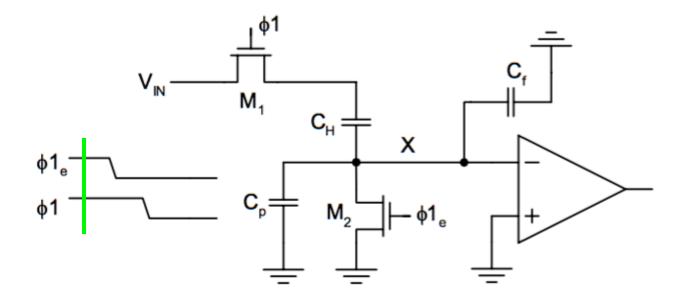

- □ Phase 1

- $C_{\text{boot}}$  is precharged to  $V_{\text{DD}}$

- Sampling switch is off

- Dephase 2

- Sampling switch is on with  $V_{GS} = V_{DD} = const.$

- To first order, both  $R_{ON}$  and channel charge are signal independent

**Simulation Result**

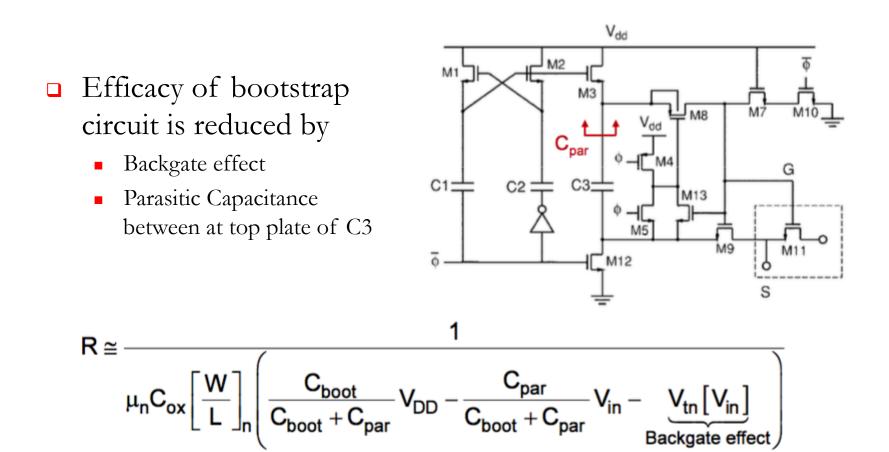

Circuit Implementation (Reference)

Penn ESE 568 Fall 2019 - Khanna adapted from Murmann EE315B, Stanford

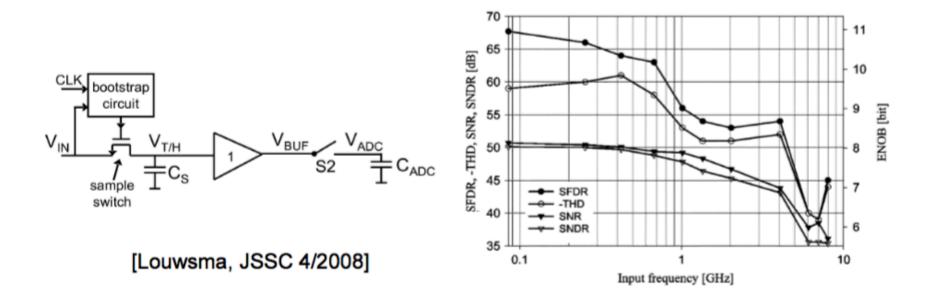

Performance of Bootstrapped Samplers (Reference)

### Bootstrapped sampling tends to work well up to ~10bit resolution

Penn ESE 568 Fall 2019 - Khanna adapted from Murmann EE315B, Stanford

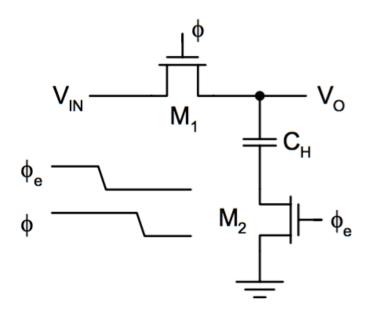

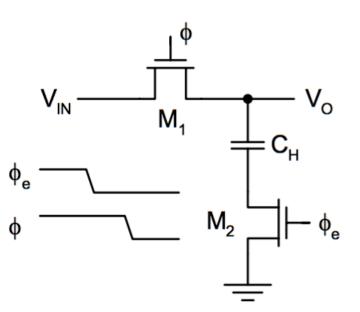

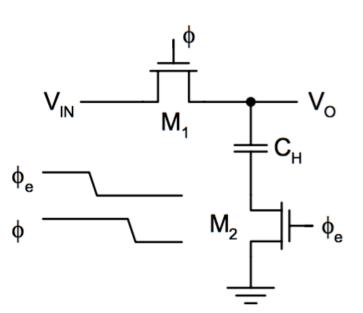

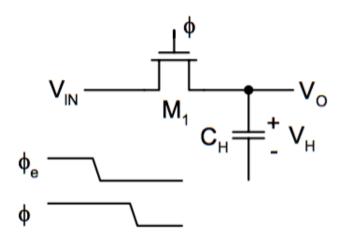

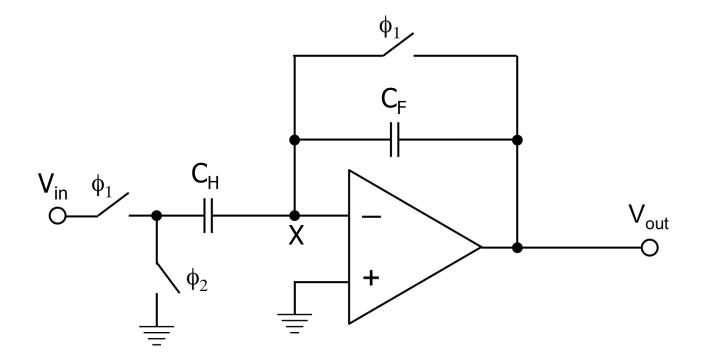

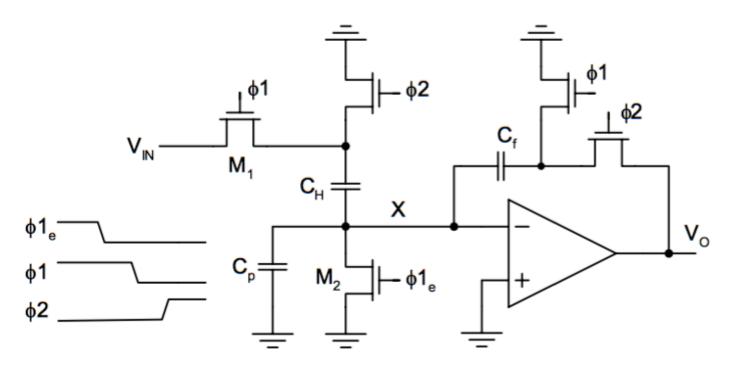

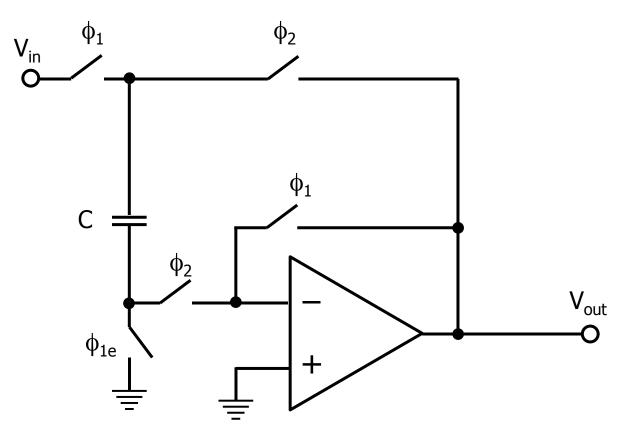

## Bottom Plate Sampling

- What if we want to do <u>much</u> better, e.g. 16 bits?

- Basic idea

- Sample signal at the "grounded" side of the capacitor to achieve signal independence

- References

- D. J. Allstot and W. C. Black, Jr., "Technological Design Considerations for Monolithic MOS Switched-Capacitor Filtering Systems," Proc. IEEE, pp. 967-986, Aug. 1983.

- K.-L. Lee and R. G. Meyer, "Low-Distortion Switched- Capacitor Filter Design Techniques," IEEE J. Solid-State Circuits, pp. 1103-1113, Dec. 1985.

- □ First look at single ended circuit

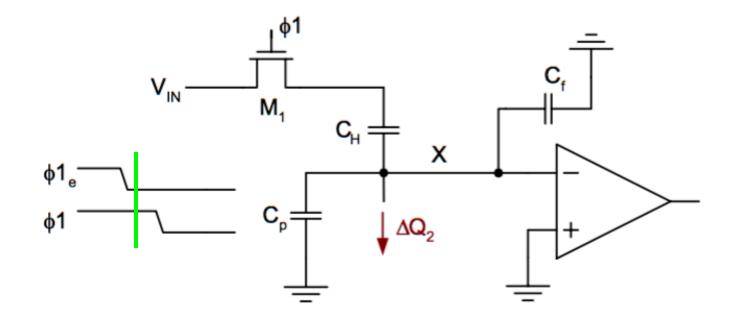

Bottom Plate Sampling Analysis

□ Turn M2 off "slightly" before M1

- □ Turn M2 off "slightly" before M1

- During turn off, M2 injects charge

$$\Delta Q_2 \cong \alpha_2 WLC_{ox} (\phi_H - V_{tn})$$

- To first order, charge injected by M2 is signal independent!

- Voltage across  $C_H$

$$V_H = V_{IN} - \frac{\Delta Q_2}{C_H}$$

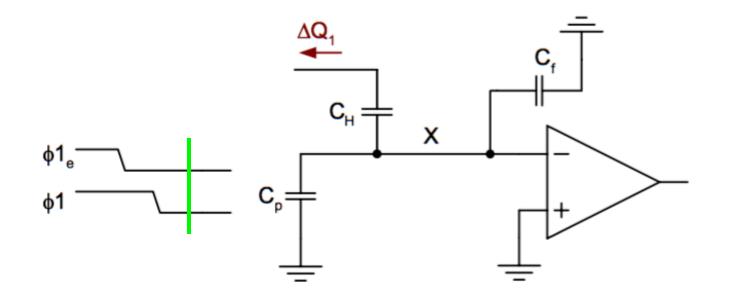

- □ Next, turn off M<sub>1</sub>

- Since bottom plate of C<sub>H</sub> is floating, there is no way to change its stored charge

- M1 cannot inject any charge onto C<sub>H</sub>

- Most of M<sub>1</sub>'s charge injection goes to input source and/or onto parasitics at node V<sub>O</sub>

- □ Next, turn off M<sub>1</sub>

- Since bottom plate of C<sub>H</sub> is floating, there is no way to change its stored charge

- M1 cannot inject any charge onto C<sub>H</sub>

- Most of M<sub>1</sub>'s charge injection goes to input source and/or onto parasitics at node V<sub>O</sub>

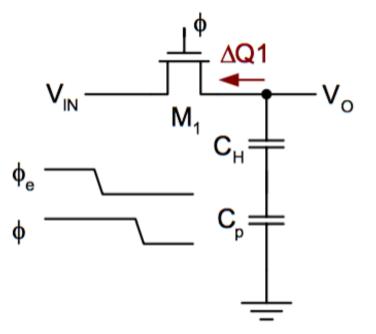

- But, is the bottom plate really floating?

Bottom plate not really floating...

- There must be some parasitic cap, e.g. M2 drain-to-bulk capacitance

- So, in real life, M1 does inject charge onto C<sub>H</sub>

- How much?

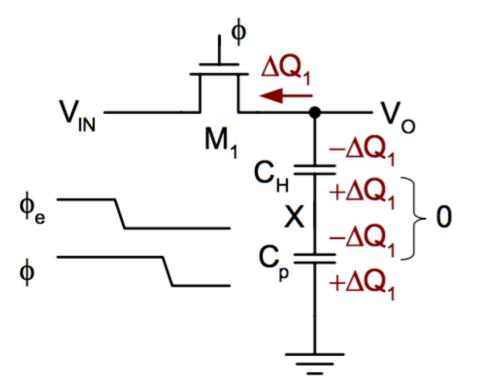

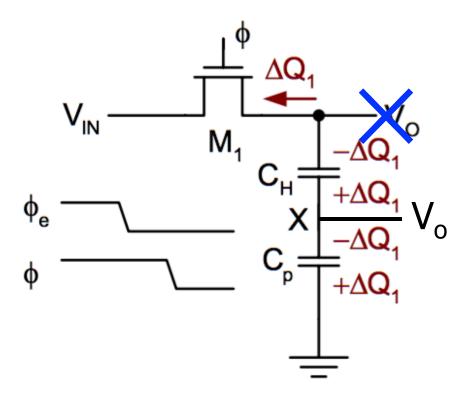

#### Interesting observation

Even if M1 injects some charge onto C<sub>H</sub>, the total charge at node X cannot change!

#### Interesting observation

- Even if M1 injects some charge onto C<sub>H</sub>, the total charge at node X cannot change!

- Idea

Process total charge at node X instead of looking at voltage across C<sub>H</sub>

- □ kTC noise

- □ Finite acquisition time

- Tracking nonlinearity

- Signal dependent hold instant

- Charge injection and clock feedthrough

- Hold mode feedthrough and leakage

- Clock jitter

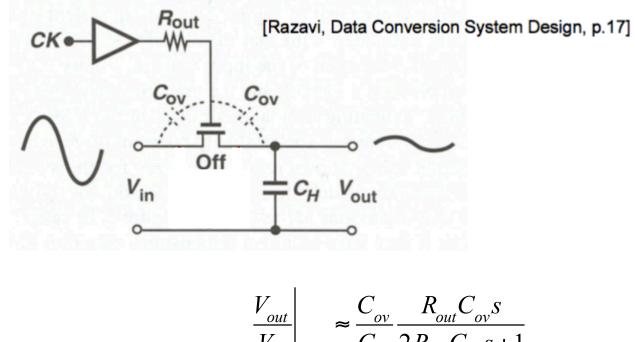

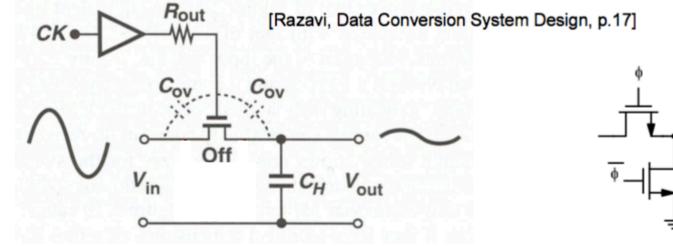

$$V_{in}|_{hold}$$

$C_H 2R_{out}C_{ov}S+1$

$\square$  Want to make  $R_{out}$  as small as possible

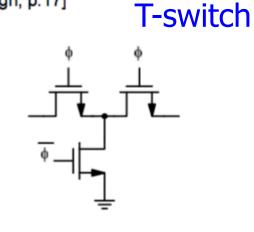

- **T**-Switch for low speed applications

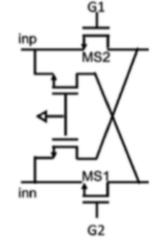

- Cross coupling for high speed applications

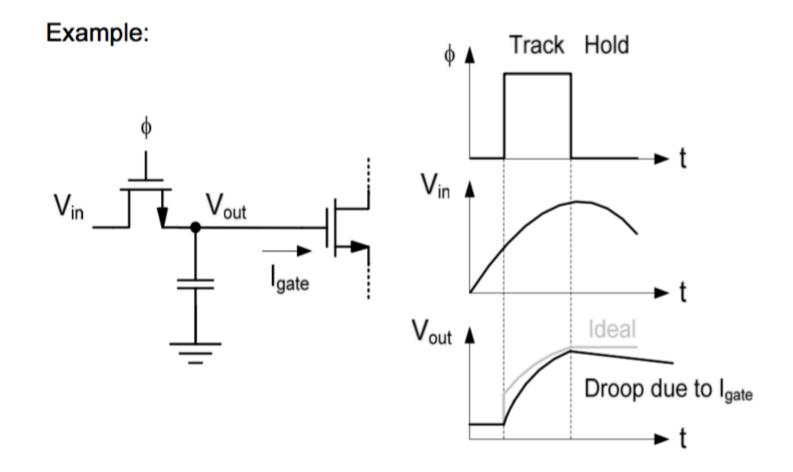

A. Annema, et al., "Analog circuits in ultra-deep-submicron CMOS," IEEE J. Solid-State Circuits, pp. 132-143, Jan. 2005.

$$\frac{dv_C}{dt} \approx -\gamma_{dv\,dt} \cdot f_{\text{gate}} \left[\frac{V}{s}\right] \quad \text{with } \gamma_{dv\,dt} \approx 1 \,\text{V}.$$

□ In 65nm CMOS, gate capacitance droop rate is  $1V/\mu$  s!

□ Later process use high-k dielectrics

- In any sampling circuit, electronic noise causes random timing variations in the actual sampling clock edge

- Adds "noise" to samples, especially if  $dV_{in}/dt$  is large

$$\Delta V_{in} = Change in V_{in} during \Delta t$$

$$\Delta V_{in} \cong \frac{dV_{in}}{dt} \cdot \Delta t$$

$$\Delta t = Sampling jitter$$

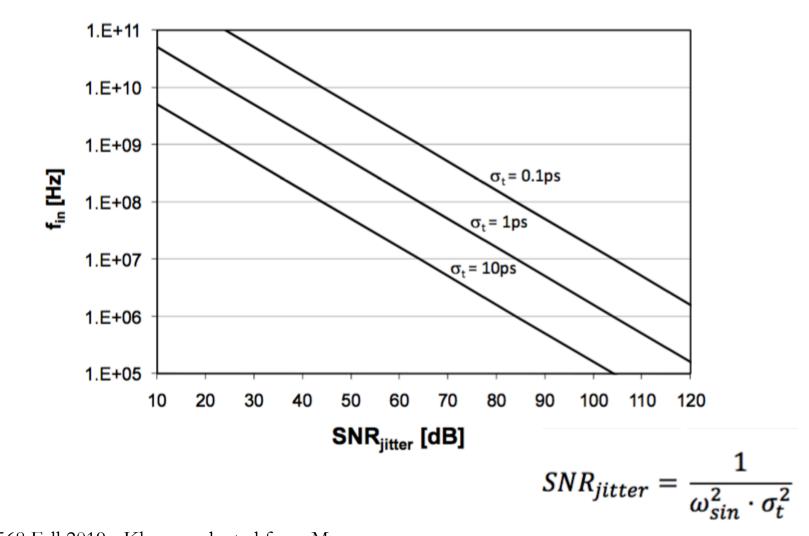

Analysis

- Consider sine wave input signal

- Assume  $\Delta t$  is random with zero mean and standard deviation  $\sigma_t$

Analysis

$$\Delta V_{in} = Change in V_{in} during \Delta t$$

$$\Delta V_{in} \cong \frac{dV_{in}}{dt} \cdot \Delta t$$

$$E\left\{\Delta V_{in}^{2}\right\} \cong E\left\{\left(\frac{dV_{in}}{dt}\right)^{2} \cdot \Delta t^{2}\right\} = E\left\{\left(\frac{dV_{in}}{dt}\right)^{2}\right\} \cdot E\left\{\Delta t^{2}\right\}$$

$$\cong E\left\{\left(\frac{d}{dt}A\cos[2\pi \cdot f_{in} \cdot t]\right)^{2}\right\} \cdot \sigma_{t}^{2} \cong \frac{1}{2}(2\pi \cdot A \cdot f_{in})^{2} \cdot \sigma_{t}^{2}$$

$$SNR_{jitter} = \frac{\frac{1}{2}A^{2}}{\frac{1}{2}A^{2}\omega_{sin}^{2} \cdot \sigma_{t}^{2}} = \frac{1}{\omega_{sin}^{2} \cdot \sigma_{t}^{2}}$$

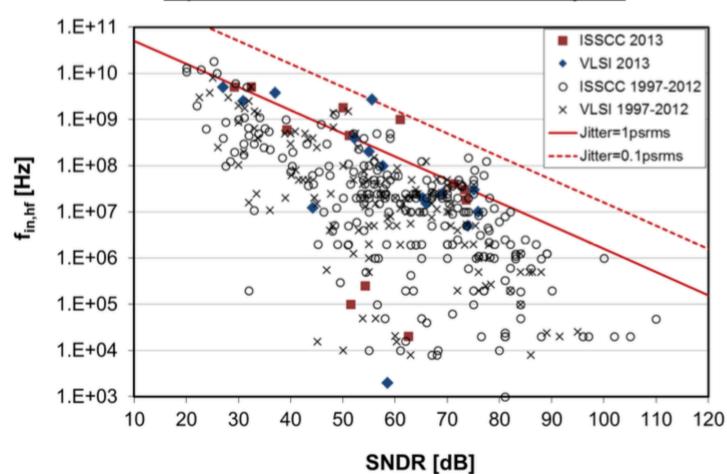

ADC Performance Survey (ISSCC & VLSI)

Data: http://www.stanford.edu/~murmann/adcsurvey.html

Significance of Jitter

- In light of the above, sampling jitter has become one of the main showstoppers for further improvements in the ADC speed-resolution product

- **Example**

$$SNR_{jitter} = \frac{\frac{1}{2}A^2}{\frac{1}{2}A^2\omega_{sin}^2 \cdot \sigma_t^2} = \frac{1}{\omega_{sin}^2 \cdot \sigma_t^2}$$

- $F_{in}=10MHz$ ,  $\sigma_t=300ps \rightarrow SNR_{jitter}=34.5dB$

- Not great, but in many applications, the signal is not a sinusoid, but spread in some way across frequency

- Proper analysis must take into account signal properties

- See Da Dalt, TCAS1, 9/2002

- Autocorrelation analysis

### Switched Capacitor Circuits

# Interesting Switched Capacitor Circuits

- □ Track & Hold

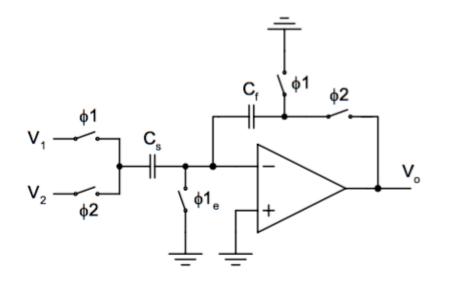

- Charge redistribution T/H with common mode cancellation

- Flip-around T/H

- SC Difference amplifiers

- Used e.g. in pipeline ADCs

- SC Integrators

- Used e.g. in sigma-delta ADCs

- Passive charge redistribution networks

- Used e.g. in successive approximation ADCs

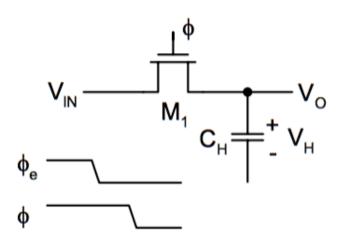

• With bottom plate sampling

• Total charge at node X:  $Q_X = -C_H V_{IN}$

• Total charge at node X:  $Q_X = -C_H V_{IN} - \Delta Q_2$

- Total charge at node X:  $Q_X = -C_H V_{IN} \Delta Q_2$

- Q1 charge injection changes voltage across all caps, but total charge at X remains unchanged

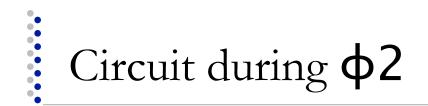

Opamp forces voltage at node X to zero

Charge at X must redistribute among capacitors

□ Sampled Charge:

$$Q_{X1} = -C_H V_{IN} - \Delta Q_2$$

• After Redistribution:

$$Q_{X2} = -C_f V_O$$

□ Charge Conservation:

$$Q_{XI} = Q_{X2}$$

$$-C_H V_{IN} - \Delta Q_2 = -C_f V_O$$

$$\therefore V_O = \frac{C_H}{C_f} V_{IN} + \frac{\Delta Q_2}{C_f}$$

- Output has signal independent offset

- Can easily cancel through full differential circuit

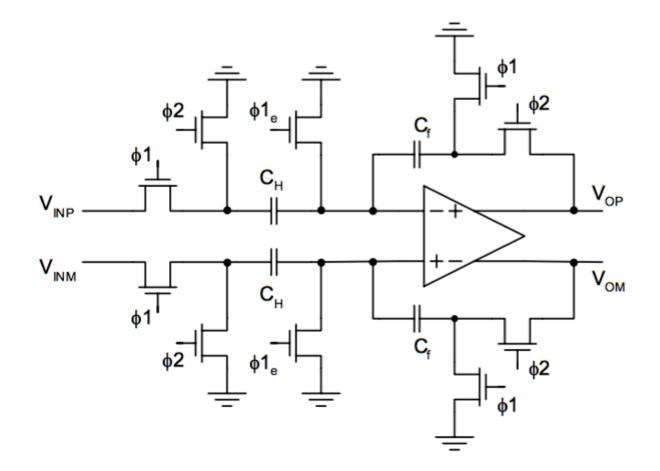

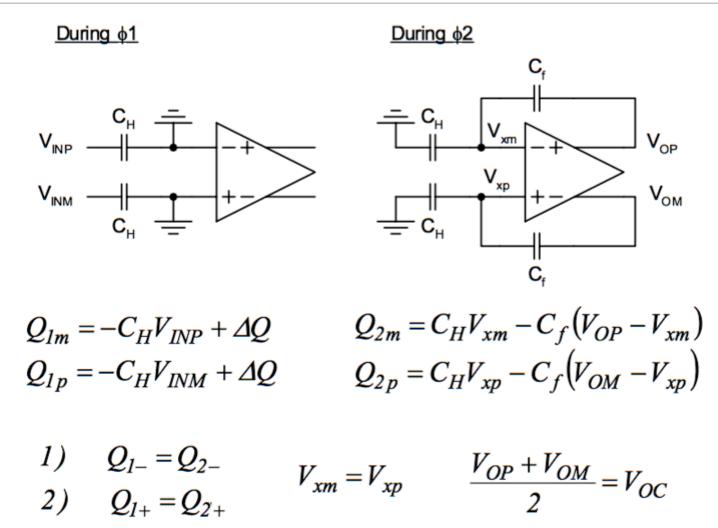

During  $\phi 1$ During  $\phi 2$ C<sub>f</sub> C<sub>H</sub> V<u>xm</u>  $V_{INP}$ VOP  $V_{xp}$ V<sub>OM</sub>  $V_{\text{INM}}$ C<sub>H</sub> C C<sub>f</sub>  $Q_{2m} = C_H V_{xm} - C_f (V_{OP} - V_{xm})$  $Q_{2p} = C_H V_{xp} - C_f (V_{OM} - V_{xp})$  $Q_{lm} = -C_H V_{INP} + \Delta Q$  $Q_{1p} = -C_H V_{INM} + \Delta Q$

□ Subtracting 1) and 2) yields

$$V_{OP} - V_{OM} = \frac{C_H}{C_f} \left( V_{INP} - V_{INM} \right)$$

□ Adding 1) and 2) yields

$$-C_{H}(V_{INP} + V_{INM}) + 2\Delta Q = (C_{H} + C_{f})(V_{xp} + V_{xm}) - C_{f}(V_{OP} + V_{OM})$$

$$V_{xc} = \frac{\Delta Q}{C_{H} + C_{f}} + \frac{C_{f}}{C_{H} + C_{f}}V_{OC} - \frac{C_{H}}{C_{H} + C_{f}}V_{IC}$$

- Variation in V<sub>IC</sub> show up as common mode variations at the amp input

- Need good CMRR

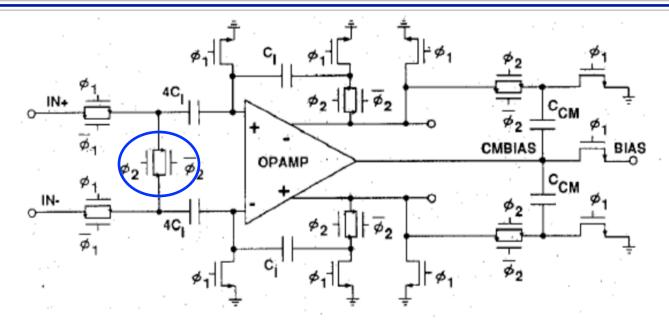

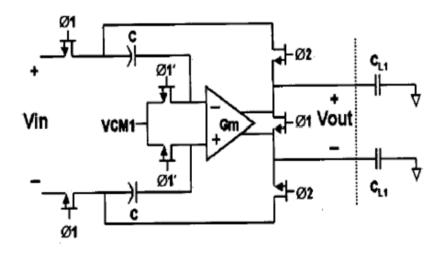

T/H with Common Mode Cancellation (Reference)

S.H. Lewis & P.R. Gray, "A Pipelined 5 MSample/s 9-bit Analog-to-Digital Converter", IEEE J. Solid-State Circuits, pp. 954-961, Dec. 1987

- Short switch allows to re-distribute only differential charge on sampling capacitors

- Common mode at OPAMP input becomes independent of common mode at circuit input terminals (IN+/IN-)

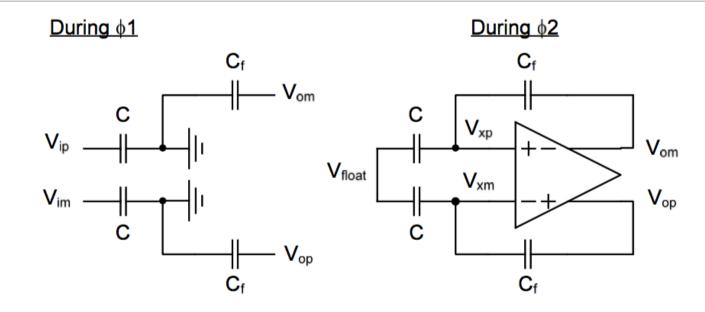

$\hfill\square$  Charge conservation at  $V_{ip}, V_{im}$  and  $V_{float}$

$$\begin{split} \left(\mathsf{V}_{\mathsf{ip}} + \mathsf{V}_{\mathsf{im}}\right) &\cdot \mathbf{C} = \left(\mathsf{V}_{\mathsf{float}} - \mathsf{V}_{\mathsf{xp}}\right) \cdot \mathbf{C} + \left(\mathsf{V}_{\mathsf{float}} - \mathsf{V}_{\mathsf{xm}}\right) \cdot \mathbf{C} \\ &\quad \mathsf{V}_{\mathsf{ic}} = \mathsf{V}_{\mathsf{float}} - \mathsf{V}_{\mathsf{xc}} \\ &\quad \mathsf{V}_{\mathsf{float}} = \mathsf{V}_{\mathsf{ic}} + \mathsf{V}_{\mathsf{xc}} \end{split}$$

Analysis (Reference)

Common mode charge conservation at amplifier inputs

$$\begin{split} V_{ic} \cdot C + V_{oc} \cdot C_{f} &= \left( V_{float} - V_{xc} \right) \cdot C + \left( V_{oc} - V_{xc} \right) \cdot C_{f} \\ V_{ic} \cdot C &= \left( \left[ V_{ic} + V_{xc} \right] - V_{xc} \right) \cdot C - V_{xc} \cdot C_{f} \\ 0 &= V_{xc} \end{split}$$

- Amplifier input common mode (V<sub>XC</sub>) is independent of

- Input common mode

- Output common mode

[W. Yang et al., "A 3-V 340-mW 14-b 75-MSample/s CMOS ADC With 85-dB SFDR at Nyquist Input", IEEE J. Solid-State Circuits, pp. 1931-1936, Dec. 2001]

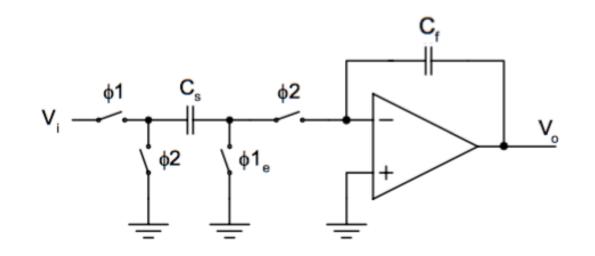

- Sampling caps are "flipped around" and used as feedback capacitors during φ2

- Pros: improved feedback factor (lower noise, higher speed), smaller area

- Cons: Amp is subjected to input common mode variations

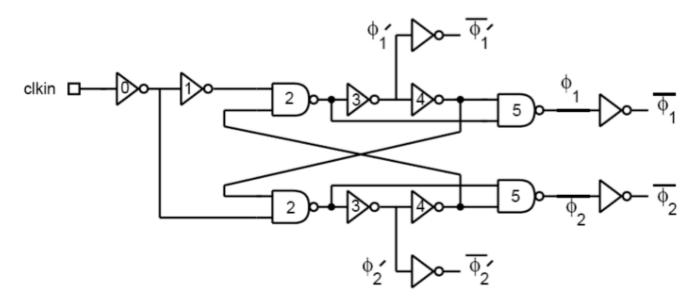

Non-overlapping clocks

[A. Abo, "Design for Reliability of Low-voltage, Switched-capacitor Circuits," PhD Thesis, UC Berkeley, 1999]

• Useful for computing differences of signals

• Application example: Pipeline ADC (more later)

Useful for computing differences of signals

• Application example: Pipeline ADC (more later)

- $C_{\rm f}$  accumulates charge packets acquired during  $\phi$  1

- "Discrete time integrator"

- □ Used e.g. in switched capacitor sigma-delta ADCs

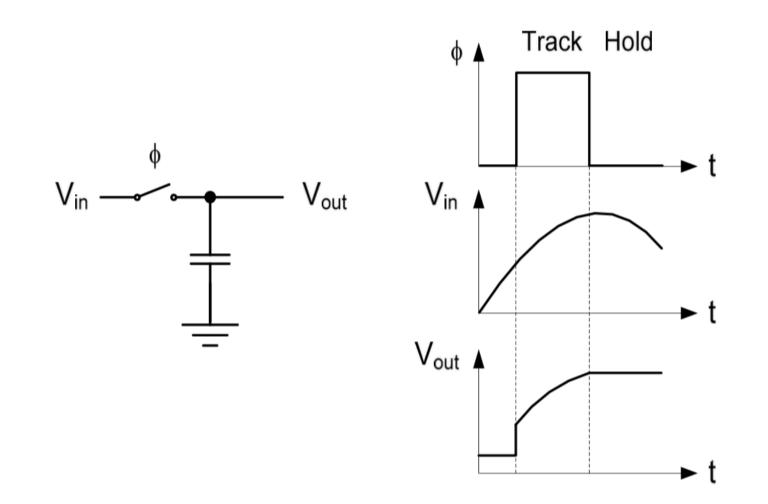

- Elementary track-and-hold circuit

- Many nonidealities

- First order improvements can improve performance

- Track-and-hold topologies

- Charge redistribution add common mode cancellation

- Bottom plate sampling charge injection cancellation

- Fully differential eliminate signal dependent offset

- Flip-around

- Faster

- □ Clock generation non overlapping clocks

Proj 1

- Due Tuesday 10/8

- **u** HW 4

- Due Sunday 10/13

- ADC static and spectral metrics