# Microeconomic Models for Managing Shared Datacenters

by

#### Qiuyun Llull

Department of Electrical and Computer Engineering

Duke University

| Date:                       |

|-----------------------------|

| Approved:                   |

|                             |

|                             |

|                             |

| Benjamin C. Lee, Supervisor |

| Benjamin et Bee, supertiser |

|                             |

|                             |

| Jeffrey S. Chase            |

|                             |

|                             |

|                             |

| Alvin R. Lebeck             |

|                             |

|                             |

|                             |

| Gabriel H. Loh              |

|                             |

|                             |

|                             |

| Daniel J. Sorin             |

Dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Electrical and Computer Engineering in the Graduate School of Duke University

ProQuest Number: 10259678

#### All rights reserved

#### INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

#### ProQuest 10259678

Published by ProQuest LLC (2017). Copyright of the Dissertation is held by the Author.

All rights reserved.

This work is protected against unauthorized copying under Title 17, United States Code Microform Edition © ProQuest LLC.

ProQuest LLC.

789 East Eisenhower Parkway

P.O. Box 1346

Ann Arbor, MI 48106 – 1346

### **Abstract**

# Microeconomic Models for Managing Shared Datacenters

by

### Qiuyun Llull

Department of Electrical and Computer Engineering

Duke University

| Date:                       |

|-----------------------------|

| Approved:                   |

|                             |

|                             |

|                             |

| Benjamin C. Lee, Supervisor |

| J*                          |

|                             |

|                             |

| Jeffrey S. Chase            |

| V                           |

|                             |

|                             |

| Alvin R. Lebeck             |

|                             |

|                             |

|                             |

| Gabriel H. Loh              |

|                             |

|                             |

|                             |

| Daniel J. Sorin             |

An abstract of a dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Electrical and Computer Engineering

in the Graduate School of Duke University 2017

# Abstract

As demands for users' applications' data increase, the world's computing platforms are moving towards more capable machines – servers and warehouse-scale datacenters. Diverse users share datacenters for complex computation and compete for shared resources. In some systems, such as public clouds where users pay for reserved hardware, management policies pursue performance goals. In contrast, private systems consist of users who voluntarily combine their resources and subscribe to a common management policy. These users reserve the right to opt-out from shared systems if resources are managed poorly. The system management framework needs to ensure fairness among strategic users, encouraging users to participate while guaranteeing individual performance and preserving the system's performance. Microeconomic models are well suited for studying individual behavior and the allocation of scarce resources. In this thesis, we present three pieces of work on task colocation, resource allocation and task scheduling problems to demonstrate the effectiveness of a microeconomic approach.

Colocating applications on shared hardware (i.e., chip-multiprocessors) improves server utilization but introduces resource contention into the memory subsystem. In the first work, we design a colocation framework based on cooperative game theory to manage shared resource contention. Our framework uses a recommendation system to predict individual applications preferences for colocated tasks. It then uses these predictions to drive novel colocation mechanisms to guarantee user fairness and

preserve system performance. Attractive system outcomes encourage strategic users to participate in the datacenter.

Processor allocations are inefficient when they are based on static reservations because reservations are often conservative; users rarely know their application's needs across time, especially when applications have complex phase behavior. In the second work, we propose a fast, lightweight performance prediction framework to help users capture their phase behaviors in parallel applications. We design a dynamic and distributed core allocation framework so that users can trade resources for better efficiency based on predicted performance. Our management framework provides efficient allocations and game-theoretic fairness guarantees.

In the last work, we characterize applications' sensitivity to non-uniform memory access (NUMA) in big memory servers. We develop performance and energy models for communication costs in a blade server. We use this model to perform case studies on NUMA-aware scheduling policies and task queue management. Our parameterized models lay the foundation for coordinated design of scheduling policies and hardware configurations. This method can be further used to design locality-aware schedulers with microeconomic models, e.g., dynamic pricing strategies for city parking.

# Contents

| A  | bstra | $\operatorname{ct}$ |                                                              | iv  |

|----|-------|---------------------|--------------------------------------------------------------|-----|

| Li | st of | Table               | ${f s}$                                                      | xi  |

| Li | st of | Figur               | es                                                           | xii |

| A  | ckno  | wledge              | ements                                                       | xvi |

| 1  | Intr  | roducti             | ion                                                          | 1   |

|    | 1.1   | Organ               | nization and Overview of the Dissertation                    | 4   |

|    |       | 1.1.1               | Cooperative Games to Manage Colocation Contention            | 4   |

|    |       | 1.1.2               | Market Mechanism to Allocate Cores for Parallel Applications | 5   |

|    |       | 1.1.3               | Performance and Energy Models for Blade Servers              | 6   |

|    |       | 1.1.4               | Key Contributions of the Thesis                              | 7   |

| 2  | Tas   | k Colo              | ocation with Cooperative Games                               | 8   |

|    | 2.1   | Case f              | for Fair Colocation                                          | 10  |

|    |       | 2.1.1               | Desirable System Desiderata                                  | 11  |

|    |       | 2.1.2               | Fair Attribution                                             | 11  |

|    |       | 2.1.3               | Satisfied Preferences and Stability                          | 14  |

|    | 2.2   | The C               | Colocation Game                                              | 15  |

|    |       | 2.2.1               | System Setting                                               | 16  |

|    |       | 2.2.2               | Game Formulation                                             | 17  |

|    |       | 2 2 3               | Game Solutions                                               | 18  |

|   | 2.3 | Coope  | er Colocation Framework Design | 22 |

|---|-----|--------|--------------------------------|----|

|   |     | 2.3.1  | Preference Predictor           | 23 |

|   |     | 2.3.2  | Action Recommender             | 25 |

|   |     | 2.3.3  | Colocation Policies            | 26 |

|   |     | 2.3.4  | Other Components               | 27 |

|   | 2.4 | Exper  | imental Methodology            | 28 |

|   | 2.5 | Evalua | ation                          | 30 |

|   |     | 2.5.1  | Fairness and Desiderata        | 30 |

|   |     | 2.5.2  | Performance and Sensitivity    | 35 |

|   |     | 2.5.3  | Preference Prediction          | 37 |

|   |     | 2.5.4  | Scalability                    | 38 |

|   | 2.6 | Relate | ed Work                        | 38 |

|   | 2.7 | Concl  | usions and Future Work         | 40 |

|   | 2.8 | Ackno  | owledgments                    | 41 |

| 3 | Cor | e Allo | cation with Market Mechanism   | 42 |

|   | 3.1 | Manag  | gement Architecture            | 44 |

|   |     | 3.1.1  | System Setting                 | 44 |

|   |     | 3.1.2  | Motivation                     | 45 |

|   |     | 3.1.3  | Allocation Architecture        | 46 |

|   | 3.2 | Amda   | hl Utility                     | 48 |

|   |     | 3.2.1  | Experimental Methodology       | 49 |

|   |     | 3.2.2  | Demonstration of Karp-Flatt    | 52 |

|   |     | 3.2.3  | Linear Scaling for Data Size   | 53 |

|   |     | 3.2.4  | Prediction Framework           | 55 |

|   |     | 3 2 5  | Prediction Validation          | 57 |

|   | 3.3 | Marke                                                                  | et Allocation                        | 58                                           |

|---|-----|------------------------------------------------------------------------|--------------------------------------|----------------------------------------------|

|   |     | 3.3.1                                                                  | Amdahl Utility Function              | 59                                           |

|   |     | 3.3.2                                                                  | Market Mechanism                     | 60                                           |

|   | 3.4 | Evalua                                                                 | ation                                | 63                                           |

|   |     | 3.4.1                                                                  | Baseline Policies                    | 63                                           |

|   |     | 3.4.2                                                                  | Experimental Methodologies           | 65                                           |

|   |     | 3.4.3                                                                  | Performance                          | 65                                           |

|   |     | 3.4.4                                                                  | Envy-Freeness                        | 67                                           |

|   |     | 3.4.5                                                                  | Sharing Incentives                   | 69                                           |

|   | 3.5 | Relate                                                                 | ed Work                              | 70                                           |

|   | 3.6 | Conclu                                                                 | usions and Future Work               | 72                                           |

|   | 3.7 | Specia                                                                 | al Acknowledgement                   | 73                                           |

| 4 | Mo  | deling                                                                 | Communication Costs in Blade Servers | 74                                           |

|   |     |                                                                        |                                      |                                              |

|   | 4.1 | Backg                                                                  | round and Motivation                 | 75                                           |

|   | 4.1 | Backg 4.1.1                                                            | round and Motivation                 | 75<br>75                                     |

|   | 4.1 |                                                                        |                                      |                                              |

|   | 4.1 | 4.1.1<br>4.1.2                                                         | Modeling Blade Servers               | 75                                           |

|   |     | 4.1.1<br>4.1.2                                                         | Modeling Blade Servers               | 75<br>76                                     |

|   |     | 4.1.1<br>4.1.2<br>Model                                                | Modeling Blade Servers               | 75<br>76<br>78<br>79                         |

|   |     | 4.1.1<br>4.1.2<br>Model<br>4.2.1                                       | Modeling Blade Servers               | 75<br>76<br>78<br>79                         |

|   |     | 4.1.1<br>4.1.2<br>Model<br>4.2.1<br>4.2.2                              | Modeling Blade Servers               | 75<br>76<br>78<br>79<br>81                   |

|   |     | 4.1.1<br>4.1.2<br>Model<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4            | Modeling Blade Servers               | 75<br>76<br>78<br>79<br>81<br>82             |

|   | 4.2 | 4.1.1<br>4.1.2<br>Model<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4            | Modeling Blade Servers               | 75<br>76<br>78<br>79<br>81<br>82<br>83       |

|   | 4.2 | 4.1.1<br>4.1.2<br>Model<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>Case \$ | Modeling Blade Servers               | 75<br>76<br>78<br>79<br>81<br>82<br>83<br>85 |

| Bi | ogra  | phy    |                              | 121 |

|----|-------|--------|------------------------------|-----|

| Bi | bliog | graphy |                              | 110 |

| 5  | Con   | clusio | n                            | 107 |

|    | 4.7   | Ackno  | wledgment                    | 106 |

|    | 4.6   | Conclu | usions and Future Work       | 105 |

|    |       | 4.5.4  | Power Efficiency Analysis    | 103 |

|    |       | 4.5.3  | Comparison to Data Migration | 98  |

|    |       | 4.5.2  | Response Time                | 95  |

|    |       | 4.5.1  | Throughput                   | 92  |

|    | 4.5   | Evalua | ation                        | 92  |

|    |       | 4.4.2  | Benchmarks and Parameters    | 90  |

|    |       | 4.4.1  | Methodologies                | 89  |

# List of Tables

| 2.1 | Application configurations, datasets, and memory intensity                                                                                             | 29 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | Cluster Specification                                                                                                                                  | 49 |

| 3.2 | Workloads and datasets                                                                                                                                 | 50 |

| 4.1 | Summary of technology models and estimates                                                                                                             | 84 |

| 4.2 | Benchmarks, their demand for remote memory bandwidth (Extremely Memory-Intensive, Memory Intensive, Compute Intensive) and latency penalties from NUMA | 90 |

| 4.3 | Marssx86 and DRAMSim2 simulation parameters                                                                                                            | 92 |

# List of Figures

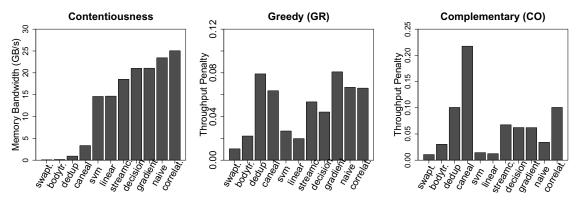

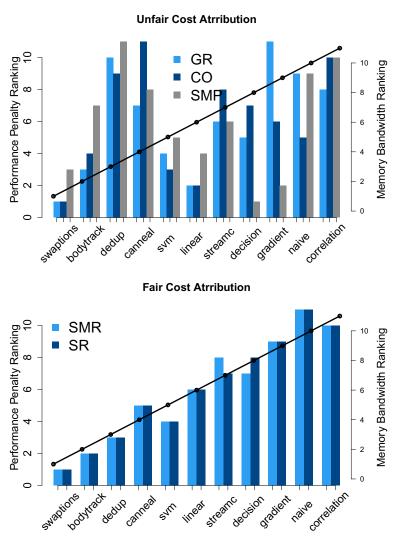

| 2.1 | Unfair colocations show no link between contentiousness and penalties. We colocate 1000 jobs drawn randomly from an application pool. Pairs of jobs share multiprocessor cache and memory bandwidth. Colocation penalties are averaged over those that include a particular job type (e.g., bodytrack) | 12        |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 2.2 | Shapley permutes users, calculates their contributions to penalties ${\bf M}$ and expected values $\phi$ over permutations                                                                                                                                                                             | 13        |

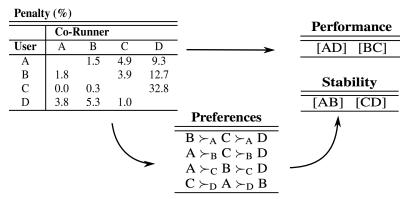

| 2.3 | Users' penalties determine preferences for co-runners. Pursuing performance minimizes system penalties. Pursuing stability satisfies user preferences. The four users in this dataset are: (A) x264, (B) fluidanima (C) decision-tree, (D) regression                                                  | te,<br>15 |

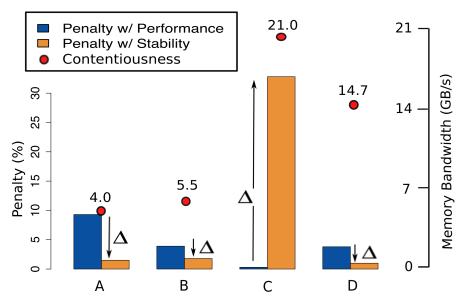

| 2.4 | Stability enhances fairness. Bars show user penalty based on throughput loss under performance- and stability-centric colocation policies. Dots show user contentiousness, based on bandwidth demand when alone. Data for four users: (A) x264, (B) fluidanimate, (C) decision-t (D) regression        | ree<br>16 |

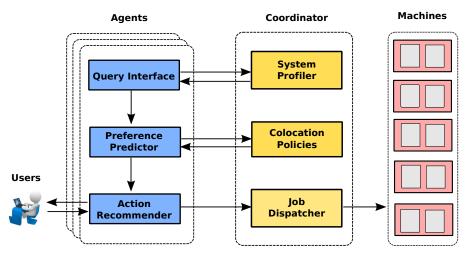

| 2.5 | Agents act on users' behalf, playing the colocation game and interfacing with the system coordinator. The agents and the coordinator shield hardware complexity from human users                                                                                                                       | 17        |

| 2.6 | Stable marriage with compute- and memory-intensive jobs                                                                                                                                                                                                                                                | 20        |

| 2.7 | Cooper Colocation Framework                                                                                                                                                                                                                                                                            | 23        |

| 2.8 | Disutility from pairwise job colocations. See Table 3.2 for job IDs                                                                                                                                                                                                                                    | 29        |

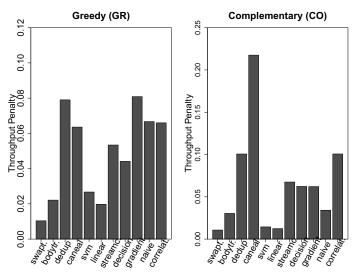

| 2.9 | (a) and (b) show contention-induced performance losses from conventional colocation policies. Jobs are ordered by increasing contentiousness on x-axis                                                                                                                                                 | 31        |

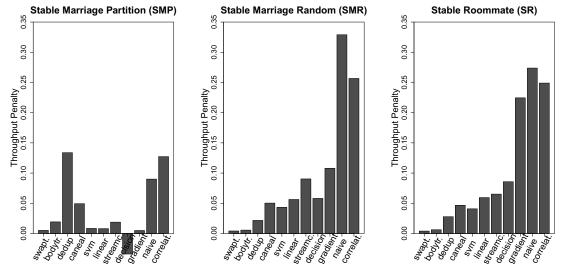

| 2.10 | (a) (b) and (c) show performance losses from stable colocation policies.  Jobs are ordered by increasing contentiousness on x-axis                                                                                                                                                                                                                                                          | 31 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.11 | Correlation between ranked performance penalties (bars) and bandwidth demands (line). When the bars track the line, colocations are fair. See Figures 2.10 for absolute measures of performance and bandwidth                                                                                                                                                                               | 33 |

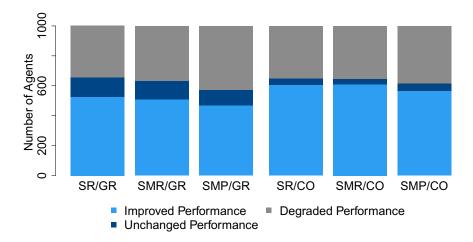

| 2.12 | Performance impact when adopting cooperative game (S*) instead of performance-centric policies (GR, CO). Data is averaged over 10 populations, each with 1000 randomly sampled jobs                                                                                                                                                                                                         | 34 |

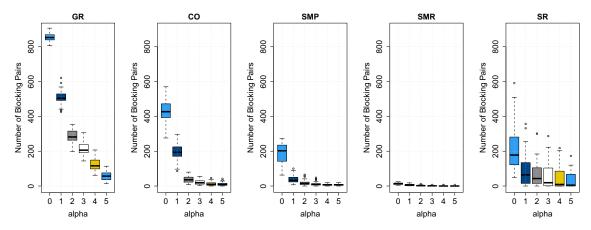

| 2.13 | Stability analysis, which measures the number of blocking pairs (y-axis) for varied policies and $\alpha$ (x-axis), the minimum benefit for which an agent breaks away. When $\alpha=2\%$ , agents break away for new colocations that improve both agents' performance by $2\%$ . Here, we show data distributions and boxplots for 50 populations, each with $1000$ randomly sampled jobs | 34 |

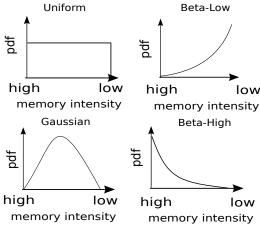

| 2.14 | Workload mixes (Uniform, Beta-Low, Gaussian, Beta-High)                                                                                                                                                                                                                                                                                                                                     | 36 |

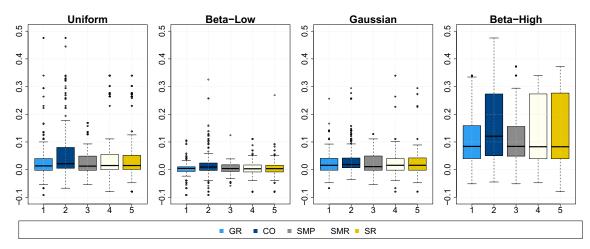

| 2.15 | Performance penalties measured for varied colocation polices (GR, CO, SMP, SMR, SR) for various workload mixes presented in Figure 2.14. Each box shows the performance penalty distribution of 1000 colocated tasks                                                                                                                                                                        | 36 |

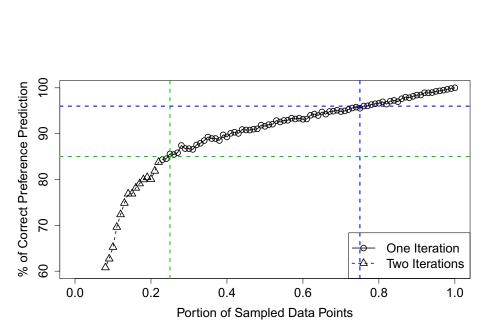

| 2.16 | Prediction accuracy, which evaluates the percentage of correctly predicted preferences (Equation 2.2). x-axis shows various sample ratios.                                                                                                                                                                                                                                                  | 38 |

| 2.17 | Scalability analysis and SMR fairness as the number of agents increases. Link between contentiousness and penalty is weak in small systems. In larger systems, more contentious jobs have larger penalties.                                                                                                                                                                                 | 39 |

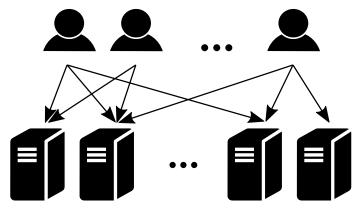

| 3.1  | Cluster of $m$ heterogeneous servers is shared by $n$ users. Users are assigned to servers based on preferences or constraints                                                                                                                                                                                                                                                              | 45 |

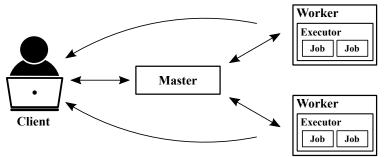

| 3.2  | Main components of the shared cluster: client, master, and worker                                                                                                                                                                                                                                                                                                                           | 47 |

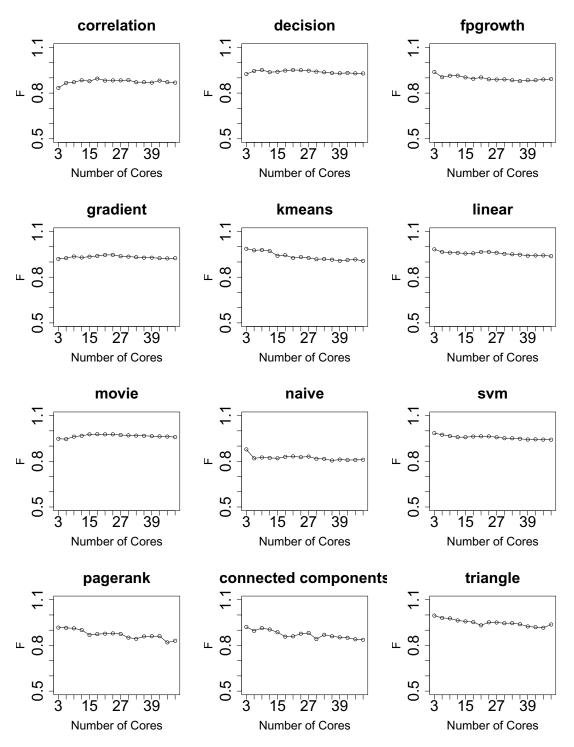

| 3.3  | Calculated parallel fraction $(F)$ for representative Spark applications as core count varies                                                                                                                                                                                                                                                                                               | 51 |

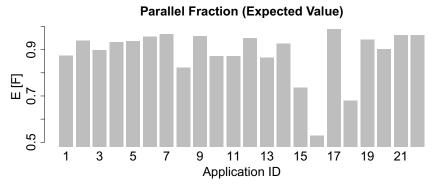

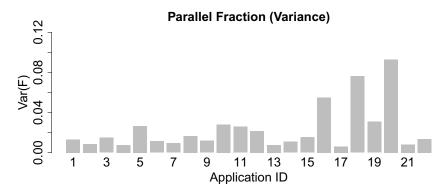

| 3.4  | Expected parallel fraction $\bar{F} = (\bar{F} =  c ^{-1} \sum_{c} F_c) \dots \dots \dots$                                                                                                                                                                                                                                                                                                  | 53 |

| 3.5  | Variance in parallel fraction $Var(F_c) =  c ^{-1} \sum_c (F_c - \bar{F})^2$ . Lower variance indicates a better fit with Amdahl's Law                                                                                                                                                                                                                                                      | 53 |

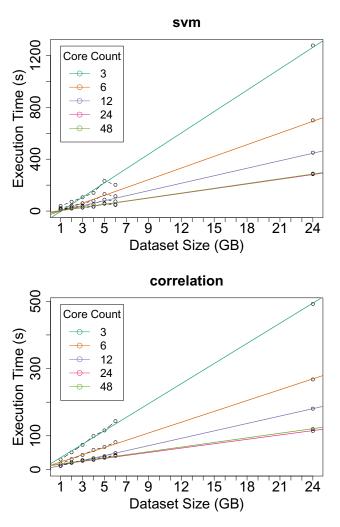

| 3.6  | We sample the dataset size and measure performance for varied core allocations. We fit linear models to estimate execution time from dataset size. Data shown for representative applications svm (T) and correlation (B)                             | 54 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

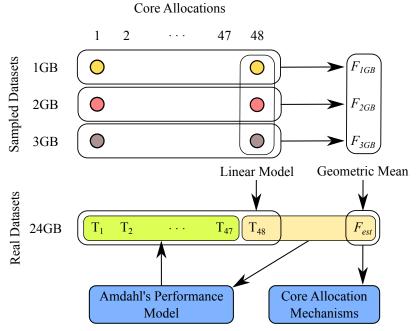

| 3.7  | Prediction framework uses linear models to estimate the effect of dataset size and Karp-Flatt calculations to estimate the effect of core count. Estimates may be used to predict execution time (Amdahl's Law) or allocate cores (market mechanism)  | 56 |

| 3.8  | Accuracy of predicted parallel fractions ${\cal F}$ when using sampled datasets.                                                                                                                                                                      | 57 |

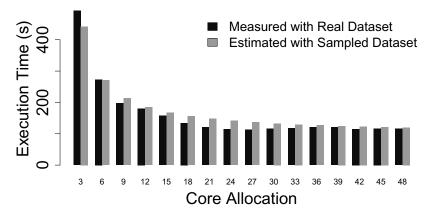

| 3.9  | Accuracy of predicted execution time given varied core allocations. Data shown for Decision Tree                                                                                                                                                      | 58 |

| 3.10 | Accuracy of predicted execution time for varied applications. Boxplots show distribution of errors given varied core allocations                                                                                                                      | 59 |

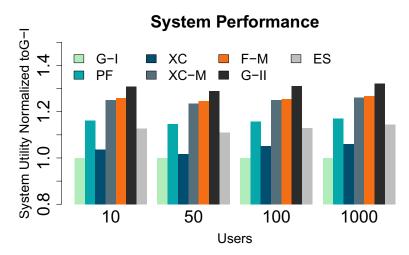

| 3.11 | Performance measured in terms of total user utility. System grows with user population; $n$ users request allocations on $m=n$ servers                                                                                                                | 66 |

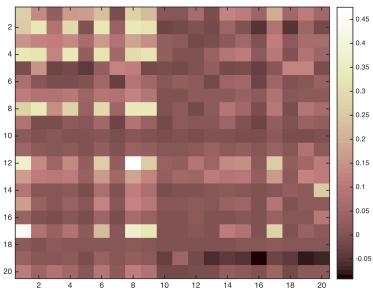

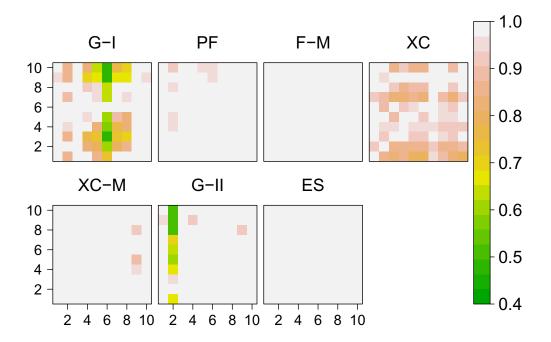

| 3.12 | Envy-free Index - Darker colors mean greater envy. X-axis and Y-axis show 10 users. Matrix items indicates how much these users envy each other (pairwise envy). Simulation parameters: $n_{user} = 100$ , $n_{appPerUser} = 10$ , $n_{server} = 100$ | 67 |

| 3.13 | Sharing Incentives                                                                                                                                                                                                                                    | 70 |

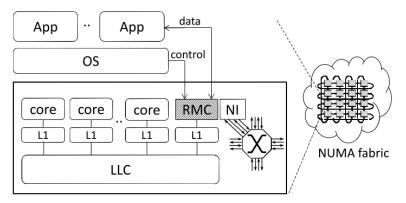

| 4.1  | Scale-out NUMA architecture [81]                                                                                                                                                                                                                      | 78 |

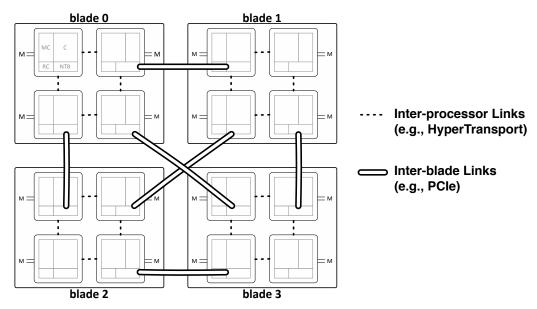

| 4.2  | Blade architecture with sixteen-core processors, four-processor blades, and a four-blade server                                                                                                                                                       | 79 |

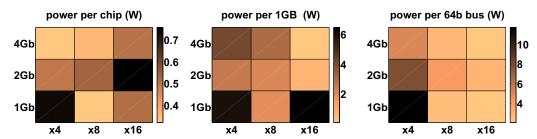

| 4.3  | DRAM power (a) per chip, (b) for 1GB of capacity, (c) for 64b interface. Estimates from Micron [75]                                                                                                                                                   | 80 |

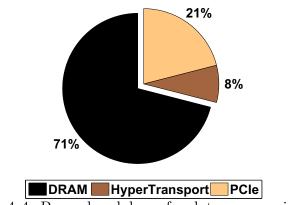

| 4.4  | Power breakdown for data communication                                                                                                                                                                                                                | 84 |

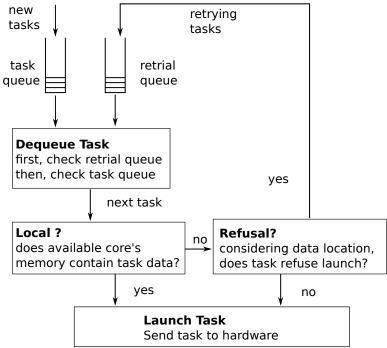

| 4.5  | Refusal policies and queue management                                                                                                                                                                                                                 | 87 |

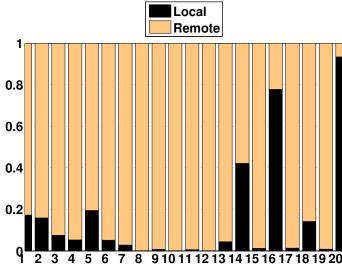

| 4.6  | Local vs Remote Memory Access                                                                                                                                                                                                                         | 91 |

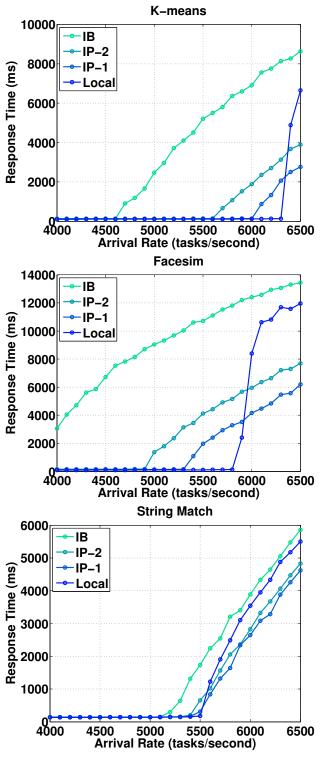

| 4.7  | Throughput as a function of task arrival rate for representative tasks drawn from (a) Spark K-means, (b) Parsec facesim, and (c) MapReduce string match.                                                                                              | 93 |

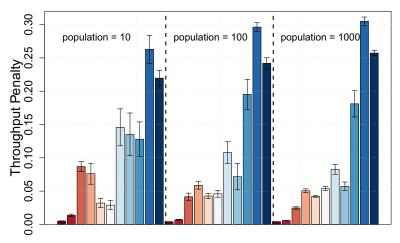

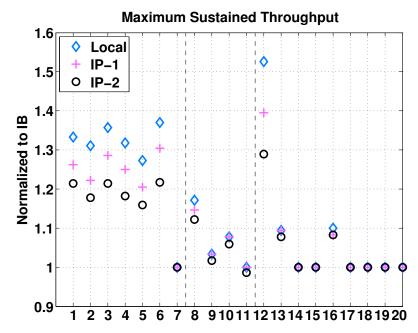

| 95  | Maximum sustained throughput for varied benchmarks indexed in Table 4.2. Vertical dash lines separate benchmark groups: S1-S7, M8-M11, P12-P20. This figure format will be consistent for all the graphs in this section | 4.8  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

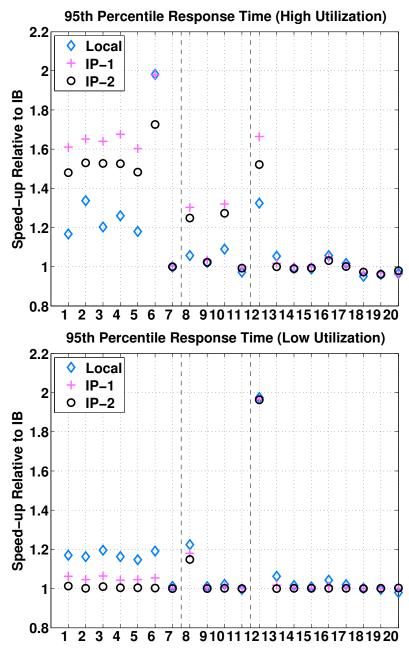

| 97  | 95th percentile response time. Response times normalized to IB policy, which permits all NUMA accesses. Data shown for (a) high server utilization and (b) low server utilization                                        | 4.9  |

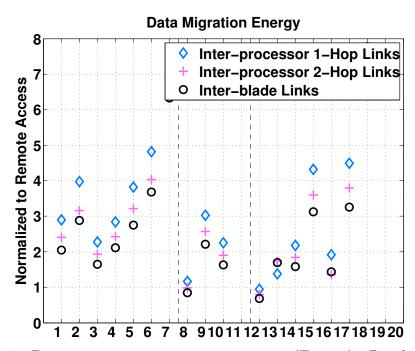

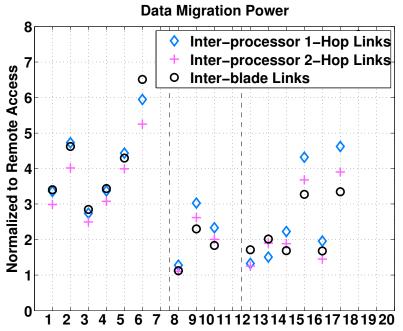

| 101 | 10 Data migration versus remote access (Energy). Benchmarks 18-20 are out of scope; baseline energy is too small for compute-intensive workloads with little memory activity                                             | 4.10 |

| 101 | 11 Data migration versus remote access (Power)                                                                                                                                                                           | 4.11 |

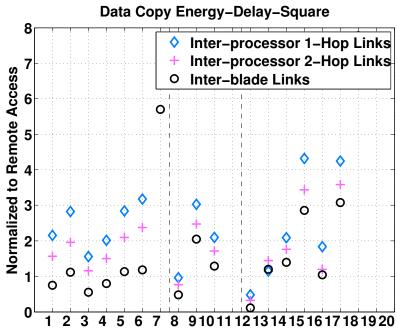

| 102 | 12 Data migration versus remote access $(ED^2)$                                                                                                                                                                          | 4.12 |

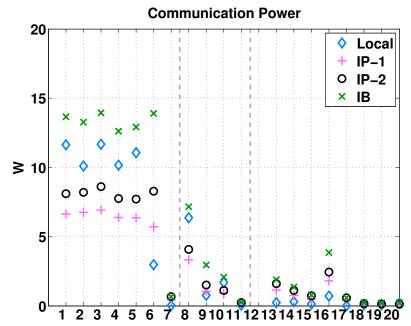

| 103 | 13 Communication power for highly utilized server                                                                                                                                                                        | 4.13 |

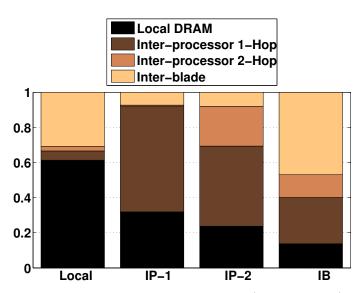

| 104 | 14 Activity distribution across channels (stacked bars) for tasks following one of four refusal policies (x-axis)                                                                                                        | 4.14 |

|     |                                                                                                                                                                                                                          |      |

# Acknowledgements

The journey to this PhD dissertation is long and challenging. Without many people, this dissertation would never have materialized. First of all, I want to thank my adviser, Dr. Benjamin Lee, for giving me the opportunity to work as a Ph.D. student in a great research lab. In the five years we have worked together, he has dedicated many hours to helping me improve my technical research and professional abilities, and our discussions have refined my soft skills and career direction. Dr. Lee was always confident in the quality of our research and sought out the best venues; this dissertation consists of our research that was accepted into a variety of competitive conferences.

The members of my exam committee have all been tremendously helpful during each of my milestones: Dr. Daniel Sorin and Dr. Alvin Lebeck, for their expertise in computer architecture, especially memory systems to help with defining realistic system settings; Dr. Jeffrey Chase, for his expertise in large-scale distributed systems and great research intuition in resource management framework design; and Dr. Gabriel Loh, for his suggestions in performance modeling and project direction as a whole. It is my great honor to have these top researchers in the field on my committee and to be able to discuss my work in depth with them.

This thesis is an interdisciplinary study between computer architecture and algorithmic economics. Without the wisdom in algorithms and economics, it would never have been complete. I would like to extend my thanks to Dr. Vincent Conitzer,

for his valuable input on the micro-economic models and game theory part of my project; two Ph.D. students in algorithms Dr. Janardhan Kulkarni and Brandon Fain for various theory discussions we had on my projects.

I would also like to express my thanks to the professors in Duke Computer Architecture group, especially Dr. Daniel Sorin, Dr. Alvin Lebeck and Dr. Andrew Hilton. Throughout my study in graduate school, I took various computer architecture and system related classes from them to enhance my CS fundamentals; they gave prompt research feedback during my conference practice talks; they led weekly reading group sessions to keep students updated with state-of-art research in the field; and they are always willing to give career advice and connect me to internships or full-time opportunities.

Getting a PhD is a combination of professional development and emotional training. I would like to thank many important people that accompanied me in this unforgettable journey and helped me reach the finishing line: Dr. Marisabel Guevara and Dr. Songchun Fan for their valuable advice on graduate school life, career development and uncountable discussions on my projects which turn to be extremely helpful; Seyed Zahedi for his dedication in our collaborative projects and his incredible knowledge in game theory; my numerous brilliant and talented labmates, Luwa Matthews, Tamara Lehman, George Mappouras, Pengfei Zheng, Ziqiang Huang and Dr. Blake Hechtman, who added the much-needed fun element to my Ph.D. life and form priceless lifelong friendship. And finally, last but by no means least, I would like to thank my husband, my parents, my family and my friends for their continuous support, love and advice throughout this time, regardless of which stage of graduate school I was in. Without their love and encouragement, I would not have had the strength and courage to reach the end.

1

### Introduction

As demands for users' applications' data increase, the world's computing platforms are moving towards more capable machines – servers and warehouse-scale datacenters. Datacenters are large-scale systems equipped with racks of servers. Internet service companies build datacenters to provide web services including search engines, social media, video streaming, email, office tools, and remote storage. Public cloud providers such as Amazon Web Service, Microsoft Azure and Google Cloud rent bare-metal servers or virtual machines along with management platforms to companies and individuals. Private datacenters, such as university department clusters or a company's internal development clusters, provide powerful computing platforms for researchers and developers. Many efforts are dedicated to improve datacenter performance. In hardware, companies like Intel and AMD continuously improve individual servers' capabilities with technology advances, for example, by increasing number of CPU cores, putting accelerators on-chip, adding more memory and building faster storage. In software, system management frameworks deploy resource management policies to improve server utilization and service quality with a much shorter production cycle.

Resource management policies include resource allocation, task scheduling and task colocation. Different techniques are used in different system settings. In some circumstances, users provide resource requirements, such as number of cores, amount of memory or number of virtual machines. This usually happens in public cloud services where users pay for a certain time frame for a fixed amount of resource. In this case, the system manager uses bin packing [38], load balancing [62, 67], live migration, or sophisticated optimization techniques to improve server utilization while monitoring VM service quality. In other circumstances, where applications are submitted to a shared cluster to perform computation, system management software should leverage performance profiling and prediction techniques [27, 70, 113] to infer applications' resource requirements and make resource management decisions based on these performance implications [28, 64].

Predicting datacenter application resource requirements for efficient system management is challenging. First, the prediction has to be fast. Applications are numerous and diverse. Simple heuristics can be effective if applications are similar. Unfortunately, even applications within the same type can behave significantly differently. Batch jobs may be compute intensive, memory intensive or I/O intensive; graph applications may have skewed data sets that change communication patterns. Second, performance prediction has to consider the effects on hardware. For example, colocated applications on the same processor might cause resource contention in the memory subsystem, which impacts performance; servers with large memory have non-uniform memory access that may cause slow response time on critical tasks and may affect the overall application performance. Finally, performance models have to be simple. Finding the optimal solution for resource allocation and scheduling problems is generally combinatorial. Greedy and heuristic strategies can help reduce the problem dimension but require performance models as input. Therefore, keeping a simple, light-weighted model is critical to keep the solution space small and to

make fast management decisions.

System performance is not the only concern for system managers. Conventional wisdom assumes that users must share and policies need only optimize for performance. Such performance goals are suitable for public systems that deliver hardware for which users have paid. In contrast, private systems consist of users who voluntarily combine their resources and subscribe to a common management policy. These users also reserve the right to withdraw from the system if resources are managed poorly. Therefore, privately shared systems must manage resources fairly to encourage participation and guard against strategic behavior [120]. Real-world users are selfish and rational [9, 24], an observation that has motivated numerous gametheoretic perspectives on systems management [16, 32, 36, 85, 119]. Neglecting users' preferences or fairness induces strategic behavior. Users may circumvent policies or break away from shared clusters, redeploying hardware to form smaller, separate systems [36, 82]. Guaranteeing fairness for shared users in system management policies can address these challenges, ensuring system integrity and cluster efficiency.

Microeconomics models are the best practice for studying individual behavior in making decisions regarding the allocation of scarce resources [101]. Market theory is a common microeconomic theory that allocates scarce resources to shared users by establishing a competitive market price. Game theory is another major method in modeling competing behaviors of strategic users; it is widely used in auctions, fair division, social network formation, voting systems, etc. These well-established microeconomic theories provide the foundation for designing system management policies that target shared datacenters with strategic users. In this dissertation, we will use three pieces of work to demonstrate the work flow and effectiveness of this approach. The focus of this thesis is not about exploring various perspectives of microeconomic theories or inventing new theories. Rather, it will focus on formalizing realistic system settings for resource management problems in shared datacenters,

designing concise and accurate performance models to drive management policies, and adapting microeconomic theories to design efficient and fair system management frameworks.

#### 1.1 Organization and Overview of the Dissertation

This thesis aims to improve datacenter applications' performance under the constraint of guaranteeing user fairness. We present three pieces of work that investigate different system management policies, from task colocation to resource allocation to task scheduling, and coordinate the policy design with different performance modeling techniques, from fitting mathematical utility functions to training machine learning models to deploying cross-level simulators.

This thesis is an interdisciplinary study of computer architecture and microeconomics. Compared to prior works in system management and policy design, the key innovation here is exploring theories in the field of microeconomics for management mechanisms that can guarantee fairness while preserving good system performance and adapting these theories to current datacenter resource management problems. At the same time, we show designs for performance models that consider both the underlying hardware and application behavior to drive management mechanisms. This combined approach can better utilize hardware, improve system efficiency and provide attractive outcomes for users in shared systems.

#### 1.1.1 Cooperative Games to Manage Colocation Contention

Datacenter system managers colocate tasks to improve server utilization and energy-proportionality, but often introduce resource contention for shared hardware. In the first work, we discover that traditional performance-centric colocation mechanisms can reduce resource contention but often lead to strategic behavior for shared users in private datacenters. Such strategic behavior harms system stability and cluster

integrity.

Chapter 2 presents the first study on fair task colocation — Cooper, a colocation framework that uses cooperative game theory [76, 80] to formalize interactions between strategic users and to enable fair task colocation. Cooper builds user preference prediction models with collaborative filtering techniques [94] and designs three matching mechanisms to finds stable matches with predicted preferences. Its colocations satisfy preferences and encourage strategic users to participate in shared systems. We find that given Cooper's colocations, users' performance penalties are strongly correlated to their contributions to contention, which is fair according to cooperative game theory. Finally, its colocations preserve system performance; we observe performance within 5% of prior heuristics. (Chapter 2)

#### 1.1.2 Market Mechanism to Allocate Cores for Parallel Applications

In the second work, we consider another datacenter resource management component—resource allocation. Instead of guaranteeing a single application's performance and fairness, we consider scenarios in which each user holds multiple applications and the total performance of all of her applications is the goal. Users share machines in a federated datacenter; each user has an endowment of resources. Users can trade CPU resources from one application to supply another application that will benefit more at the current time.

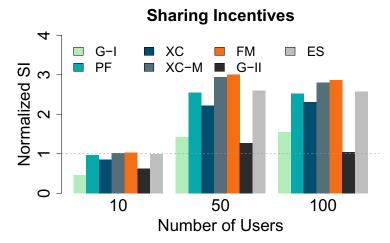

In Chapter 3, we present a performance prediction framework for users' parallel applications with large data sets. We use Amdahl's Law [8] and Karp-Flatt [43] to estimate each application's utility from any core allocation. We validate our performance model with real system measurements of benchmarks from Apache Spark and predict execution time for varied core counts and dataset sizes with an average of 15% error. We propose a Fisher Market that leverages our lightweight performance predictor along with a distributed bidding mechanism to find a market equilibrium [121]. We discover that resulting core allocations outperform state-of-art performance-centric mechanisms with collaborative filtering predictions [94]. More importantly, they provide strong game-theoretical guarantees on envy-freeness, sharing incentives and Pareto-efficiency. (Chapter 3)

#### 1.1.3 Performance and Energy Models for Blade Servers

The previous two works demonstrate the coordinated approach for designing performance models and system management policies In some scenarios, like task scheduling with multiple queues, closed form utility functions can only model simple queue structures (i.e., M/M/1 or M/M/K queues). Complex hardware poses challenges in building fast and accurate performance models for task scheduling. In this work, we investigate datacenter big memory servers — blade servers — which disaggregate memory across multiple blades to provide dense memory capacity for big data applications [60, 61]. Larger memory capacities cause deeper non-uniform memory access (NUMA), which complicates NUMA-aware scheduling policy design [18, 26].

In Chapter 4, we derive technology and architectural models to estimate communication delay and energy for blade servers. Additionally, we propose a multi-stage simulation method with detailed architecture and discrete-event simulators to estimate application performance and communication channel energy costs. These models permit new case studies in delay scheduling to mitigate NUMA and improve the energy-efficiency of data movement. Preliminary results from our case study show that these models can help researchers coordinate NUMA mitigation and task queueing dynamics. We find that judiciously permitting NUMA reduces queueing time, which benefits throughput, latency and energy-efficiency for datacenter workloads like Apache Spark[118]. These findings highlight blade servers' strengths and opportunities when building distributed shared memory machines for data analytics. Finally, our models lay the foundation for estimating communication costs within

memory systems with flexible interconnection technology and topology. Future studies in task scheduling policy design can benefit from these models to optimize for system goals, like performance, fairness, energy-efficiency. (Chapter 4)

#### 1.1.4 Key Contributions of the Thesis

In summary, we make the following contributions in this thesis.

- We define fair task colocation as fair attribution of costs, satisfied user preferences, and stable colocations. We propose the first study on fair colocation with cooperative games and demonstrate that our task colocation framework can provide these system desiderate while preserving system performance. We prototype the task colocation framework in a local cluster with the following system components: system profiler, preference predictor, colocation policies, action recommender and job dispatcher.

- We propose a performance model and a lightweight prediction framework based on Amdahl's Law and Karp-Flatt metric to model parallel applications' performance. We validate the performance model by real system measurements of big data applications. We propose a Fisher Market solution to the multiuser resource allocation problem and a distributed bidding mechanism that leverages the performance models to find a market equilibrium. We show that the resource allocation mechanism can provide game-theoretic desiderata while preserving system performance.

- We provide a detailed model of communication costs for a modern big memory server in latency, power, and energy. We characterize applications' sensitivity to non-uniform memory access with architectural models, and perform a coordinated study of NUMA-aware scheduling policy design and task queueing dynamics with system simulation.

# Task Colocation with Cooperative Games

Modern datacenters, with their increasingly parallel computation and increasingly capable machines, colocate small tasks on big servers. Colocating multiple tasks on each server increases efficiency and energy proportionality [15] but introduces contention for shared resources such as last-level cache capacity and memory bandwidth [96, 99, 122].

In a privately shared system, where strategic users have options to bypass the management policy or opt out from sharing, colocation contention can cause strategic behavior and harm shared system integrity. For example, in a computer science department, three professors (A, B, C) are sharing a cluster equally and working towards a conference deadline. Professor A's applications are mostly memory-intensive. Professor B and C's applications are similar light-weighted applications. If the cluster manager colocates professor A and B's applications together, professor B's applications will suffer great performance losses. Therefore, strategic user (professor) B would migrate his applications to colocate with professor C's application to gain performance. Professor B and C have no incentive to colocate with professor A. If many strategic users are dissatisfied with their colocation assignment and migrate their

applications, the system suffers from non-deterministic performance. If many users opt out and form small shared systems to improve their performance, the system loses its integrity.

One of the many challenges to manage shared systems is ensuring fairness among strategic users and incentivize them to participate in such shared environment. Prior work focuses on colocation policies that improves system performance. It manages colocation performance by controlling contention, which depends on the tasks colocated. Because finding the best colocations requires combinatorial optimization, practical heuristics often colocate tasks if performance penalties are tolerable [27, 70] or use architectural insights to pair applications with complementary resource demands [96, 99].

Conventional wisdom assumes that users must colocate and policies need only mitigate contention. Such performance goals are suitable for public systems that deliver hardware for which users have paid. In contrast, private systems consist of users who voluntarily combine their resources and subscribe to a common management policy. These users also reserve the right to withdraw from the system if resources are managed poorly.

Therefore, privately shared systems must manage resources fairly to encourage participation and guard against strategic behavior. Real-world users are selfish and rational, an observation that has motivated numerous game-theoretic perspectives on systems management [16, 32, 36, 85, 119].

We pursue our system desiderata with cooperative games. Game theory is a framework for analyzing outcomes from strategic behavior. Cooperative games describe how agents' interactions dictate shared outcomes. Such games are well suited for colocation as interference between tasks dictates performance penalties. Cooperative games build a foundation for fair colocation, which encourages strategic users to share. The following summarizes our contributions:

- Fair Colocation. We present the case for three desiderata from colocation:

(i) fair attribution such that more contentious users incur larger penalties, (ii) satisfied preferences such that more users colocate with preferred co-runners, (iii) stable colocations such that fewer users break away from the shared system.

- Cooperative Games. We formalize the colocation game in which users share hardware and contention causes performance losses. When assigning colocations, the game accommodates users' preferences for co-runners. The game's equilibrium produces fair and stable systems.

- Colocation Framework. We present Cooper, a cooperative game that predicts preferences and colocates tasks. It adapts stable matching algorithms to the colocation problem. It then assesses colocations and recommends strategic actions for users.

- Multiprocessor Evaluation. We evaluate Spark and PARSEC jobs that share chip multiprocessors. We show that Cooper's colocations are fair as jobs' performance losses increase with their demands for memory. Colocations also satisfy users' preferences, which encourages sharing. Cooper performs within 5% of prior heuristics.

#### 2.1 Case for Fair Colocation

For the first time, we present the case for fair colocation. In economics, fairness is the equal treatment of equals and the unequal treatment of unequals in proportion to their relevant differences [11, 76]. We say colocations are fair when similar tasks suffer similar performance losses. We argue that, when tasks are dissimilar, the relevant differentiator is contentiousness. Thus, users' performance losses from colocation should increase with their contributions to contention.

We approach fair colocation from a game-theoretic perspective, which formally describes strategic situations, because systems are often shared by strategic users. Cooperative game theory prescribes the fair division of costs that arise from interactions between strategic agents [80]. Solutions to these games reconcile agents' divergent preferences to produce stable outcomes [35, 51]. We use such theories to design colocation policies and build frameworks to manage datacater colocation contention.

#### 2.1.1 Desirable System Desiderata

We manage datacenters that colocate strategic users and their tasks on chip multiprocessors. We define *strategic users* as those who selfishly pursue performance and opt out (or manipulate) management policies when outcomes fail to satisfy their preferences; define *contentiousness* as user demand for shared resources such as memory bandwidth; and define *penalty* as user disutility, such as throughput loss from contention. Cooperative game theory guides us to colocation algorithms that satisfy three system desiderata.

- Fair Cost Attribution. More contentious users incur larger penalties from colocation.

- Satisfied Preferences. More users colocate with their preferred co-runners.

- Stable Colocations. No subset of users benefits by breaking away to share separate subsystem.

#### 2.1.2 Fair Attribution

We argue that a colocation's performance penalties are attributed fairly when more contentious users incur larger penalties. In practice, such fair attribution encourages colocation. Suppose Alice's job is contentious and Bob's is not. If Bob contributes

FIGURE 2.1: Unfair colocations show no link between contentiousness and penalties. We colocate 1000 jobs drawn randomly from an application pool. Pairs of jobs share multiprocessor cache and memory bandwidth. Colocation penalties are averaged over those that include a particular job type (e.g., bodytrack).

little interference but suffers large performance losses when colocated with Alice, he has little *incentive to share*. Bob would rather form his own private cluster than contribute resources to the shared system. As Bob-like users leave the system, Alicelike users dominate and exacerbate contention.

Figure 2.1 highlights unfairness in existing policies. A greedy policy assigns jobs to servers that perform well given prior assignments. A complementary policy pairs jobs with harmonious demands such as compute and memory intensive jobs. Neither policy links contentiousness to penalty (memory intensity and performance loss, respectively). Correlation is the most contentious but penalized no less than Canneal and Dedup under greedy pairing. Dedup is one of the least contentious applications but penalized more than most applications under complementary pairing. These outcomes violate fairness in cost attribution.

Our practical notion of fairness is justified by the notion of Shapley value in cooperative game theory [92]. Shapley determines each agent's fair share of a common outcome based on her contributions. Equation 2.1 shows the Shapley calculation. When applied to colocation,  $\phi_i$  is agent i's fair share of penalty p, which depends on

| Coalition (S) | Penalty (p) | Permutation                                               | $\mathbf{M}_{\mathbf{A}}$ | $\mathbf{M_B}$ | $\mathbf{M_C}$ |

|---------------|-------------|-----------------------------------------------------------|---------------------------|----------------|----------------|

| {A}           | 0           | {A, B, C}                                                 | 0                         | 3              | 3              |

| {B}           | 0           | $\{A, C, B\}$                                             | 0                         | 2              | 4              |

| {C}           | 0           | $\{B, A, C\}$                                             | 3                         | 0              | 3              |

| {A, B}        | 3           | $\{B, C, A\}$                                             | 1                         | 0              | 5              |

| $\{A, C\}$    | 4           | $\{C, A, B\}$                                             | 4                         | 2              | 0              |

| {B, C}        | 5           | $\{C, B, A\}$                                             | 1                         | 5              | 0              |

| $\{A, B, C\}$ | 6           | $\phi_{\mathbf{i}} = \mathbf{E}[\mathbf{M}_{\mathbf{i}}]$ | 1.5                       | 2.0            | 2.5            |

FIGURE 2.2: Shapley permutes users, calculates their contributions to penalties M and expected values  $\phi$  over permutations.

the agents in colocation S.

$$\phi_i(p) = \sum_{S \subset N} \frac{(s-1)!(n-s)!}{n!} \left[ p(S) - p(S-i) \right]$$

(2.1)

Agent i's marginal contribution to colocation penalties is p(S) - p(S - i). Shapley states that her fair share  $\phi_i$  of penalty p is her marginal contribution to those penalties, averaged over the combinations that colocations could form.

Shapley assigns penalties  $\phi$  that correlate with interference I when system penalty is  $p = \sum_{i \in S} I_i$ . System penalty depends on coalition of three users (A,B,C). Shapley permutes users, calculates each user's marginal contribution to penalties  $\mathbf{M}$ , and calculates expected values  $\phi$  over permutations.

We apply Shapley to motivate larger colocation penalties for more contentious users. Consider a simple model of colocation and its contention penalties. Users A, B, and C perform normally when alone but suffer penalties when colocated. Each user contributes interference  $\{I_A = 1, I_B = 2, I_C = 3\}$ . Suppose system-wide penalty is the sum of each user's contribution to interference such that  $p = \sum I_i$ . Shapley determines users' marginal contributions to penalties, averaged over permutations of users in the coalition – see Equation 2.1.

To understand Shapley, suppose n agents arrive sequentially and n! orderings are equally likely. Agent i arrives after agents in coalition S-i and is the s-th agent in S with probability (s-1)!(n-s)!/n!. Agent i's arrival increases coalition penalty

by p(S) - p(S - i).

Figure 2.2 enumerates penalties and orderings for our example. Consider ordering {A, C, B}.

- A's marginal penalty is  $\mathbf{M}_{\mathbf{A}} = v(\mathbf{A}) v(\emptyset) = 0$ ;

- C's marginal penalty is  $\mathbf{M}_{\mathbf{C}} = v(AC) v(A) = 4;$

- B's marginal penalty is  $\mathbf{M_B} = v(ABC) v(AC) = 2$ .

Each user's Shapley value is her average marginal contribution to penalties across permutations. From Shapley, a fair assignment of penalties is  $\phi = \{1.5, 2.0, 2.5\}$ , which correlates with users' contributions to interference  $I = \{1, 2, 3\}$ .

Shapley is an analytical framework, which is not meant for direct application because it unrealistically assumes performance losses can be transferred arbitrarily between colocated agents. Nonetheless, Shapley provides the theoretical foundation for a realistic fairness goal—larger losses for more contentious jobs. In practice, colocation policies pursue this goal by assigning co-runners that dictate performance losses.

#### 2.1.3 Satisfied Preferences and Stability

Stability leads to an equilibrium state which satisfy user preferences and strengthen system integrity. Figure 2.3 illustrates instability from existing policies. Suppose four users share two processors and suffer from contention in the memory subsystem. A colocation policy minimizes system-wide penalties with colocations {AD, BC}. However, these colocations do not satisfy preferences – pairing A with D even though A prefers D least. In addition, they are unstable as A and B prefer each other over their co-runners. If A and B break away to form a separate subsystem to improve their utility, the datacenter fragments and efficiency suffers. In contrast,

FIGURE 2.3: Users' penalties determine preferences for co-runners. Pursuing performance minimizes system penalties. Pursuing stability satisfies user preferences. The four users in this dataset are: (A) x264, (B) fluidanimate, (C) decision-tree, (D) regression.

stable colocations {AB, CD} satisfy three of four users' preferences – A, B and D's. Moreover, no pair wants to break away to form their own subsystem.

Figure 2.4 indicates that stability enhances fairness whereas the pursuit of performance does not. When optimizing system-wide performance, user C sees the smallest performance penalty although it is most memory-intensive (1%, 21 GB/s). Users A and B see the largest penalties although they are least contentious (4-9%, 4-5 GB/s). In comparison, stability-centric policies more closely align penalties with memory intensity. The penalty for the most contentious user rises while those for less contentious users fall. Stability, although imperfect, furthers the fair attribution of costs in shared systems.

#### 2.2 The Colocation Game

We present a game-theoretic framework that colocates software on shared hardware in a multi-user setting. Our framework is an alternative to heuristics that myopically maximize performance. The colocation game balances the pursuit of performance with the provision of fairness, which encourages strategic users to share hardware.

FIGURE 2.4: Stability enhances fairness. Bars show user penalty based on throughput loss under performance- and stability-centric colocation policies. Dots show user contentiousness, based on bandwidth demand when alone. Data for four users: (A) x264, (B) fluidanimate, (C) decision-tree, (D) regression.

#### 2.2.1 System Setting

We consider a shared cluster with homogeneous processors, each with multiple cores, that serve batch and offline computation. The colocation game batches and assigns arriving jobs to available processors periodically. The length of the scheduling period is comparable to job completion times (i.e., minutes rather than seconds or milliseconds). If the system is heavily loaded, jobs queue for scheduling.

Figure 2.5 illustrates an architecture for the colocation game, which defines abstraction layers – agents and coordinator – between users and machines. Agents act on users' behalf within the game, shielding users from complex management mechanisms. The coordinator communicates system information to agents and implements management mechanisms.

Agents play three roles when interfacing with the coordinator. First, agents query the coordinator's profiler to obtain job performance under varied colocations. Second,

FIGURE 2.5: Agents act on users' behalf, playing the colocation game and interfacing with the system coordinator. The agents and the coordinator shield hardware complexity from human users.

they use profiles to predict preferences for co-runners and influence the coordinator's colocation assignments. Third, agents assess assigned colocations and recommend strategic actions to users. An agent recommends participation when assignments satisfy preferences. Otherwise, an agent recommends better colocations with others.

#### 2.2.2 Game Formulation

We formulate colocation as a cooperative game in which users form coalitions to share hardware and divide penalties from resource contetion. We define the game's components, introduce actions, and present solution concepts.

Agents, Disutility, and Preferences. An agent represents a user and her job. In a given epoch, the colocation game assigns 2N agents to N chip multiprocessors. Colocated agents comprise a coalition who contribute to shared contention and performance penalties. Each agent defines disutility  $d \in [0, 1]$ .

$$d = 1 - \frac{\text{Throughput}_{\text{colocation}}}{\text{Throughput}_{\text{stand-alone}}}$$

Disutility quantifies a colocation's performance penalty. For example, d = 0.3

when a job's colocated performance is  $0.7 \times$  that of its stand-alone performance, all else being equal (e.g., allocation of processor cores). Disutility dictates an agent's preferences for co-runners. Let  $\succ_i$  denote agent *i*'s preferences. If *i*'s disutility with x is lower than its disutility with y, then  $x \succ_i y$ . In other words, i performs better with x than with y.

Strategic Action. The datacenter operator would like all agents to share one monolithically managed cluster to enhance efficiency. However, subsets of agents could determine that a colocation policy provides better individual outcomes when applied to separately managed clusters. Agents would then create subsystems shared by mutually preferred co-runners. Breaking away is the act of finding a subset of agents who form new coalitions on separately shared subsystems to improve their performance.

Blocking Coalitions and Equilibria. Agents who break away to pursue better outcomes together comprise a blocking coalition. Let C denote a datacenter's colocations and C(i) denote i's co-runner, assuming two users share a chip multiprocessor. Agents i and j are blocking if they prefer each other over their co-runners:  $j >_i C(i)$  and  $i >_j C(j)$ . Colocations with fewer blocking pairs are more stable.

Stability is a system outcome that minimizes the number of blocking pairs, producing equilibria in which all agents participate in the shared system. In equilibrium, no subset of agents can better satisfy preferences and improve performance by deviating from assigned colocations. In contrast, neglecting preferences produces blocking pairs and harms stability.

#### 2.2.3 Game Solutions

Stable matching is a natural fit for colocation. A matching process builds pairwise coalitions based on mutual consent from independent, strategic agents. Matches are stable when no pair of agents prefers each other over their existing partners. We draw

## Algorithm 1 Stable Marriage for Colocation Game

```

1: sets M, W \leftarrow 2N tasks such that |M| = |W| = N

2: lists P[i] \leftarrow \text{ordered preferences } \forall i \in M, W

3: single(i) \leftarrow True \ \forall i \in M, W

4: while \exists single(m) \in M, P[m] \neq \emptyset do

w \leftarrow P[m]

if single(w) then

7:

pair(m, w)

8:

if (m', w) paired, but m >_w m' then

9:

pair(m, w)

10:

single(m') \leftarrow True

P[m] \leftarrow P[m].next

11:

```

inspiration from stable algorithms for marriage [40] and roommate assignment [51], adapting them to the colocation game.

**Stable Marriages.** The stable marriage algorithm solves the colocation problem with two sets of agents. Agents in one set propose colocations while those in the other accept or reject them. Agents act strategically to pursue their preferred co-runners.

Algorithm 1 sketches the procedure for finding stable marriages between two sets of jobs, which are labeled M and W. Job m proposes to w according to its ordered preferences. Job w accepts when it prefers m over its current co-runner m. If w rejects, m proposes to its next preferred co-runner. The procedure iterates until all jobs are matched. In each round, all jobs in M propose to their top-ranked co-runners simultaneously. Each job in W accepts its best proposal and rejects the rest in parallel. Those in M that are not accepted proceed to the next round. The procedure continues until all jobs are matched.

The procedure provides stable colocations in which no two agents from opposite sets can break away and improve their utility [35]. Every job in M has one successful proposal because a job in M that had all prior proposals rejected is accepted by the least desirable job in W. Stability arises from accepted proposals. Suppose m prefers w' over its co-runner w. Because m and w' are not colocated, m must have proposed to w' only to have been rejected because w' preferred m'. Matches are stable because  $m' >_{w'} m$  even though  $w' >_m w$ .

| Preferences            | Round | Propose                                   | Accept      | Reject |

|------------------------|-------|-------------------------------------------|-------------|--------|

| $m_1: c_1 > c_2 > c_3$ | 1     | $m_1 \rightarrow c_1$                     | $c_1 - m_3$ | $m_1$  |

| $m_2:c_3>c_1>c_2$      |       | $m_1 \to c_1$ $m_2 \to c_3$ $m_3 \to c_1$ | $c_3 - m_2$ |        |

| $m_3:c_1>c_2>c_3$      |       | $m_3 \rightarrow c_1$                     | $c_2-$      |        |

| $c_1: m_2 > m_3 > m_1$ | 2     | $m_1 \rightarrow c_2$                     | $c_2 - m_1$ |        |

| $c_2: m_3 > m_1 > m_2$ |       |                                           |             |        |

| $c_3: m_2 > m_1 > m_3$ |       |                                           |             |        |

FIGURE 2.6: Stable marriage with compute- and memory-intensive jobs.

Adapting Partitions and Proposals. Stable marriage matches jobs from two disjoint sets, requiring a job partitioning strategy. Some strategies arise from the system. High- and low-priority jobs should be partitioned, as should compute- and memory-intensive jobs. When domain expertise indicates jobs within a set should not colocate with each other, marriage is a solution that precludes intra-set matches.

The algorithm can also partition jobs randomly. In large systems with diverse jobs, random partitions uniformly distribute jobs of all types across two sets. Stable marriages are more likely when each set holds diverse jobs, not just memory-intensive ones. Diverse preferences produce diverse proposals and reduce the likelihood of common, desirable co-runners. Random partitions are as effective as sophisticated ones for satisfying preferences.

We implement two partitioning mechanisms — partition based on applications' memory intensity and partition randomly. Partitioning by memory intensity reflects the source of hardware contention and tends to favor performance. Partitioning randomly neglects inherent job characteristics and tends to favor fairness.

Agents that propose perform nearly optimally and better than those that receive proposals [52]. Proposers choose co-runners in order of their preferences where as those that receive proposals have no influence on their suitors. Agents accept or reject without knowing which job might propose next. In practice, we find that proposers' advantages are small, especially for randomly partitioned jobs.

Stable Marriage Example. Figure 2.6 presents an example of stable marriage.

First, the system partitions memory- and compute-intensive jobs (m and c), based on memory bandwidth demands. Second, agents profile and predict preferences, ranking candidate co-runners in the opposite set. Finally, jobs in set m propose to those in set c. Specifically,  $m_1$  and  $m_3$  both propose to  $c_1$ . Based on its preferences,  $c_1$  accepts  $m_3$  and rejects  $m_1$ . Simultaneously,  $m_2$  proposes to  $c_3$ , which accepts as it lacks a better proposal. Rejected,  $m_1$  proposes to  $c_2$  in the next round. Lacking a proposal,  $c_2$  accepts and the algorithm terminates with colocation  $\{m_1c_2, m_2c_3, m_3c_1\}$ .

Stable Roommates. Roommate assignment provides a natural alternative to marriage when an agent may match with any other. Irving provides a generalized matching algorithm [51]. First, each agent proposes sequentially to preferred roommates while simultaneously receiving proposals from others. An agent rejects a proposal if she already holds a better one and accepts otherwise. If any agents are rejected by everyone, the algorithm terminates and states that no perfectly stable solution exists. If all agents hold successful proposals, each agent reduces her preference list by deleting roommates that are less desirable than proposals they hold. The algorithm further reduces preference lists by eliminating preference cycles (e.g.,  $B >_A C$ ,  $C >_B A$ ,  $A >_C B$ ). The algorithm terminates when no cycle exists and produces stable roommate assignments.

Adapting Stable Roommate. Stable roommate assignment does not always produce a solution. We extend the algorithm with heuristics when no stable solution exists. When Irving's algorithm terminates with no solution, we greedily pair unmatched agents to minimize their pair disutilities. In practice, stable roommate assignments rarely exist for large agent populations. For such settings, our adapted algorithm significantly reduces the number of blocking pairs.

**Limitations.** In theory, stable-matching problems with arbitrary group size can not be solved in polynomial time. Only in the instance of a pair-wise stable roommate problem, does a polynomial algorithm exist [51]. However, if no stable

matching exists, minimizing the number of blocking pairs is NP-hard and hard to approximate [6]. One approximation relaxes stability, defining an  $\alpha$ -stable system in which agents form blocking pairs only when gains exceed a factor of  $\alpha$  [12].  $\alpha$ -stability is particularly relevant when agents set thresholds that reflect the costs of breaking away. For example, colocated jobs deploy separately managed subsystems only to avoid large performance penalties.

In practice, finding a stable matching or  $\alpha$ —stable matching for an arbitrary group size is hard and may not be necessary. When colocating more than two data intensive applications on the same processor, the resource competition caused in the memory subsystem (share last level cache and memory bandwidth) is large and causes high performance penalties. This system scenario happens rarely.

In sum, stable matching solves the colocation game efficiently. The solution satisfies preferences and preempts strategic behavior. In theory, marriage and roommate algorithms find pairwise matches in polynomial time. In practice, overheads are modest in our implementation.

# 2.3 Cooper Colocation Framework Design

We design and implement Cooper, a cooperative game that provides the management desiderata, fair colocations for strategic users, satisfies users' preferences and stability. It enhances shared user fairness, safeguard the integrity and efficiency of the shared system.

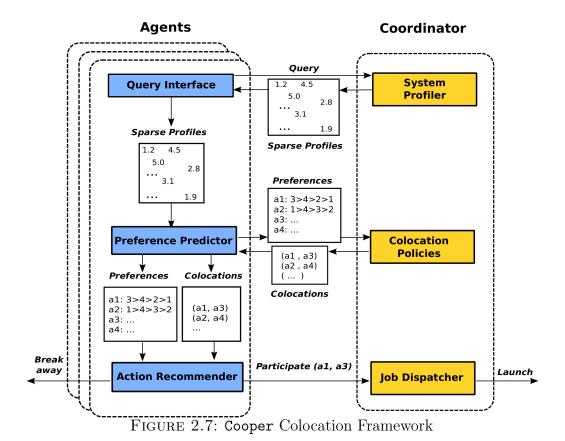

Figure 2.7 illustrates Cooper's architecture and components. Decentralized agents act on behalf of users to pursue preferred colocations. Each agent instantiates three modules. The query interface requests profiles for sparsely observed colocations. The preference predictor estimates performance for unobserved colocations. The action recommender assesses assigned co-runners and suggests user action.

To support agents, Cooper implements a centralized coordinator with three mod-

ules. The system profiler responds to queries with a database of performance measurements. Colocation policies assign co-runners based on agents' preferences. The job dispatcher assigns computation to machines when agents choose to participate.

Cooper's design emphasizes intelligent agents that separate strategic users from the shared system. From the user's perspective, the system delivers fairness and stability to encourage participation. Users rely on agents to assess colocations and recommend strategic action. From the system's perspective, agents pursue preferred colocations independently.

# 2.3.1 Preference Predictor

The predictor receives performance profiles and estimates preferences for co-runners. It uses sparsely profiled colocations to infer a preference list that ranks co-runners by the agent's expected performance. The game's matching algorithms use preferences to find stable colocations.

In principle, users could report preferences directly to the system coordinator; however, they are poorly equipped to assess preferences for each co-runner. Because self-reported preferences can be burdensome, inaccurate, and non-truthful, Cooper relies on agents' predictors.

Collaborative Filtering. Agents employ light-weight predictors to estimate preferences. Determining preferences for each co-runner via direct measurement is intractable. Fortunately, predicting agents' preferences from sparse performance profiles is analogous to predicting consumers' preferences from sparse product ratings. Predictors treat jobs as consumers, co-runners as products, and profiles as ratings.

Collaborative filtering trains predictors, observing that consumers who rate many items similarly share preferences for other items. Cooper implements item-based collaborative filtering, predicting that a co-runner affects similar agents similarly. When a co-runner degrades one task's performance, it will similarly degrade another's. Cooper implements IBCF because it emphasizes similarity in contention's sources and effects. If  $x_1 >_{y_1} x_2$  and  $x_3$  is similar to  $x_2$ , IBCF infers that  $x_1 >_{y_1} x_3$ .

Implementation. We preferences using an R library – recommenderlab [74]. For n agents, a sparse  $n \times n$  matrix M[x, y] reports x's performance with co-runner y. In each iteration, the recommender predicts the unknown ratings in the matrix while minimizing error for known values. Iterations terminate when all matrix elements are filled. In practice, this process requires one to three iterations and completes within 100ms for 1000 agents.