# COMPUTATIONAL SPRINTING: EXCEEDING SUSTAINABLE POWER IN THERMALLY CONSTRAINED SYSTEMS

Arun Raghavan

A DISSERTATION

in

Computer and Information Science

Presented to the Faculties of the University of Pennsylvania

in

Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

2013

Milo M. K. Martin, Associate Professor of Computer and Information Science Supervisor of Dissertation

> Val Tannen, Professor of Computer and Information Science Graduate Group Chairperson

> > **Dissertation Committee**

André DeHon, Professor of Electrical and System Engineering

Zachary Ives, Associate Professor of Computer and Information Science

Jonathan M. Smith, Professor of Computer and Information Science

David Brooks, Professor of Computer Science, Harvard University

### COMPUTATIONAL SPRINTING: EXCEEDING SUSTAINABLE POWER IN THERMALLY CONSTRAINED SYSTEMS COPYRIGHT

2013

Arun Raghavan

To my parents.

## Acknowledgments

Milo Martin has been my advisor through my years in graduate school. Beyond his profound contributions to all our published research, he has influenced how I think, read, write and present my work. I hope I continue to benefit from his advise in the years ahead.

Soon after Milo and I had the first conversation about sprinting and ran through some backof-the-envelop calculations, Tom Wenisch (Michigan) shared our impressions of initial disbelief and cautious optimism. He immediately brought on board Kevin Pipe and Marios Papaefthymiou (both from the University of Michigan) whose added expertise in thermal and electrical engineering respectively gave this project the required critical mass. Milo, Tom, Kevin and Marios were hence instrumental in the inception of this project and continue the active collaboration as of this writing.

Yixin Luo and Anuj Chandawalla performed the SPICE experiments for the many-core activation sequence under Marios' supervision at Michigan. Lei Shao put together and experimented with several phase-change heatsinks (including those used in this dissertation) and is continuing to work on thermal aspects of sprinting under Kevin's supervision at Michigan. Laurel Emurian at Penn helped put together adrenaline-2 and adrenaline-3 (the successor sprinting testbeds to adrenaline-1) and reported the first successes with sprint-and-rest for sustained workloads. Kris and SSVR read through drafts of this dissertation, catching several bugs and improving the English. Drew Hilton created the multicore x86 simulator used in Chapter 4.

Amir Roth and E. Lewis (and Milo, of course) helped make the Architecture and Compilers Group (ACG) at Penn my venue for grad school. Amir taught me CIS 501 during the first year (my first ever college level computer architecture course), hired me as teaching assistant during the next, and left me with an indelible classroom experience. Anne, Colin, Drew, Tingting and Vlad welcomed me as a fellow student into ACG. Colin helped make my initial experiences with research successful, co-authored my first couple of publications and taught me much along the way. Most of

my years in Levine 614 were spent alongside Drew and Santosh, and later Abhishek, Christian and Laurel (and sometimes Sela). They shared the SGE cluster with me before deadlines, helped debug code, and offered feedback on papers. Adam and Emily joined the ACG folks in sitting through several practice talks, patiently guiding each iteration towards a better version.

Rajeev, Sudipto and Benjamin Pierce taught excellent courses which gave me an appreciation for theory, even if I quickly learned that it wasn't my cup of tea. Instead, I was happy to collaborate with Abhishek, Jyotirmoy, Sela, Milo and Rajeev on a PLDI paper which included a lot of Greek.

I turned to Mike Felker for any departmental requirement and he responded with incredible efficiency every single time. Mark, Amy, Gail, Towanda and Lillian at the Moore Business Office facilitated equipment orders, reimbursed travels and even replaced my stolen laptop. Brittany, Charity, Cheryl, Maggie and Marissa helped with booking conference rooms, projector rentals and receiving shipments. Chip, Dan and the good folks at CETS managed the cluster, desktops and even helped with technical queries when setting up the adrenaline machines.

Doug Carmean, Mike Upton and Mark Davis hosted me as an intern with the Larrabee architecture team in Intel Hillsboro. Besides the opportunity to work on architectural exploration of a slated product, I enjoyed the conversations with several brilliant industry veterans.

Finally I would like to thank my dissertation committee—David Brooks, Andre' DeHon, Zack Ives and Jonathan Smith, who offered valuable direction after my proposal towards guiding the goals of this dissertation, and improved this document with their feedback. It has been a privilege to have them on my committee.

#### ABSTRACT

#### COMPUTATIONAL SPRINTING: EXCEEDING SUSTAINABLE POWER IN THERMALLY CONSTRAINED SYSTEMS

Arun Raghavan

Milo M. K. Martin

Although process technology trends predict that transistor sizes will continue to shrink for a few more generations, voltage scaling has stalled and thus future chips are projected to be increasingly more power hungry than previous generations. Particularly in mobile devices which are severely cooling constrained, it is estimated that the peak operation of a future chip could generate heat ten times faster than than the device can sustainably vent.

However, many mobile applications do not demand sustained performance; rather they comprise short bursts of computation in response to sporadic user activity. To improve responsiveness for such applications, this dissertation proposes *computational sprinting*, in which a system greatly exceeds sustainable power margins (by up to  $10\times$ ) to provide up to a few seconds of high-performance computation when a user interacts with the device. Computational sprinting exploits the material property of *thermal capacitance* to temporarily store the excess heat generated when sprinting. After sprinting, the chip returns to sustainable power levels and dissipates the stored heat when the system is idle.

This dissertation: (i) broadly analyzes thermal, electrical, hardware, and software considerations to analyze the feasibility of engineering a system which can provide the responsiveness of a platform with 10× higher sustainable power within today's cooling constraints, (ii) leverages existing sources of thermal capacitance to demonstrate sprinting on a real system today, and (iii) identifies the energy-performance characteristics of sprinting operation to determine runtime *sprint pacing* policies.

# Contents

| 1 | Intr | oduction                                                                  | 1  |

|---|------|---------------------------------------------------------------------------|----|

|   | 1.1  | Bursty versus Sustained Computation: Re-examining Thermal Constraints     | 2  |

|   | 1.2  | Computational Sprinting Overview                                          | 4  |

|   | 1.3  | Dissertation Structure and Goals                                          | 7  |

|   | 1.4  | Differences from Previously Published Versions of this Work               | 9  |

| 2 | Bac  | kground on Dark Silicon                                                   | 10 |

|   | 2.1  | Basic Transistor Operation and Dennard Scaling                            | 11 |

|   | 2.2  | Static Power and the Limits of Dennard Scaling                            | 13 |

|   | 2.3  | Thermal Design Power and Dark Silicon                                     | 14 |

|   | 2.4  | Approaches to Mitigate Dark Silicon                                       | 15 |

|   | 2.5  | Dark Silicon in Mobile Chips                                              | 16 |

|   | 2.6  | Chapter Summary                                                           | 17 |

| 3 | Bac  | kground on Thermal Response                                               | 18 |

|   | 3.1  | Sustainable Operation at Thermal Design Power: Role of Thermal Resistance | 19 |

|   |      | 3.1.1 Thermal Resistance                                                  | 19 |

|   |      | 3.1.2 Thermal Design Power (TDP)                                          | 20 |

|   | 3.2  | Transient Temperature: The Role of Thermal Capacitance                    | 21 |

|   |      | 3.2.1 Thermal capacitance                                                 | 21 |

|   |      | 3.2.2 Transient thermal analysis                                          | 21 |

|   | 3.3  | Thermal Transient due to Latent Heat of Phase Change                      | 24 |

|   |      | 3.3.1 Phase-change while heating                                          | 25 |

|   |      | 3.3.2      | Phase-change While Cooling                                                   | 26 |

|---|------|------------|------------------------------------------------------------------------------|----|

|   |      | 3.3.3      | Thermal State of a System with PCM                                           | 27 |

|   | 3.4  | Model      | ing a System using a Thermal R-C Network                                     | 28 |

|   | 3.5  | Therm      | al-aware Computing                                                           | 29 |

|   |      | 3.5.1      | Dynamic Thermal Management                                                   | 29 |

|   |      | 3.5.2      | Thermal-aware Design and Layout                                              | 31 |

| 4 | Feas | sibility S | Study of Computational Sprinting                                             | 32 |

|   | 4.1  | A The      | rmally-augmented System for Sprinting                                        | 33 |

|   |      | 4.1.1      | Thermal Resistance, Thermal Design Power, and Thermal Capacitance            | 34 |

|   |      | 4.1.2      | Sprinting on a System Augmented with Phase Change Material                   | 35 |

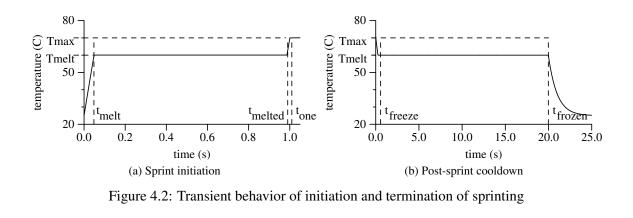

|   |      | 4.1.3      | Temperature Transients of Sprinting with Phase-change Change Materials .     | 36 |

|   | 4.2  | Archit     | ectural Evaluation                                                           | 37 |

|   |      | 4.2.1      | Simulation Methodology                                                       | 37 |

|   |      | 4.2.2      | Workloads                                                                    | 38 |

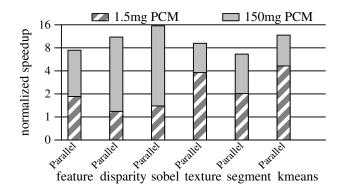

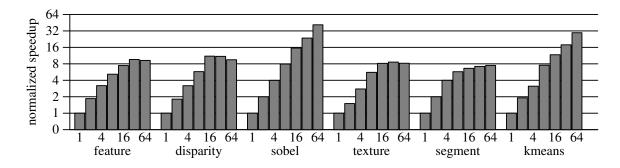

|   |      | 4.2.3      | Increased Responsiveness                                                     | 41 |

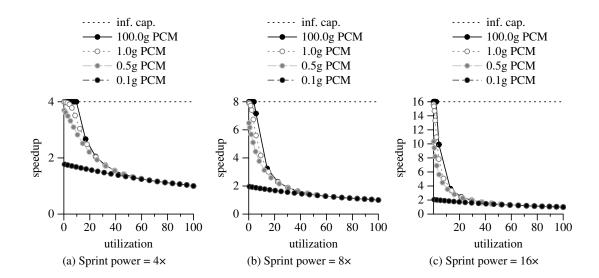

|   |      | 4.2.4      | Thermal Capacitance Design Point                                             | 42 |

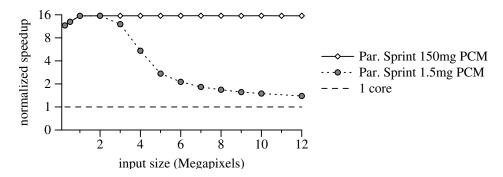

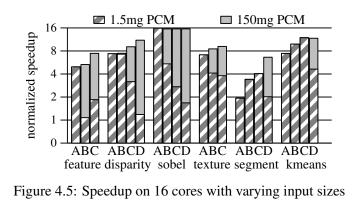

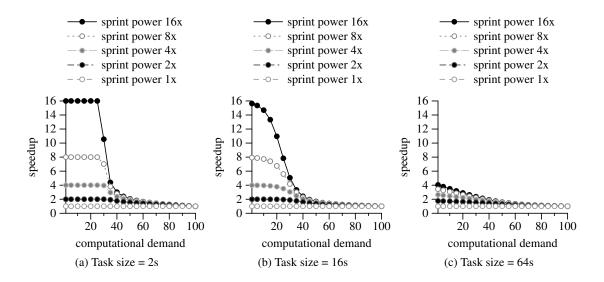

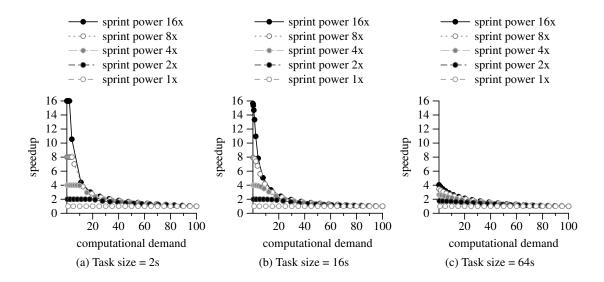

|   |      | 4.2.5      | Varying Intensity of Parallel Sprinting                                      | 43 |

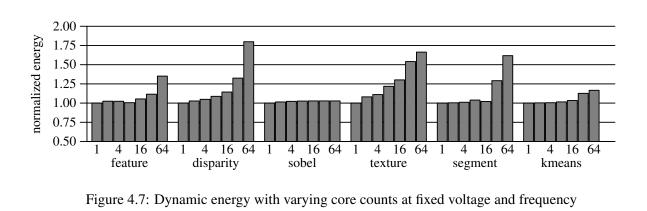

|   |      | 4.2.6      | Dynamic Energy Analysis                                                      | 44 |

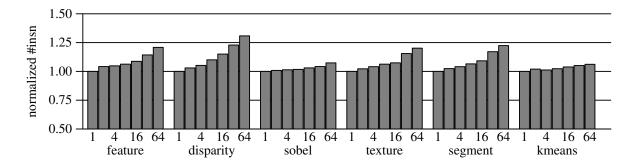

|   |      | 4.2.7      | Instruction Overheads                                                        | 44 |

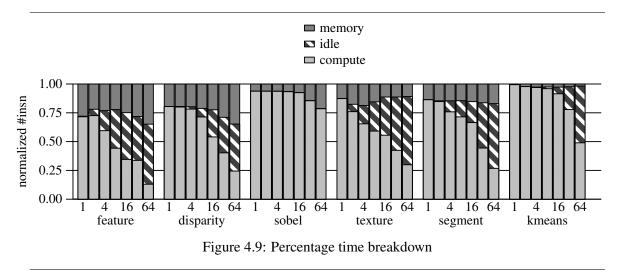

|   |      | 4.2.8      | Runtime Breakdown                                                            | 44 |

|   | 4.3  | Multip     | le Sprints                                                                   | 46 |

|   |      | 4.3.1      | Usage Model                                                                  | 46 |

|   |      | 4.3.2      | How is Sprinting Performance Sensitive to Device Utilization?                | 47 |

|   |      | 4.3.3      | Periodic Computation Bursts: The Case for a Thermal Hierarchy                | 50 |

|   |      | 4.3.4      | Further Considerations to Multiple Sprints: Energy-efficiency and Scheduling | 53 |

|   | 4.4  | Discus     | ssion on Sources of Thermal Capacitance                                      | 53 |

|   |      | 4.4.1      | Heat Storage Using Solid Materials                                           | 54 |

|   |      | 4.4.2      | Heat Storage Using Phase Change                                              | 56 |

|   | 4.5  | Supply     | ving Peak Power                                                              | 58 |

|   |      | 4.5.1      | Conventional Batteries in Mobile Devices                                     | 59 |

|   |     | 4.5.2   | Ultracapacitors                                           | 62 |

|---|-----|---------|-----------------------------------------------------------|----|

|   |     | 4.5.3   | Hybrid Energy Storage Systems                             | 63 |

|   |     | 4.5.4   | Voltage Regulation and Supply Pins                        | 64 |

|   |     | 4.5.5   | On-chip Voltage Stability                                 | 66 |

|   | 4.6 | Hardw   | vare-Software Interface for Sprinting                     | 66 |

|   | 4.7 | Impact  | t of Sprinting on Reliability                             | 69 |

|   | 4.8 | Impact  | t of Sprinting on Cost                                    | 71 |

|   | 4.9 | Chapte  | er Summary                                                | 71 |

|   |     | 4.9.1   | Summary of Findings                                       | 71 |

|   |     | 4.9.2   | Next Steps                                                | 72 |

| 5 | The | rmal Re | esponse of Sprinting on A Hardware/Software Testbed       | 74 |

|   | 5.1 | Unmo    | dified System                                             | 76 |

|   |     | 5.1.1   | Configuration and Monitoring                              | 76 |

|   |     | 5.1.2   | Processor Power Profile                                   | 77 |

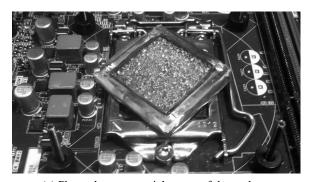

|   | 5.2 | Constr  | ructing a Sprinting Testbed                               | 78 |

|   |     | 5.2.1   | Constraining Heat Dissipation                             | 78 |

|   |     | 5.2.2   | Thermal Capacitance from Internal Heat Spreader           | 80 |

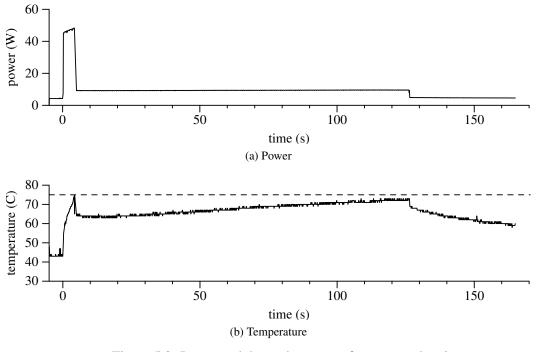

|   | 5.3 | Testbe  | d Power and Thermal Response while Sprinting              | 82 |

|   |     | 5.3.1   | Sprinting with Maximum Intensity                          | 82 |

|   |     | 5.3.2   | Sprinting with Lower Intensity                            | 83 |

|   |     | 5.3.3   | Effect of Non-uniform Thermal Capacitance                 | 84 |

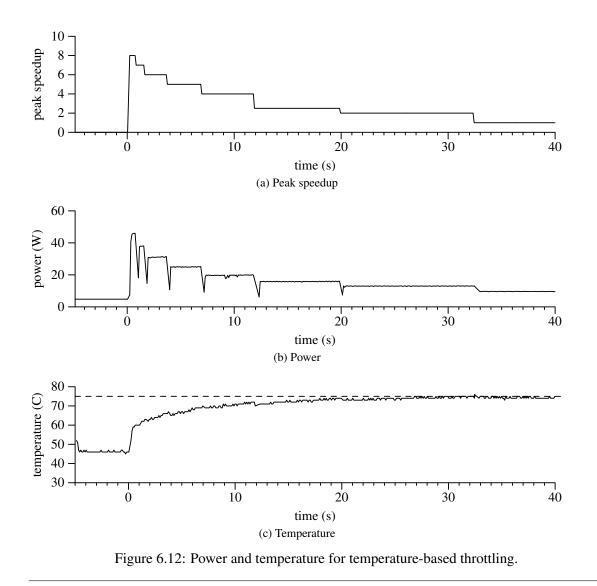

|   | 5.4 | Trunca  | ating Sprints when the Chip Reaches Threshold Temperature | 84 |

|   |     | 5.4.1   | Implementing Sprint Truncation                            | 85 |

|   |     | 5.4.2   | Thermal Response of Truncated Sprinting                   | 85 |

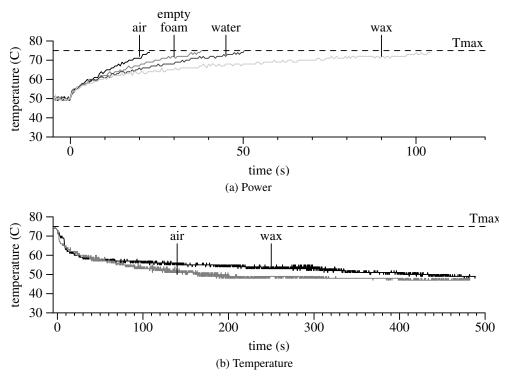

|   | 5.5 | Extend  | ling Sprint Duration with Phase-change Material           | 86 |

|   |     | 5.5.1   | Heating Transient                                         | 87 |

|   |     | 5.5.2   | Cooling Transient                                         | 88 |

|   | 5.6 | Limita  | tions of Testbed                                          | 88 |

|   | 5.7 | Chapte  | er Summary                                                | 89 |

| 6 | Res | ponsive  | ness and Energy Consumption of Sprinting on a Real System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 91  |

|---|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

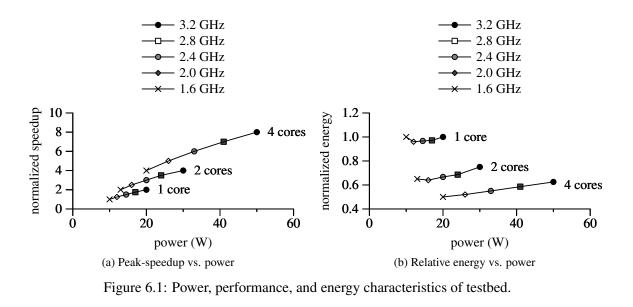

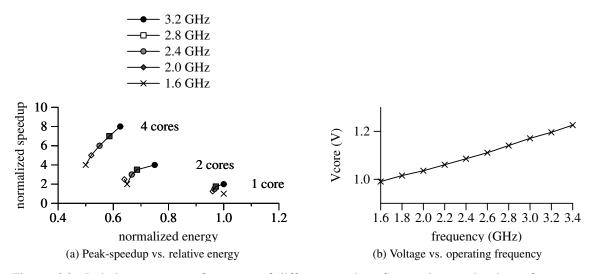

|   | 6.1 | Testbe   | d Characterization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 92  |

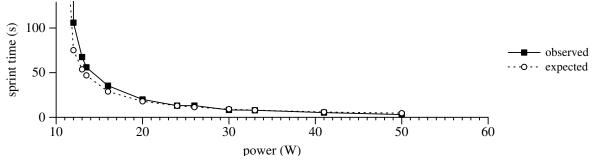

|   |     | 6.1.1    | Estimating Peak Performance and Energy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 93  |

|   |     | 6.1.2    | Power-constrained Performance and Energy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 94  |

|   | 6.2 | Speedu   | up and Relative Energy of Unabridged Sprints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 96  |

|   |     | 6.2.1    | Experimental Methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 96  |

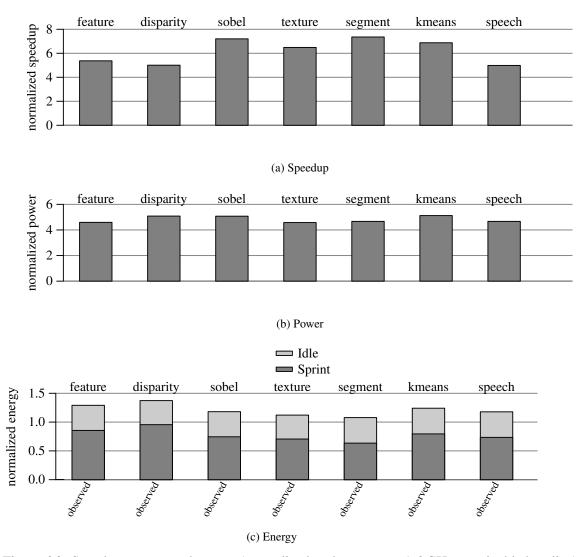

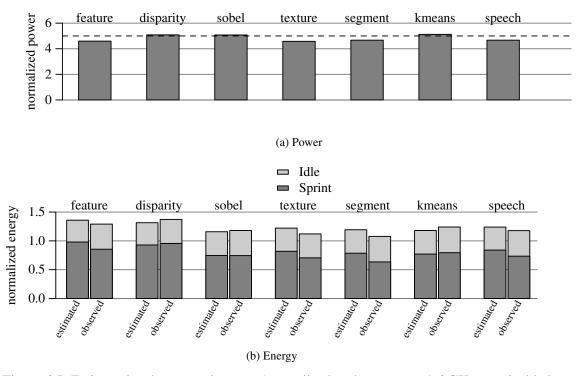

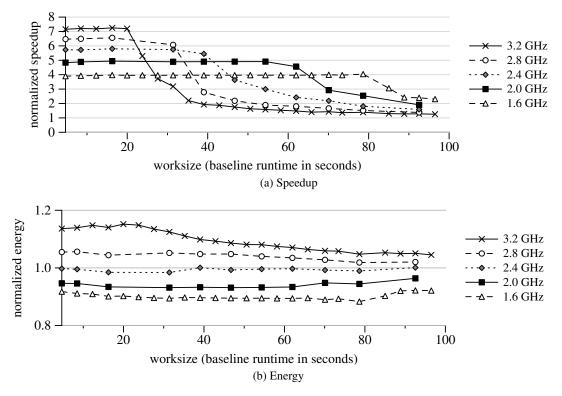

|   |     | 6.2.2    | Responsiveness Benefits of Sprinting with Maximum Intensity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 97  |

|   |     | 6.2.3    | Energy Impact of Sprinting with Maximum Intensity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 98  |

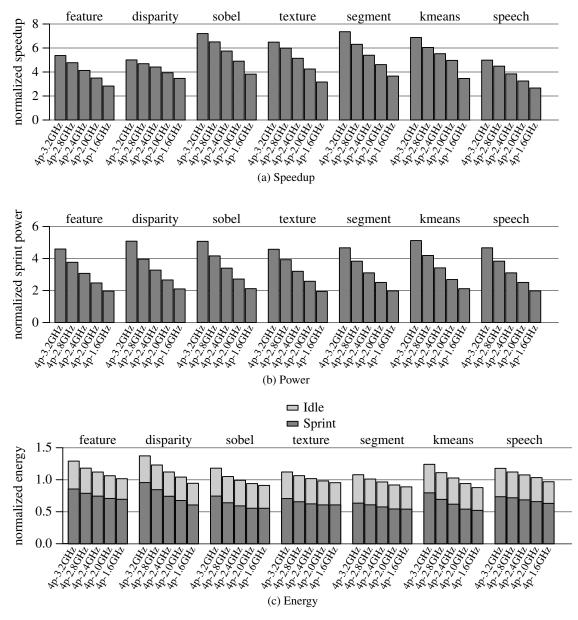

|   |     | 6.2.4    | Unabridged Sprints with Lower Frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 100 |

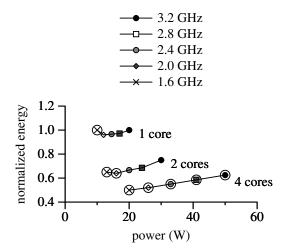

|   | 6.3 | When     | Does Sprinting Save Energy?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 101 |

|   |     | 6.3.1    | Sprinting to Reduce Energy-per-Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 103 |

|   |     | 6.3.2    | Implications of Idle Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 105 |

|   |     | 6.3.3    | Comparison with Observed Energy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 105 |

|   | 6.4 | Trunca   | tted Sprints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 107 |

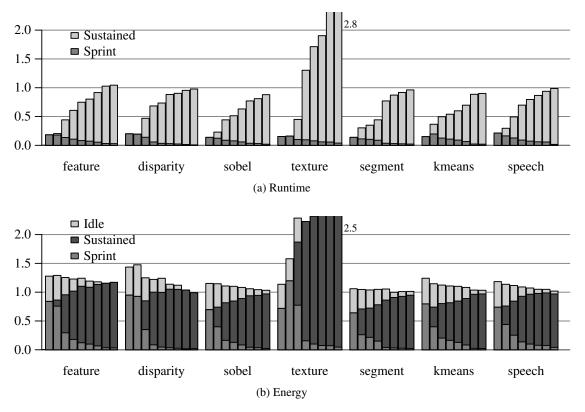

|   |     | 6.4.1    | Performance and Energy Penalties of Sprint Truncation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 107 |

|   |     | 6.4.2    | Inefficiency of Truncated Sprints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 108 |

|   |     | 6.4.3    | Sprint-aware Task-based Parallel Runtime to Mitigate Oversubscription                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 110 |

|   | 6.5 | Sprint   | Pacing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 111 |

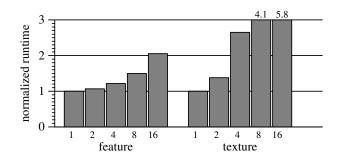

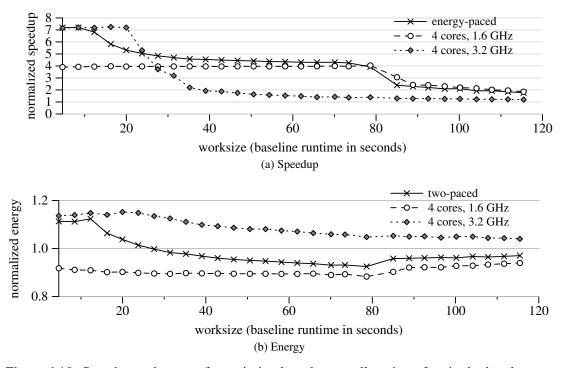

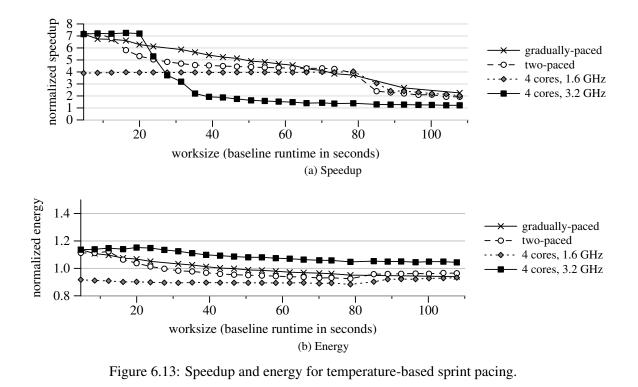

|   |     | 6.5.1    | Benefits of Paced Sprinting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 112 |

|   |     | 6.5.2    | A Simple, Two-intensity Sprint Pacing Policy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 113 |

|   |     | 6.5.3    | A Gradual Sprint Pacing Policy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 114 |

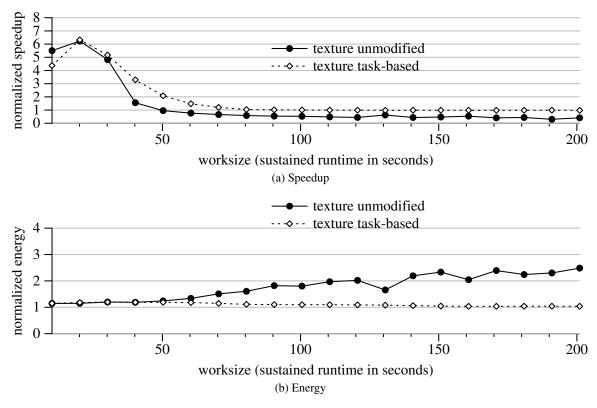

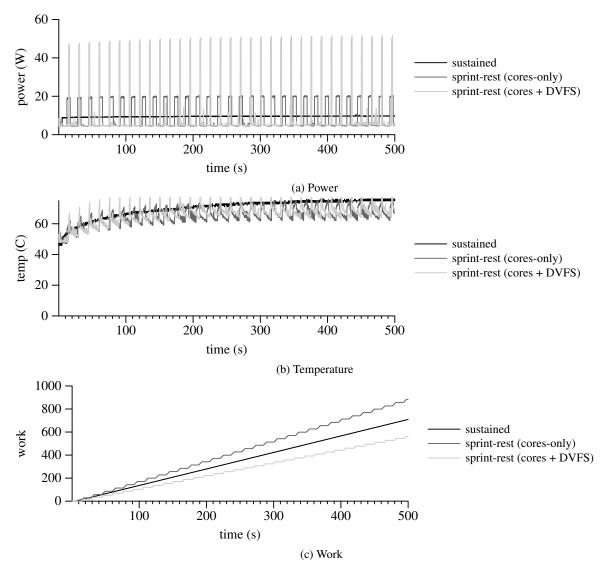

|   | 6.6 | Sprint-  | and-Rest for Sustained Computations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 118 |

|   |     | 6.6.1    | Sprint-and-Rest Energy Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 119 |

|   |     | 6.6.2    | Evaluating Sprint-and-Rest                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 119 |

|   | 6.7 | Chapte   | er Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 121 |

| 7 | Con | clusions | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 123 |

|   | 7.1 |          | tation Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 123 |

|   | 7.2 |          | ions for Future Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 125 |

|   |     | 7.2.1    | How Does Sprinting Impact Reliability?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 125 |

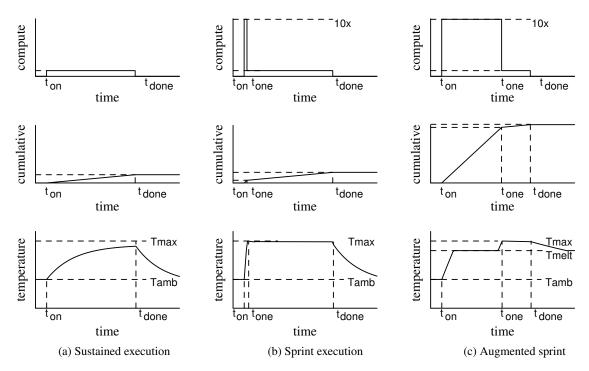

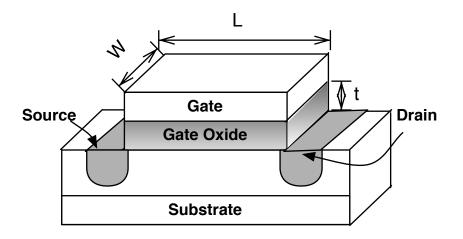

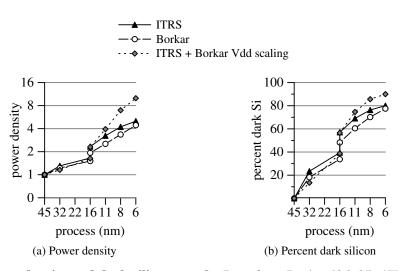

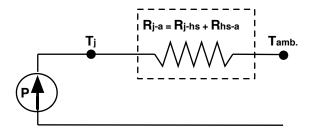

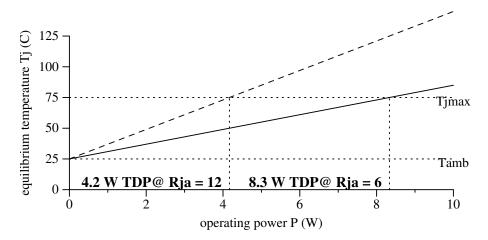

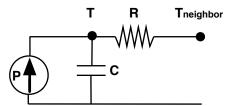

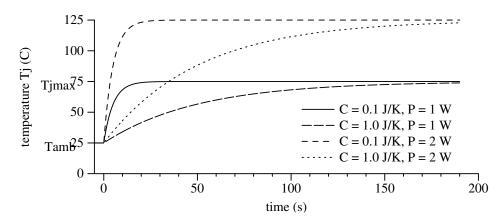

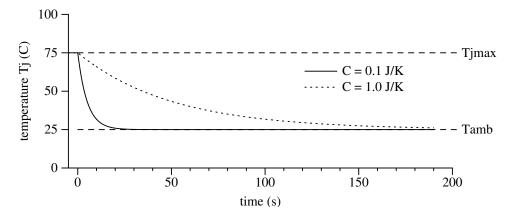

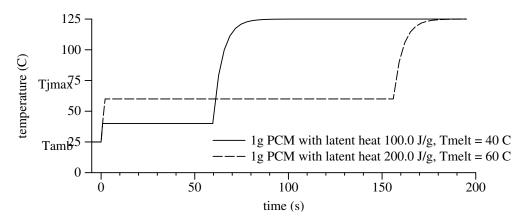

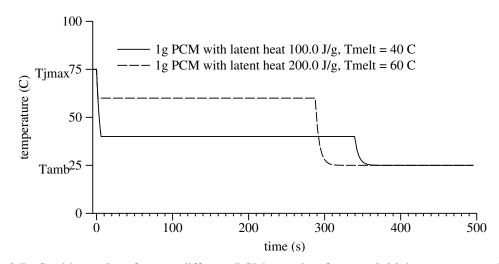

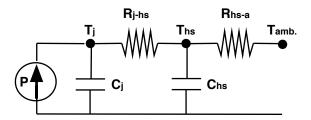

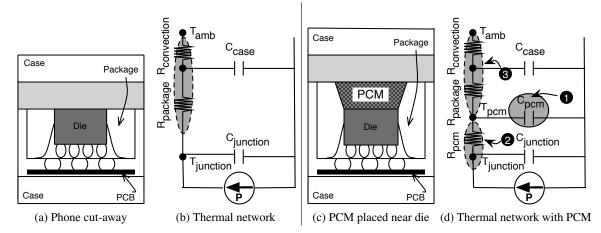

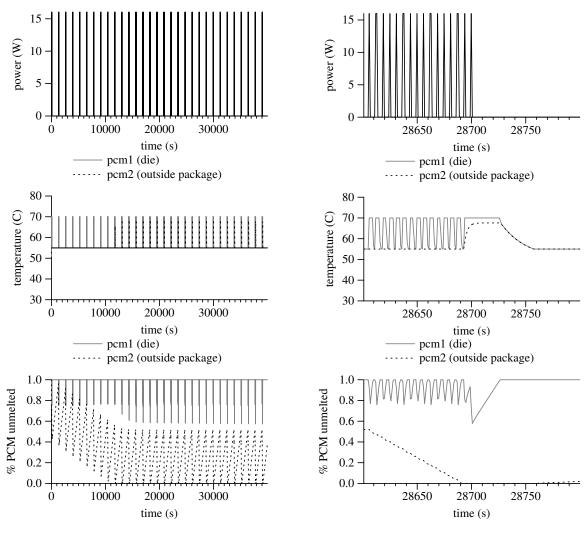

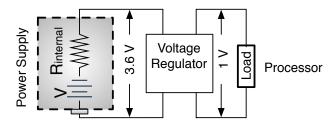

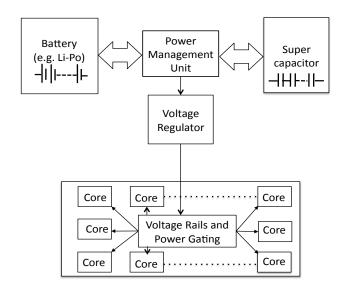

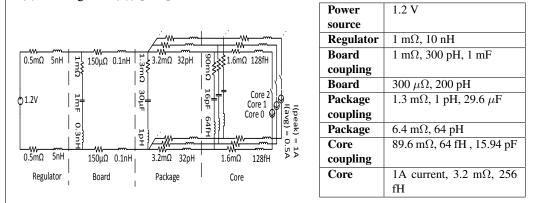

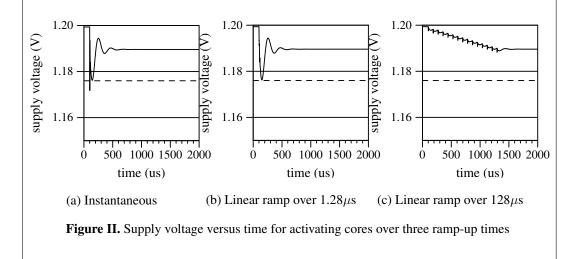

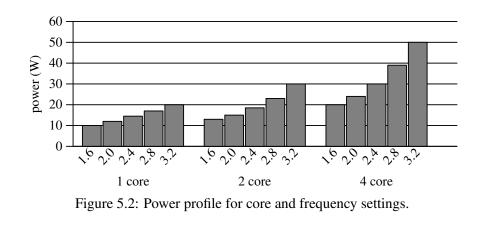

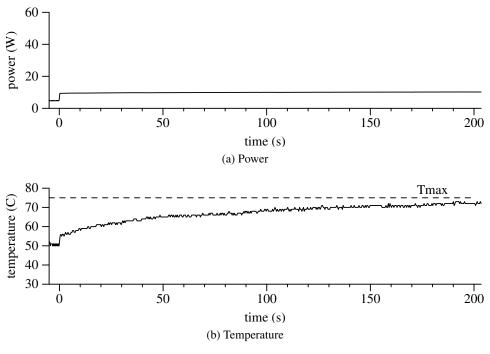

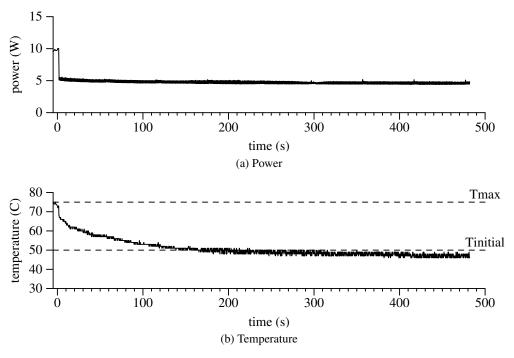

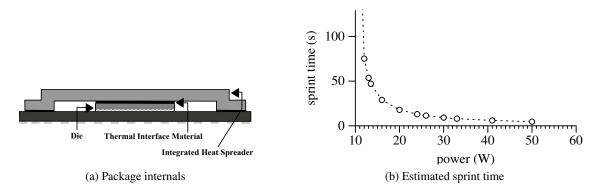

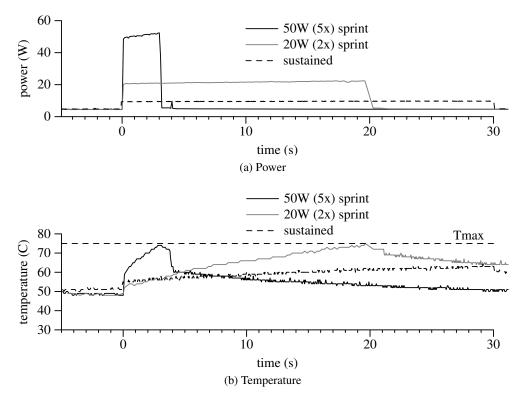

|   |     | 7.2.2    | What is the Metric of Sprinting Performance?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 126 |