# MECHANISMS FOR UNBOUNDED, CONFLICT-ROBUST HARDWARE TRANSACTIONAL MEMORY

Colin Blundell

A DISSERTATION

in

Computer and Information Science

Presented to the Faculties of the University of Pennsylvania

in

Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

2010

Milo M. K. Martin, Associate Professor of Computer and Information Science Supervisor of Dissertation

Jianbo Shi, Associate Professor of Computer and Information Science Graduate Group Chairperson

**Dissertation Committee**

Rajeev Alur, Professor of Computer and Information Science André DeHon, Associate Professor of Electrical and System Engineering Maurice Herlihy, Professor of Computer Science, Brown University Amir Roth, Associate Professor of Computer and Information Science

## Mechanisms for Unbounded, Conflict-Robust Hardware Transactional Memory COPYRIGHT

2010

Colin Blundell

This dissertation is dedicated to my wife, Angelina. Without you, this would not have been possible.

# Acknowledgements

This dissertation would not have been possible without the love and support of my family. My deepest thanks go to my wife, Angelina. The opportunity to meet her has been the greatest reward of my decision to go to graduate school. She is both the source of my success and the reason that this success has meaning. I also thank Jacob for the joy that he has brought to my life and Merlin for his constant good humor, support, and loyalty.

The support of my mother, father, and brother has been instrumental in me reaching this point. They have shared in the joy of my successes and have helped me weather the setbacks. The foundation of my later success was laid in my parents' teaching when I was young. My brother David has been there with me through the ups and downs of our entire lives; he is the best friend a brother could ever hope for.

I am also deeply grateful to my extended family: the Boyarins, the Blundells, and the Stelmachs. The Boyarins have encouraged a spirit of questioning that has served me well as a researcher. My mathematical bent, on the other hand, can be traced to the influence of the Blundells. The Stelmachs have welcomed me as a son. All of these family members have given me constant love and support, and I thank them all. I wish to especially thank my cousin Jonah and my uncle Ian for the extraordinary closeness that we have shared over the course of my life.

I have been fortunate to be advised by Milo Martin. The last five years have been an awesome ride, during which I have benefited greatly from Milo's degree of technical knowledge and ability to share that knowledge. In addition, he has been the best advisor that I can imagine: generous with his time and wisdom, supportive through good times and bad times, extremely fair, and most of all, fun. He is not only an advisor to whom I am deeply indebted but a close friend.

In addition to Milo, I thank the other professors of UPenn's Architecture and Compilers Group (ACG), Amir Roth and E Lewis. Amir and E have greatly contributed to my success and to my

enjoyment of graduate school. Learning about microarchitecture from Amir has been like drinking from a firehose. E has been a second advisor to me. I also thank the members of my committee. Amir, André DeHon, Maurice Herlihy, and Rajeev Alur all provided valuable insight on my dissertation research, for which I am grateful.

I am also grateful for the mentorship of many other professors and senior colleagues. I have greatly benefited from the opportunity to collaborate with Tom Wenisch, who has taught me a great deal about computer architecture as well as the value of hard work. I am grateful to Steve Zdancewic for helping to broaden the scope of my research through the opportunity to collaborate on the Hard-Bound project. I also thank Insup Lee and Sampath Kannan for their support and mentorship during my early years in graduate school, Corina Pasareanu and Dimitra Giannakopoulou for their support during an instructive internship at NASA-Ames, and Joseph Silverman, Kathi Fisler, and Shriram Krishnamurthi for introducing me to research during my undergraduate years. I especially thank Alan Bivens, Calin Cascaval, Maged Michael, Stefanie Chiras, and Trey Cain for helping make my summer at IBM Research so productive and enjoyable that I decided to return after graduating.

I am also greatly indebted to many fellow students. Joe Devietti and Arun Raghavan have been my closest collaborators in graduate school, deeply contributing to my work on unbounded hardware transactional memory and conflict-robust transactional memory respectively. These collaborations have been the source of my greatest enjoyment in graduate school. I also thank the other members of ACG whose support and knowledge I have benefited from: Anne Bracy, Drew Hilton, Marc Corliss, Santosh Nagarakatte, Tingting Sha, and Vlad Petric.

I have been fortunate to have had wonderful friends throughout my time at Penn. Aaron Bohannon and I have had an incredible amount of fun exploring Philadelphia and discussing computer science, indie music, and everything in between over excellent gin and tonics. T.J. Green and his wife Elisabeth have been wonderful friends to both Angelina and myself. Dimitris Vytiniotis and Nate Foster have been close and supportive friends from my first days in graduate school. I have also enjoyed spending time with Jeff Vaughan, Jenn Wortman Vaughan, Matt Jacobs, Micah Sherr, Nick Taylor, Pavol Cerny, and Peng Li. Thank you all.

Throughout this time, I have also relied on and benefited from the support of friends made before graduate school. Ben Finkel has influenced my life more deeply than anyone else outside of my family; I cannot thank him enough. My friendships with Andrew McClain, Nick and Lela Beem, Sarovar Banka, Stephan Marguet, and Thea Brennan-Krohn mean more to me than I can express. Diana Gross has been a close and supportive friend through many ups and downs over the last fifteen years.

I am grateful to the administrative and technical support staff of the CIS Department. Mike Felker is the cornerstone without which the department would surely collapse; I deeply appreciate his competence, friendliness, caring, and hard work over the past seven years. Rita Powell has been a pleasure to interact with. My research would not have been possible without the support of Penn Engineering's Computing and Educational Technology Services (CETS). I particularly thank Dan Widyono, who has been consistently terrific throughout my entire time at Penn. The professionalism of the Moore Business Office has eased many tasks. I especially acknowledge Amy Deitz, Gail Shannon, Mark West, and Towanda Marner.

My graduate work has been financially supported by an IBM Graduate Fellowship, National Science Foundation Grant CCF-0644197, and donations from Intel Corporation.

#### ABSTRACT

## MECHANISMS FOR UNBOUNDED, CONFLICT-ROBUST HARDWARE TRANSACTIONAL MEMORY

#### Colin Blundell

Supervisor: Milo M. K. Martin

Conventional lock implementations serialize access to critical sections guarded by the same lock, presenting programmers with a difficult tradeoff between granularity of synchronization and amount of parallelism realized. Recently, researchers have been investigating an emerging synchronization mechanism called transactional memory as an alternative to such conventional lock-based synchronization. Memory transactions have the semantics of executing in isolation from one another while in reality executing speculatively in parallel, aborting when necessary to maintain the appearance of isolation. This combination of coarse-grained isolation and optimistic parallelism has the potential to ease the tradeoff presented by lock-based programming.

This dissertation studies the hardware implementation of transactional memory, making three main contributions. First, we propose the permissions-only cache, a mechanism that efficiently increases the size of transactions that can be handled in the local cache hierarchy to optimize performance. Second, we propose OneTM, an unbounded hardware transactional memory system that serializes transactions that escape the local cache hierarchy. Finally, we propose RetCon, a novel mechanism for detecting conflicts that reduces conflicts by allowing transactions to commit with different values than those with which they executed as long as dataflow and control-flow constraints are maintained.

# Contents

| 1 | Intr | oductio | n                                                              | 1  |

|---|------|---------|----------------------------------------------------------------|----|

|   | 1.1  | The Pr  | oblem of Synchronization in Shared-Memory Parallel Programs    | 2  |

|   | 1.2  | Transa  | ctional Memory: Promise and Challenges                         | 3  |

|   | 1.3  | The Pe  | ermissions-Only Cache and ONETM                                | 5  |

|   | 1.4  | RetC    | ON                                                             | 6  |

|   | 1.5  | Contri  | butions of this Dissertation                                   | 6  |

|   | 1.6  | Disser  | tation Structure                                               | 7  |

|   | 1.7  | Differe | ences from Previously Published Versions of this Work          | 9  |

| 2 | Ove  | rview o | f Transactional Memory                                         | 10 |

|   | 2.1  | Synch   | ronization in Shared-Memory Parallel Programs                  | 11 |

|   |      | 2.1.1   | Synchronization via Locks                                      | 12 |

|   |      | 2.1.2   | Synchronization via Transactional Memory                       | 14 |

|   | 2.2  | Transa  | ctional Memory Semantics                                       | 17 |

|   |      | 2.2.1   | Basic Semantics                                                | 17 |

|   |      | 2.2.2   | Advanced Semantic Issues                                       | 18 |

|   | 2.3  | Transa  | ctional Memory Implementation Tasks and Terminology            | 19 |

|   |      | 2.3.1   | Conflict Detection                                             | 19 |

|   |      | 2.3.2   | Conflict Resolution                                            | 21 |

|   |      | 2.3.3   | Version Management                                             | 22 |

|   | 2.4  | Three   | High-Level Transactional Memory Algorithms                     | 22 |

|   |      | 2.4.1   | An Eager Conflict Detection/Eager Version Management Algorithm | 23 |

|   |      | 2.4.2   | An Eager Conflict Detection/Lazy Version Management Algorithm  | 24 |

|                                                                                                                                               | 2.4.3                                                                                                                  | A Lazy Conflict Detection/Lazy Version Management Algorithm                                                                                                                                                                                                                                                                                                              | 24                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

|                                                                                                                                               | 2.4.4                                                                                                                  | Implementing These Algorithms                                                                                                                                                                                                                                                                                                                                            | 26                                                                    |

| 2.5                                                                                                                                           | Review                                                                                                                 | of Multiprocessor Memory Systems                                                                                                                                                                                                                                                                                                                                         | 27                                                                    |

|                                                                                                                                               | 2.5.1                                                                                                                  | Caches                                                                                                                                                                                                                                                                                                                                                                   | 27                                                                    |

|                                                                                                                                               | 2.5.2                                                                                                                  | Cache Coherence                                                                                                                                                                                                                                                                                                                                                          | 28                                                                    |

| 2.6                                                                                                                                           | Bounde                                                                                                                 | ed Hardware Transactional Memory                                                                                                                                                                                                                                                                                                                                         | 30                                                                    |

|                                                                                                                                               | 2.6.1                                                                                                                  | Conflict Detection via Cache Coherence                                                                                                                                                                                                                                                                                                                                   | 32                                                                    |

|                                                                                                                                               | 2.6.2                                                                                                                  | Conflict Resolution via Timestamping                                                                                                                                                                                                                                                                                                                                     | 32                                                                    |

|                                                                                                                                               | 2.6.3                                                                                                                  | Options for Eager Version Management                                                                                                                                                                                                                                                                                                                                     | 32                                                                    |

|                                                                                                                                               | 2.6.4                                                                                                                  | Bounded HTM Algorithms                                                                                                                                                                                                                                                                                                                                                   | 34                                                                    |

|                                                                                                                                               | 2.6.5                                                                                                                  | Implementation Details                                                                                                                                                                                                                                                                                                                                                   | 37                                                                    |

|                                                                                                                                               | 2.6.6                                                                                                                  | Restrictions on Transaction Size and Duration                                                                                                                                                                                                                                                                                                                            | 38                                                                    |

| 2.7                                                                                                                                           | Seman                                                                                                                  | tic and Performance Challenges of Bounded HTM                                                                                                                                                                                                                                                                                                                            | 38                                                                    |

| 2.8                                                                                                                                           | Summa                                                                                                                  | ury                                                                                                                                                                                                                                                                                                                                                                      | 39                                                                    |

|                                                                                                                                               |                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                          | 44                                                                    |

| Cha                                                                                                                                           | racteriz                                                                                                               | ation of Transactional Behavior                                                                                                                                                                                                                                                                                                                                          | 41                                                                    |

| <b>Cha</b><br>3.1                                                                                                                             |                                                                                                                        | ation of Transactional Behavior                                                                                                                                                                                                                                                                                                                                          | <b>41</b><br>42                                                       |

|                                                                                                                                               |                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                          |                                                                       |

|                                                                                                                                               | Worklo                                                                                                                 | ads                                                                                                                                                                                                                                                                                                                                                                      | 42                                                                    |

|                                                                                                                                               | Worklo<br>3.1.1<br>3.1.2                                                                                               | ads                                                                                                                                                                                                                                                                                                                                                                      | 42<br>42                                                              |

| 3.1                                                                                                                                           | Worklo<br>3.1.1<br>3.1.2<br>Experin                                                                                    | pads                                                                                                                                                                                                                                                                                                                                                                     | 42<br>42<br>44                                                        |

| <ul><li>3.1</li><li>3.2</li></ul>                                                                                                             | Worklo<br>3.1.1<br>3.1.2<br>Experin<br>Are Co                                                                          | bads       STAMP       STAMP       STAMP         Python       State       State       State         mental Infrastructure and Methodology       State       State       State                                                                                                                                                                                            | 42<br>42<br>44<br>45                                                  |

| <ul><li>3.1</li><li>3.2</li><li>3.3</li></ul>                                                                                                 | Worklo<br>3.1.1<br>3.1.2<br>Experin<br>Are Co<br>Analys                                                                | bads    STAMP      STAMP    STAMP      Python    Python      Infrastructure and Methodology    Infrastructure and Methodology      Inflicts a Performance Problem?    Infrastructure                                                                                                                                                                                     | 42<br>42<br>44<br>45<br>47<br>50                                      |

| <ul><li>3.1</li><li>3.2</li><li>3.3</li><li>3.4</li></ul>                                                                                     | Worklo<br>3.1.1<br>3.1.2<br>Experin<br>Are Co<br>Analys<br>How La                                                      | bads STAMP   STAMP STAMP   Python Python   Infirastructure and Methodology Infirastructure and Methodology   Inflicts a Performance Problem? Infirastructure and Infirastructure                                                                                                                                                                                         | 42<br>42<br>44<br>45<br>47<br>50                                      |

| <ul> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>3.6</li> </ul>                                                      | Worklo<br>3.1.1<br>3.1.2<br>Experin<br>Are Co<br>Analys<br>How La<br>Summa                                             | bads       STAMP       STAMP         Python       Python         mental Infrastructure and Methodology       Inflicts a Performance Problem?         is of Conflicts       Inflicts a Performance Problem?         arge Do Transactions Become?       Inflicts                                                                                                           | 42<br>42<br>44<br>45<br>47<br>50<br>53                                |

| <ul> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>3.6</li> </ul>                                                      | Worklo<br>3.1.1<br>3.1.2<br>Experin<br>Are Co<br>Analys<br>How La<br>Summa                                             | bads       STAMP                                                                                                                                                                                                                                                                                                                                                         | 42<br>42<br>44<br>45<br>47<br>50<br>53<br>58                          |

| <ul> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>3.6</li> <li>Prior</li> </ul>                                       | Worklo<br>3.1.1<br>3.1.2<br>Experin<br>Are Co<br>Analys<br>How La<br>Summa                                             | bads STAMP   STAMP STAMP   Python Python   mental Infrastructure and Methodology Image of the structure and Methodology   inflicts a Performance Problem? Image of the structure and methodology   is of Conflicts Image of the structure and methodology   arge Do Transactions Become? Image of the structure and methodology   arge to Handling Overflows in Hardware | 42<br>42<br>44<br>45<br>47<br>50<br>53<br>58<br><b>61</b>             |

| <ul> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>3.6</li> <li>Prio</li> <li>4.1</li> </ul>                           | Worklo<br>3.1.1<br>3.1.2<br>Experin<br>Are Co<br>Analys<br>How La<br>Summa<br>or Appro<br>UTM, T<br>Bulk an            | bads STAMP   Python Python   mental Infrastructure and Methodology Python   inflicts a Performance Problem? Python   is of Conflicts Python   arge Do Transactions Become? Python   ary Python                                                                                                                                                                           | 42<br>42<br>44<br>45<br>47<br>50<br>53<br>58<br><b>61</b><br>62       |

| <ul> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>3.6</li> <li>Prio</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> </ul> | Worklo<br>3.1.1<br>3.1.2<br>Experin<br>Are Co<br>Analys<br>How La<br>Summa<br>or Appro<br>UTM, T<br>Bulk an<br>Discuss | wads STAMP   Python Python   mental Infrastructure and Methodology Python   inflicts a Performance Problem? Python   is of Conflicts Python   is of Conflicts Python   arge Do Transactions Become? Python   infly Python   exaches to Handling Overflows in Hardware   VTM, and PTM   NTM, and PTM                                                                      | 42<br>42<br>44<br>45<br>47<br>50<br>53<br>58<br><b>61</b><br>62<br>65 |

|                                                                                                                                               | 2.6                                                                                                                    | <ul> <li>2.5 Review</li> <li>2.5.1</li> <li>2.5.2</li> <li>2.6 Bounde</li> <li>2.6.1</li> <li>2.6.2</li> <li>2.6.3</li> <li>2.6.4</li> <li>2.6.5</li> <li>2.6.6</li> <li>2.7 Semant</li> </ul>                                                                                                                                                                           | <ul> <li>2.5 Review of Multiprocessor Memory Systems</li></ul>        |

|   | 5.2 | Efficie | nt Encoding                                                              | 76  |

|---|-----|---------|--------------------------------------------------------------------------|-----|

|   | 5.3 | Emplo   | ying the L2 Cache to Store Permissions-Only Information                  | 78  |

|   | 5.4 | Related | d Work                                                                   | 78  |

|   | 5.5 | Discus  | sion                                                                     | 79  |

| 6 | Oni | ETM: H  | andling Overflows via Selective Serialization                            | 80  |

|   | 6.1 | ONET    | M-Serialized                                                             | 82  |

|   |     | 6.1.1   | Structures                                                               | 82  |

|   |     | 6.1.2   | Operation                                                                | 84  |

|   |     | 6.1.3   | Runtime Involvement                                                      | 85  |

|   |     | 6.1.4   | ONETM-Serialized Summary                                                 | 85  |

|   | 6.2 | ONET    | M-Concurrent                                                             | 86  |

|   |     | 6.2.1   | Metadata Operation                                                       | 88  |

|   |     | 6.2.2   | Lazy Metadata Clearing                                                   | 91  |

|   |     | 6.2.3   | Lazily Coherent Metadata                                                 | 92  |

|   |     | 6.2.4   | Example Execution                                                        | 93  |

|   |     | 6.2.5   | Operating System Involvement                                             | 93  |

|   |     | 6.2.6   | Comparison to Prior Work                                                 | 94  |

|   | 6.3 | Seman   | tic Considerations in ONETM                                              | 95  |

|   | 6.4 | Subsec  | juent Work                                                               | 97  |

|   | 6.5 | Summ    | ary                                                                      | 98  |

| 7 | Exp | eriment | al Evaluation of ONETM and the Permissions-Only Cache                    | 100 |

|   | 7.1 | Experi  | mental Methodology                                                       | 101 |

|   | 7.2 | Evalua  | tion of ONETM                                                            | 101 |

|   |     | 7.2.1   | What is the Impact of Serializing the System on Overflow?                | 102 |

|   |     | 7.2.2   | Does Serialization of Only Overflowed Transactions Increase Performance? | 102 |

|   |     | 7.2.3   | Summary                                                                  | 104 |

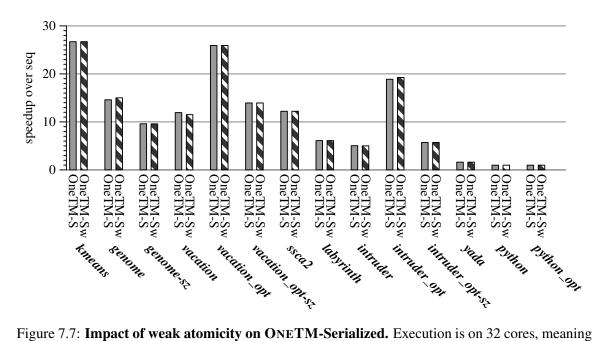

|   | 7.3 | Impact  | t of Weak Atomicity on ONETM                                             | 106 |

|   |     | 7.3.1   | Does Weak Atomicity Help ONETM-Serialized Performance?                   | 108 |

|   |     | 7.3.2   | Does Weak Atomicity Help ONETM-Concurrent Performance?                   | 109 |

|   |     | 7.3.3   | Summary                                                              | 109 |

|---|-----|---------|----------------------------------------------------------------------|-----|

|   | 7.4 | Impact  | of Lazy Clearing on ONETM-Concurrent Performance                     | 109 |

|   |     | 7.4.1   | Summary                                                              | 112 |

|   | 7.5 | Impact  | of the Permissions-Only Cache on ONETM Performance                   | 112 |

|   |     | 7.5.1   | Impact of the Read-Only Permissions-Only Cache on ONETM-Serialized . | 112 |

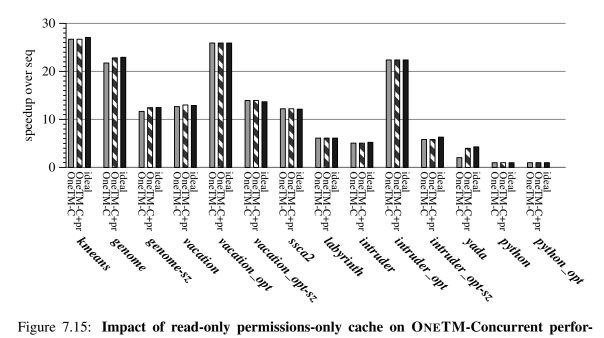

|   |     | 7.5.2   | Impact of the Read-Only Permissions-Only Cache on ONETM-Concurrent   | 114 |

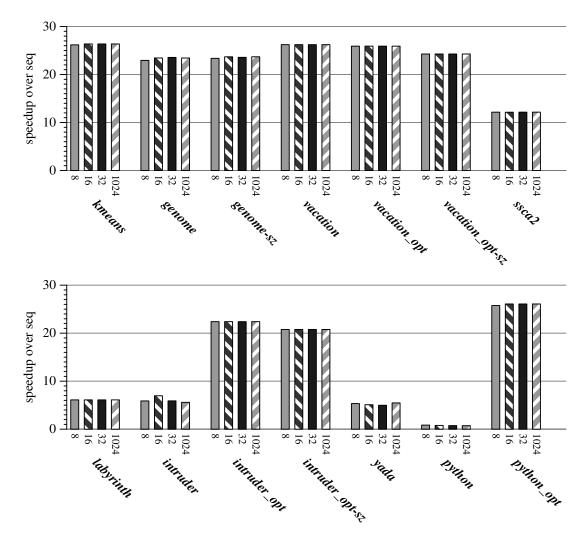

|   |     | 7.5.3   | Sensitivity to Sector Cache Organization                             | 114 |

|   |     | 7.5.4   | Sensitivity to Permissions-Only Cache Size                           | 114 |

|   |     | 7.5.5   | The Remaining Performance Gap between ONETM and the Idealized HTM    | 122 |

|   |     | 7.5.6   | Permissions-Only Cache Summary                                       | 124 |

|   | 7.6 | Discus  | sion of Power Implications of Our Proposals                          | 124 |

|   | 7.7 | Summa   | ary                                                                  | 126 |

| 8 | Ret | CON: F  | Eliminating Auxiliary Data Conflicts                                 | 128 |

|   | 8.1 | RetCo   | ON Architecture and High-Level Operation                             | 130 |

|   |     | 8.1.1   | RETCON Operation                                                     | 131 |

|   |     | 8.1.2   | Conflict Idioms that RETCON Can Repair                               | 136 |

|   |     | 8.1.3   | Conflict Idioms that RETCON Cannot Repair                            | 136 |

|   | 8.2 | Operat  | ional Details                                                        | 140 |

|   | 8.3 | RetCo   | ON Implementation Optimizations                                      | 142 |

|   | 8.4 | Other I | Benefits of RETCON                                                   | 143 |

|   | 8.5 | Related | d Work                                                               | 144 |

|   | 8.6 | Summa   | ary                                                                  | 146 |

| 9 | Exp | eriment | al Evaluation of RETCON                                              | 147 |

|   | 9.1 | Metho   | dology                                                               | 148 |

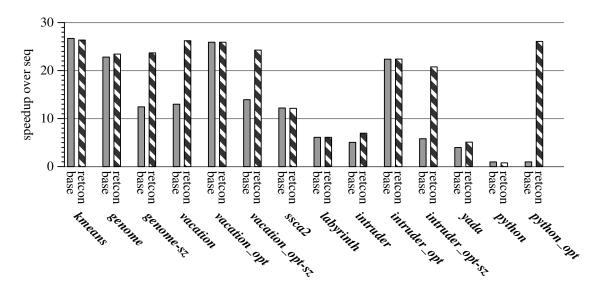

|   | 9.2 | Perform | mance Impact of RETCON                                               | 149 |

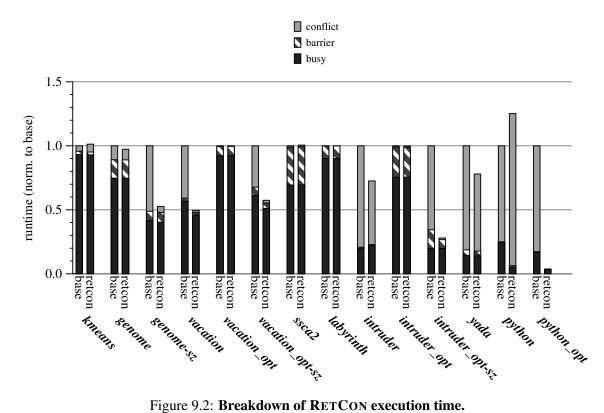

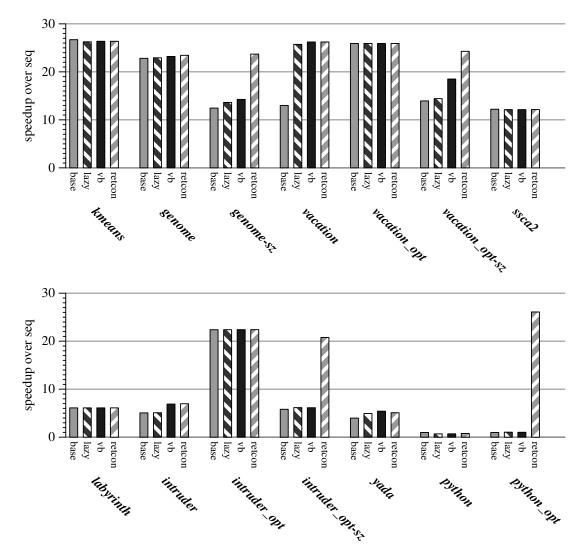

|   | 9.3 | What C  | Contributes to RETCON Performance?                                   | 149 |

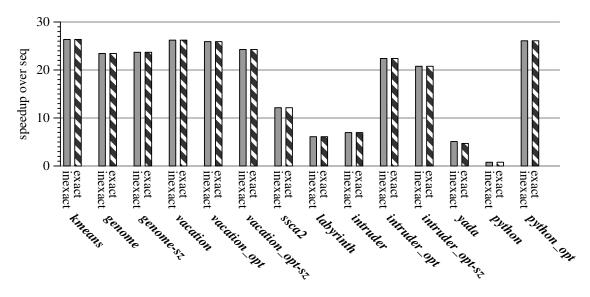

|   | 9.4 | Impact  | of Inexact Constraint Representation on RETCON                       | 152 |

|   | 9.5 | Sensiti | vity of RETCON to Parallelism of Commit-Time Reacquires              | 153 |

|   | 9.6 | Sensiti | vity of RETCON to Structure Size                                     | 153 |

|     | 9.7    | Sensitivity of RETCON to Predictor Configuration | 156 |

|-----|--------|--------------------------------------------------|-----|

|     | 9.8    | Discussion of the Power Implications of RETCON   | 160 |

|     | 9.9    | Summary and Remaining Challenges                 | 160 |

| 10  | Con    | clusions                                         | 163 |

|     | 10.1   | Dissertation Summary                             | 163 |

|     | 10.2   | Future Work                                      | 164 |

|     | 10.3   | Reflections on Transactional Memory              | 165 |

| Bil | bliogr | aphy                                             | 167 |

# **List of Figures**

| A program requiring synchronization for correct behavior                                 | 11                          |

|------------------------------------------------------------------------------------------|-----------------------------|

| Synchronization via locking                                                              | 12                          |

| Two ways to synchronize a hashtable with locks                                           | 13                          |

| Moving an element from one hashtable to another using locking                            | 15                          |

| Synchronizing a hashtable using transactions                                             | 15                          |

| Moving an element from one hashtable to another using transactions                       | 16                          |

| Algorithm for an eager/eager transactional memory system                                 | 23                          |

| Algorithm for an eager/lazy transactional memory system                                  | 25                          |

| Algorithm for a lazy/lazy transactional memory system                                    | 26                          |

| Coherence algorithm                                                                      | 29                          |

| Bounded HTM algorithm using cleaning for version management                              | 35                          |

| Bounded HTM algorithm using a log for version management                                 | 36                          |

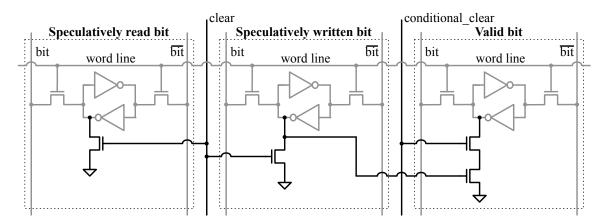

| Flash-clear and conditional flash-clear circuitry                                        | 37                          |

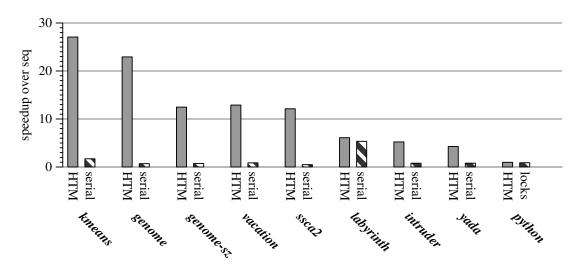

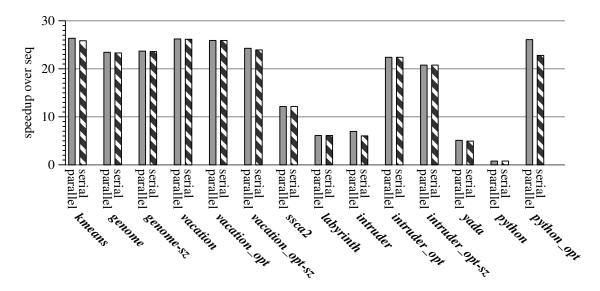

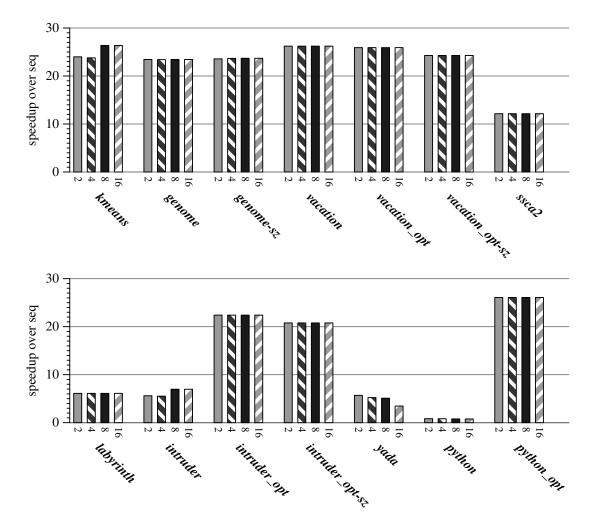

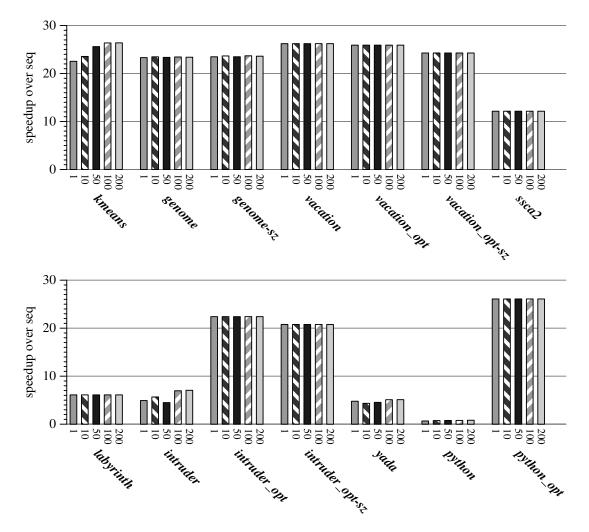

| Scalability of workloads under idealized HTM                                             | 47                          |

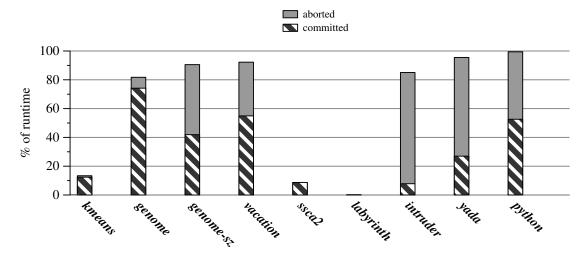

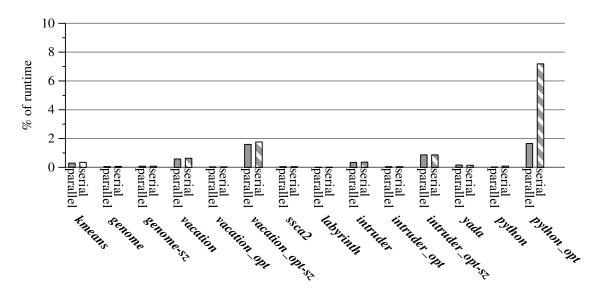

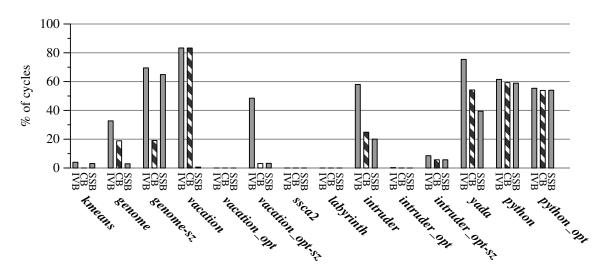

| Percentage of total execution time that is spent in committed and aborted transactions . | 48                          |

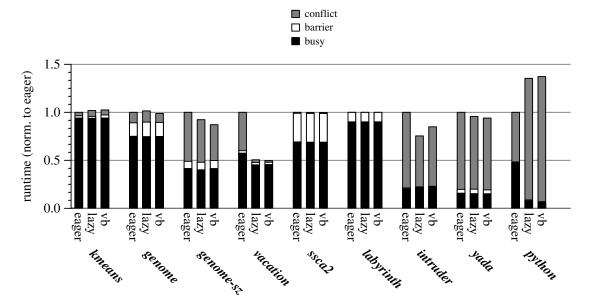

| Runtime breakdown of workloads under idealized HTM                                       | 49                          |

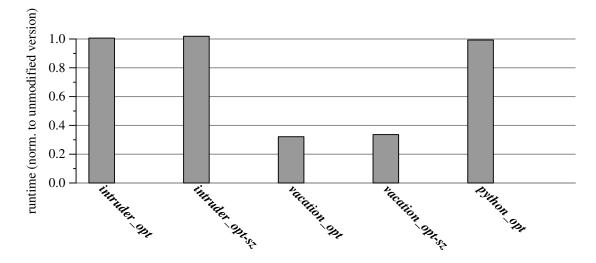

| Sequential runtimes of optimized workloads relative to the unoptimized versions          | 51                          |

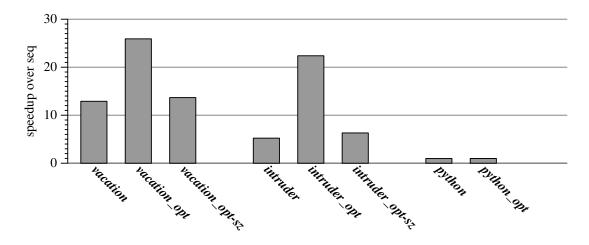

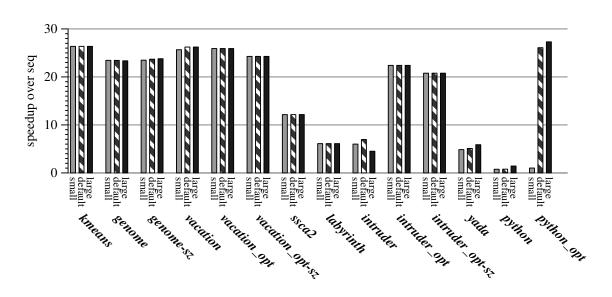

| Scalability of unoptimized and optimized versions of workloads under idealized HTM       | 52                          |

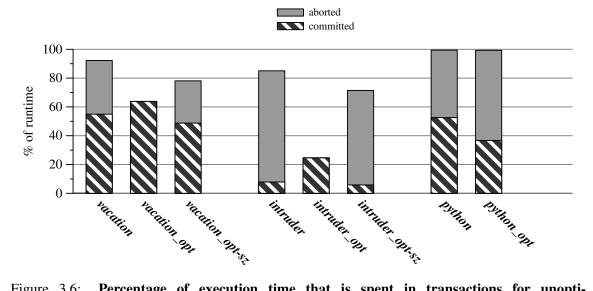

| Percentage of time spent in transactions for unoptimized/optimized workloads             | 52                          |

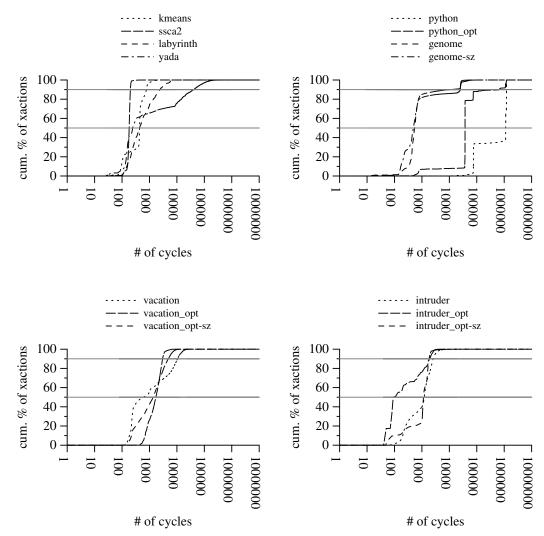

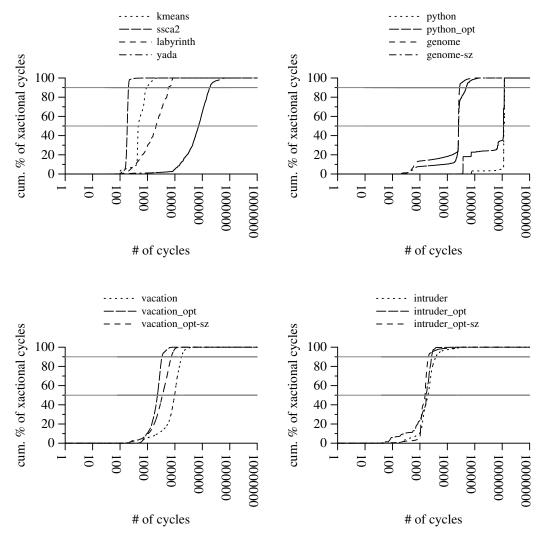

| Breakdown of transaction lengths by percent of transactions                              | 54                          |

| Breakdown of transaction lengths by percent of transactional cycles                      | 55                          |

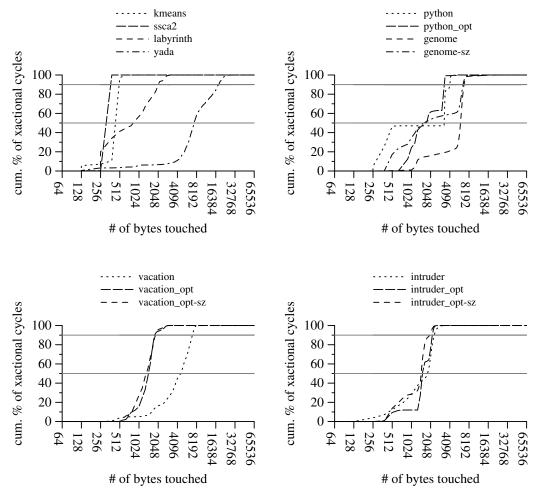

| Breakdown of transaction sizes by percent of transactional cycles                        | 56                          |

|                                                                                          | Synchronization via locking |

| 3.10 | Breakdown of transaction read set sizes by percent of transactional cycles     | 57  |

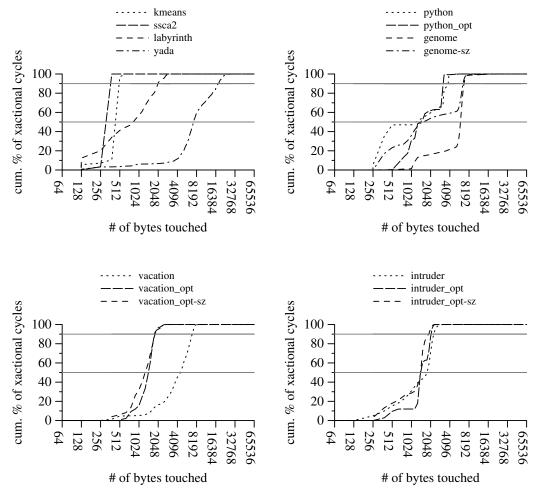

|------|--------------------------------------------------------------------------------|-----|

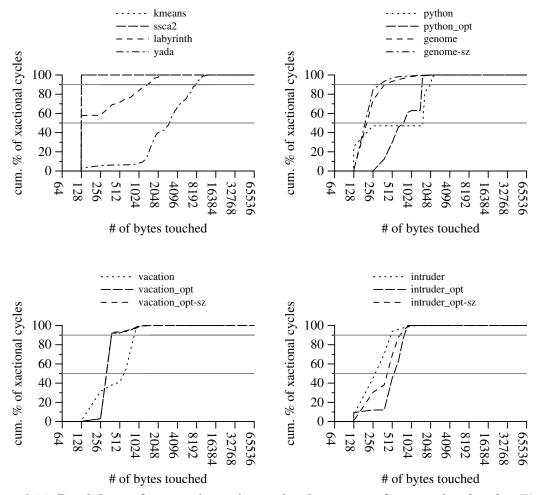

| 3.11 | Breakdown of transaction write set sizes by percent of transactional cycles    | 58  |

| 3.12 | Breakdown of transaction sizes by percent of total cycles                      | 59  |

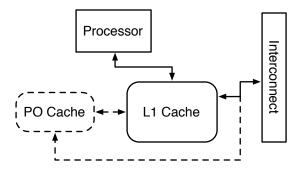

| 5.1  | Incorporation of the permissions-only cache into the system                    | 72  |

| 5.2  | Adding a read-only permissions-only cache to bounded HTM                       | 74  |

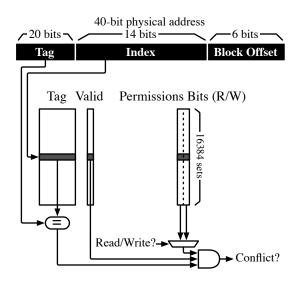

| 5.3  | Adding a read-write permissions-only cache to bounded HTM                      | 75  |

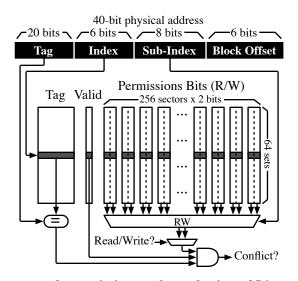

| 5.4  | A naively-organized 4KB direct-mapped permissions-only cache                   | 76  |

| 5.5  | 4KB direct-mapped permissions-only cache in a 256-sector organization          | 77  |

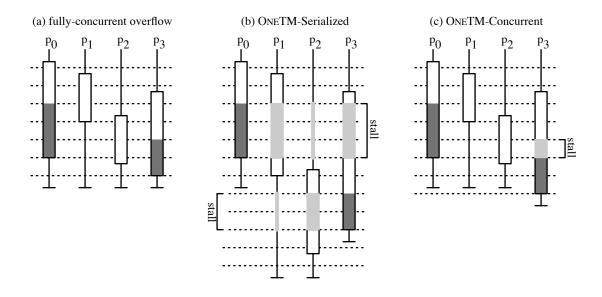

| 6.1  | An example execution on three systems for handling overflowed transactions     | 81  |

| 6.2  | Description of transaction status words                                        | 82  |

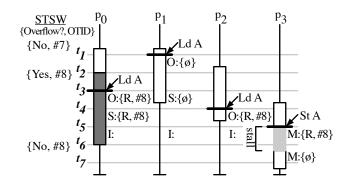

| 6.3  | ONETM-Serialized algorithm                                                     | 83  |

| 6.4  | ONETM-Concurrent algorithm with active clearing                                | 87  |

| 6.5  | Addition of lazy clearing to ONETM-Concurrent algorithm                        | 90  |

| 6.6  | Lazy coherence and clearing of metadata in ONETM-Concurrent                    | 94  |

| 6.7  | Overflow handling algorithm of Hofmann et al. [50]                             | 97  |

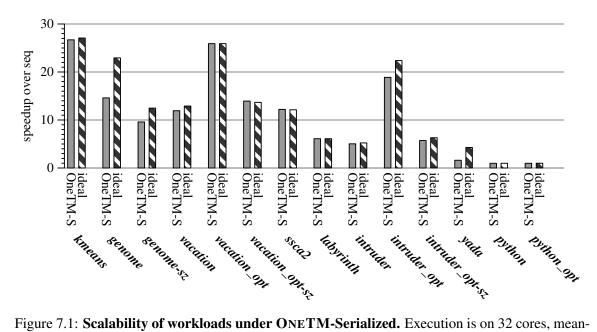

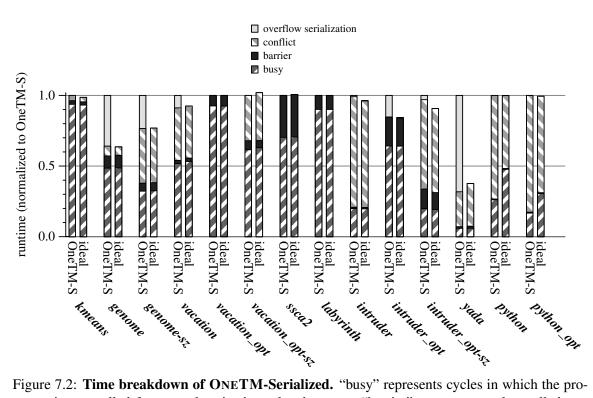

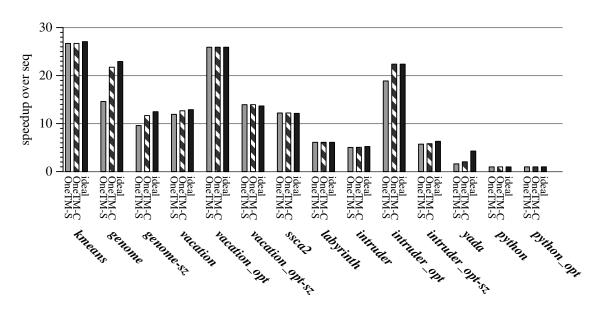

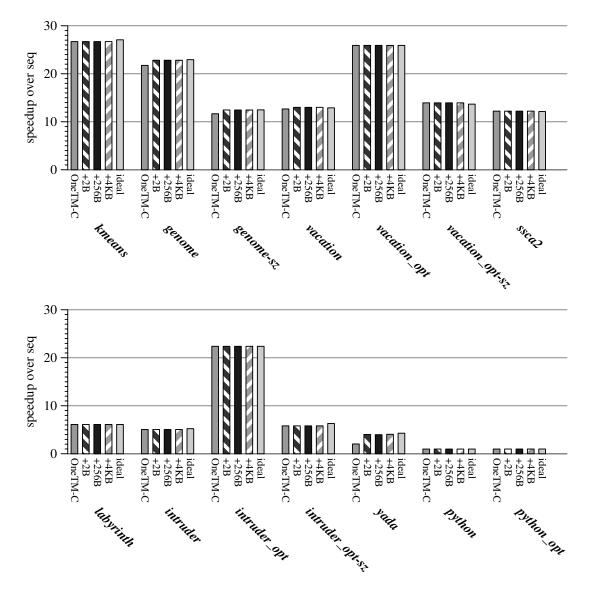

| 7.1  | Scalability of workloads under ONETM-Serialized                                | 103 |

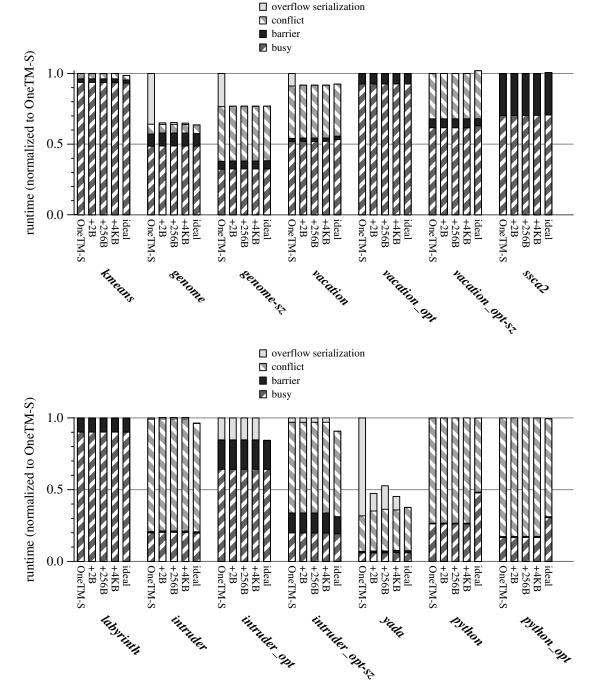

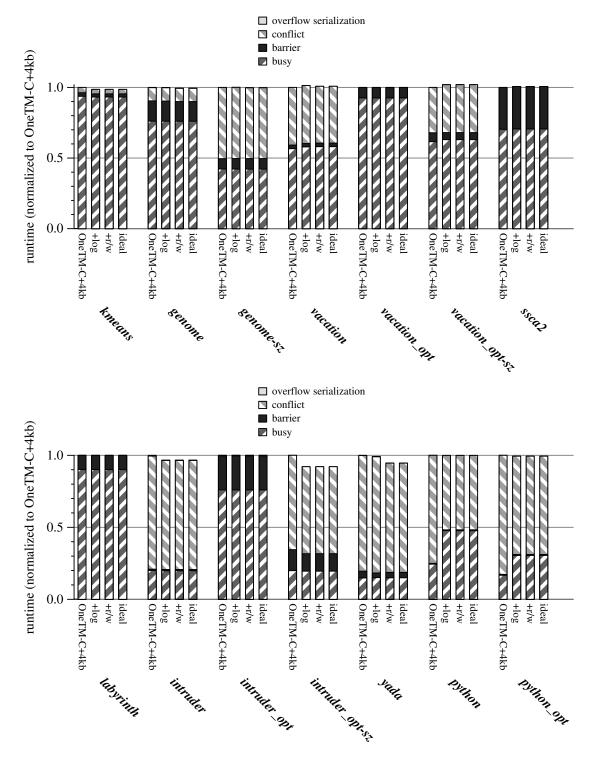

| 7.2  | Time breakdown of ONETM-Serialized                                             | 103 |

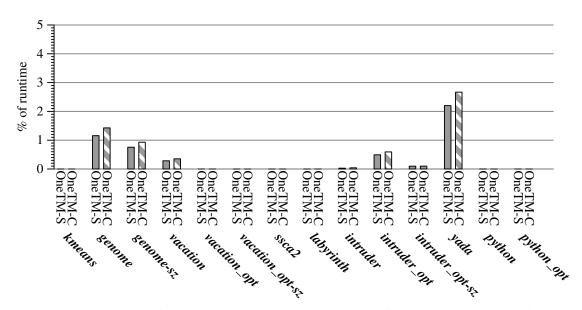

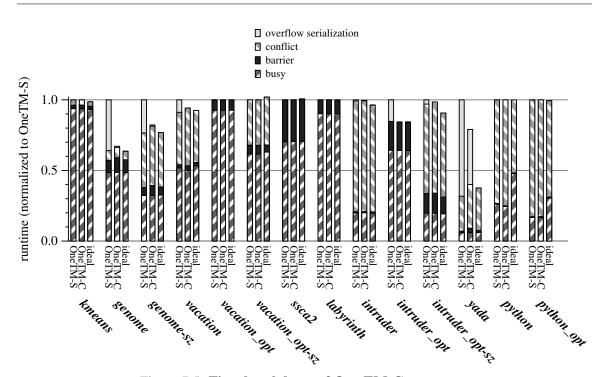

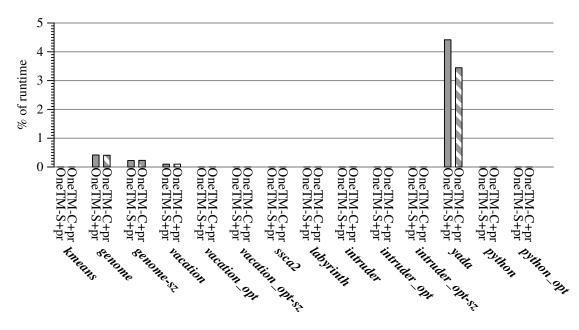

| 7.3  | Overflowed transaction time in ONETM                                           | 104 |

| 7.4  | Scalability of workloads under ONETM-Concurrent                                | 105 |

| 7.5  | Time breakdown of ONETM-Concurrent                                             | 105 |

| 7.6  | Stall time due to serialization of overflowed transactions in ONETM-Concurrent | 106 |

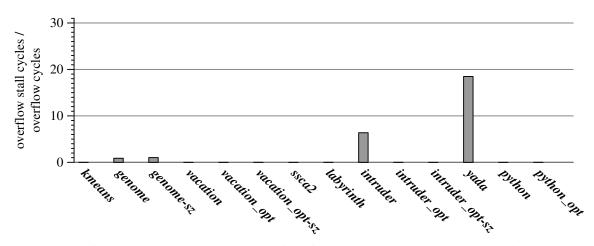

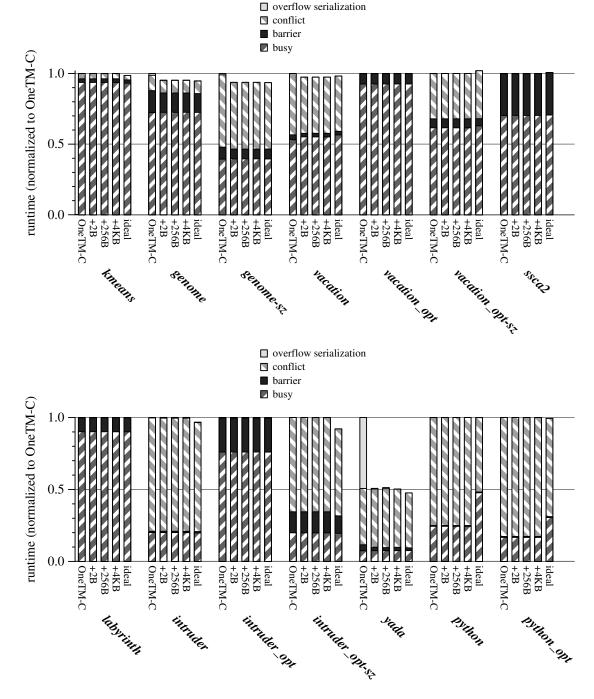

| 7.7  | Impact of weak atomicity on ONETM-Serialized                                   | 107 |

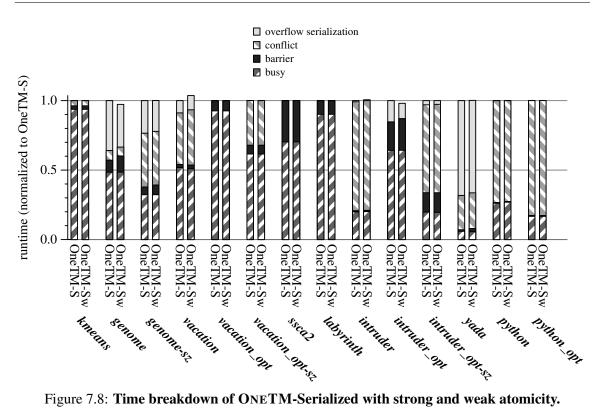

| 7.8  | Time breakdown of ONETM-Serialized with strong and weak atomicity              | 107 |

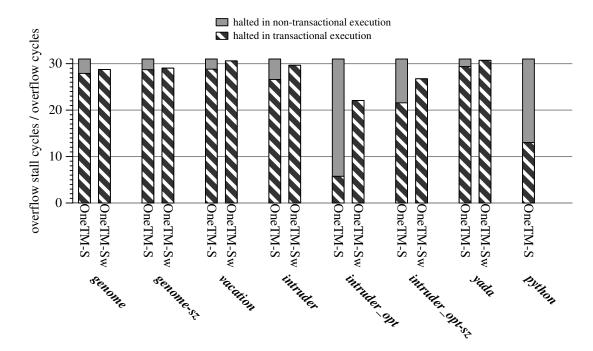

| 7.9  | Stall time due to serialization of overflowed transactions                     | 108 |

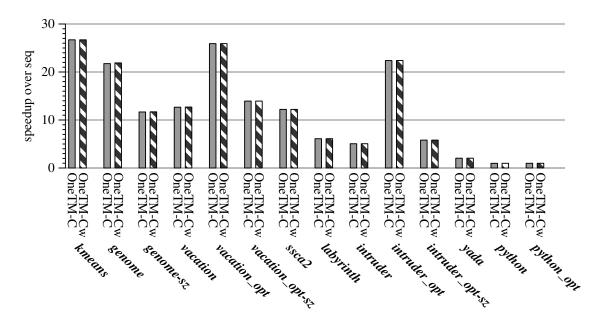

| 7.10 | Impact of weak atomicity on ONETM-Concurrent                                   | 110 |

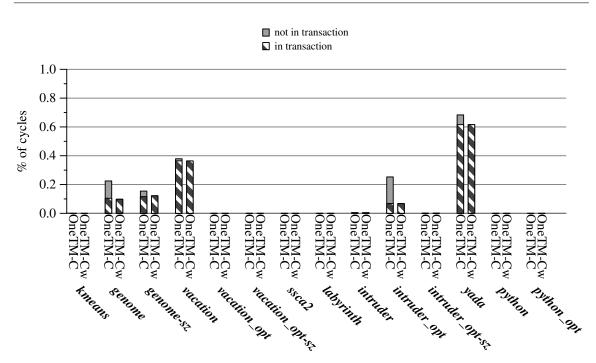

| 7.11 | Breakdown of stall time due to overflowed conflicts in ONETM-Concurrent        | 110 |

| 7.12 | Impact of OTID length on ONETM-Concurrent                                      | 111 |

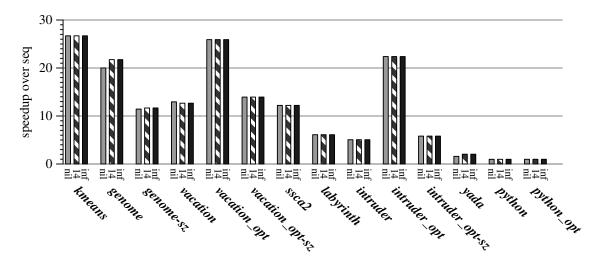

| 7.13 | Impact of read-only permissions-only cache on ONETM-Serialized performance     | 113 |

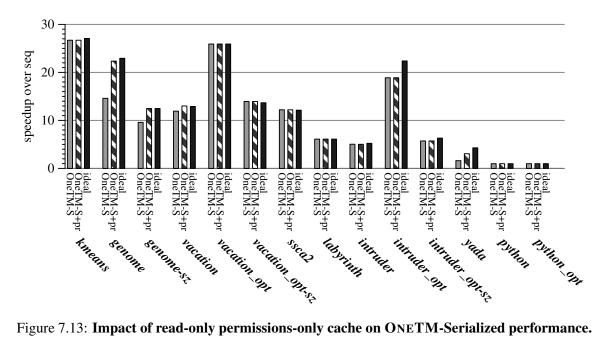

| 7.14 | Impact of read-only permissions-only cache on ONETM-Serialized execution time  | 113 |

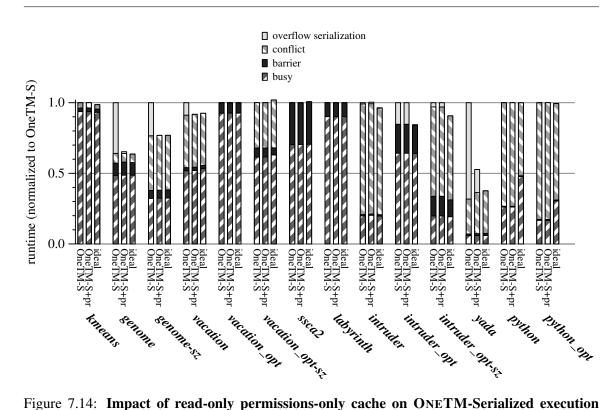

| 7.15 | Impact of read-only permissions-only cache on ONETM-Concurrent performance 1         | 15 |

|------|--------------------------------------------------------------------------------------|----|

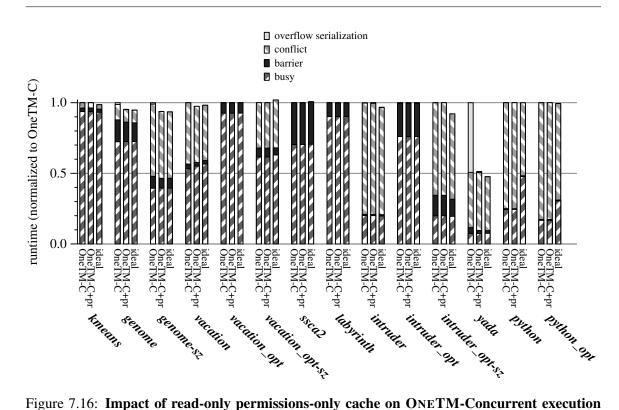

| 7.16 | Impact of read-only permissions-only cache on ONETM-Concurrent execution time 1      | 15 |

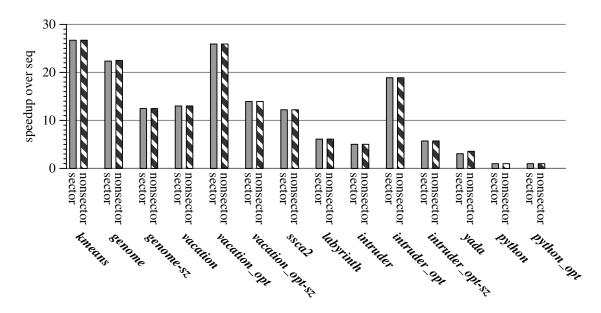

| 7.17 | Impact of permissions-only cache sector cache organization on ONETM-Serialized 1     | 16 |

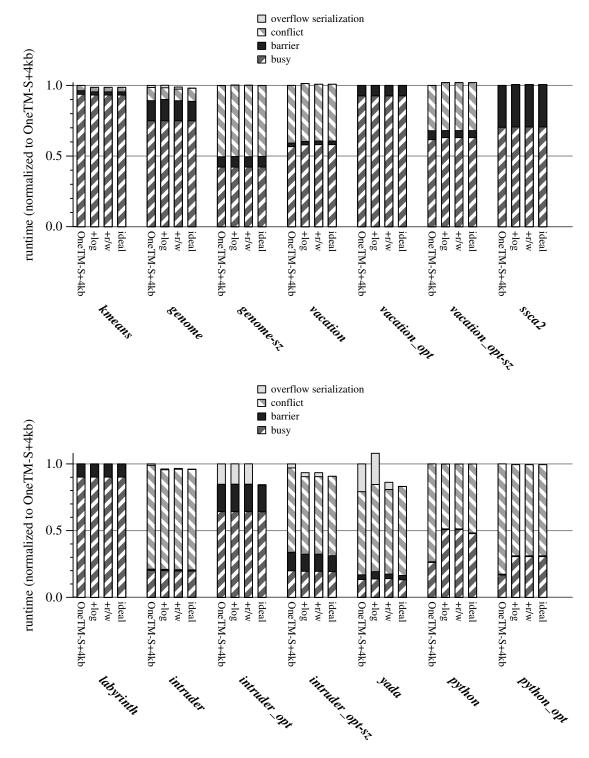

| 7.18 | Impact of permissions-only cache sector cache organization on ONETM-Concurrent . 1   | 16 |

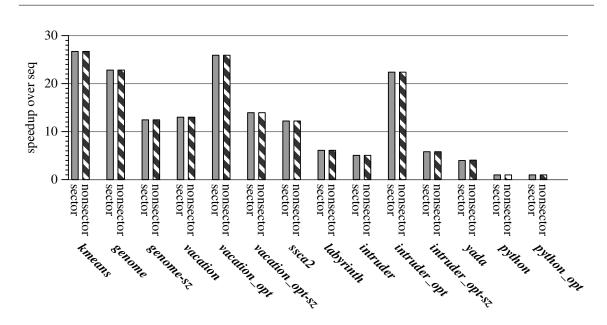

| 7.19 | Impact of permissions-only caches of various sizes on ONETM-Serialized performance 1 | 17 |

| 7.20 | Impact of permissions-only caches of varying sizes on ONETM-Serialized runtime 1     | 18 |

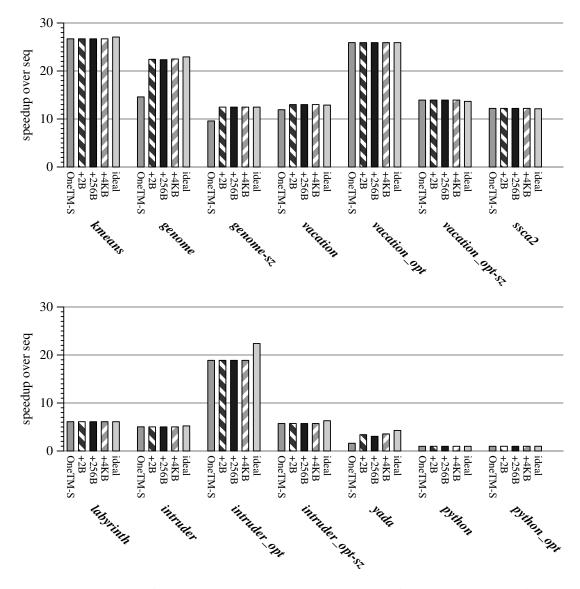

| 7.21 | Impact of permissions-only caches of varying sizes on ONETM-Concurrent performance 1 | 20 |

| 7.22 | Impact of permissions-only caches of varying sizes on ONETM-Concurrent runtime . 1   | 21 |

| 7.23 | Remaining performance gap between ONETM-Serialized and the idealized HTM 1           | 23 |

| 7.24 | Remaining performance gap between ONETM-Concurrent and the idealized HTM $\ldots$ 1  | 25 |

| 7.25 | Percent of time that the permissions-only cache is non-empty                         | 26 |

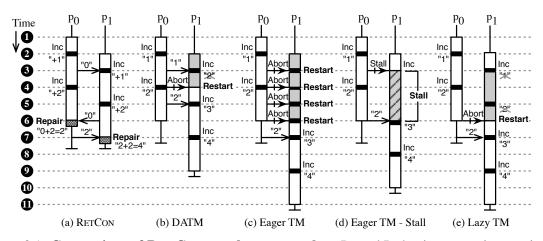

| 8.1  | Comparison of RETCON to other approaches                                             | 29 |

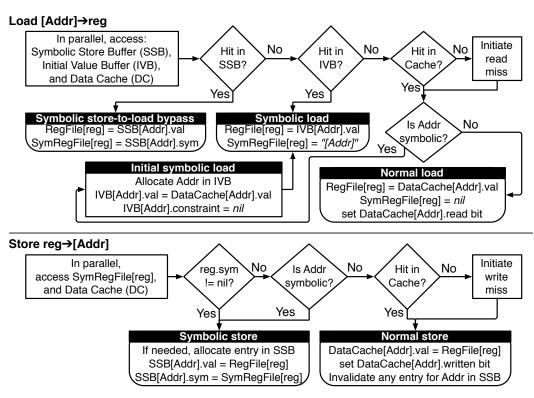

| 8.2  | RETCON structures   1                                                                |    |

| 8.3  | RETCON memory operation flowchart                                                    |    |

| 8.4  | RETCON pre-commit repair algorithm                                                   |    |

| 8.5  |                                                                                      | 35 |

| 8.6  | A conflict idiom that RETCON can repair                                              |    |

| 8.7  | -                                                                                    | 37 |

| 8.8  |                                                                                      | 38 |

| 8.9  | Generating a constraint from multiple branches                                       |    |

|      | A conflict idiom that RETCON cannot repair                                           |    |

|      | A conflict idiom that RETCON cannot repair                                           |    |

|      | A conflict idiom that RETCON cannot repair                                           |    |

|      |                                                                                      | 42 |

|      |                                                                                      | 43 |

|      | -                                                                                    | 44 |

|      |                                                                                      |    |

| 9.1  |                                                                                      | 50 |

| 9.2  | Breakdown of RETCON execution time                                                   | 50 |

| 9.3  | Performance of variants of RETCON                                                    | 51 |

| 9.4  | Impact of inexact constraint representation on RETCON performance                    | 52 |

| 9.5  | Impact of serial reacquire at commit on RETCON performance   | 154 |

|------|--------------------------------------------------------------|-----|

| 9.6  | Impact of serial reacquire RETCON time in transaction commit | 154 |

| 9.7  | Impact of RETCON structure sizes on performance              | 155 |

| 9.8  | Impact of varying size of RETCON predictor                   | 157 |

| 9.9  | Impact of varying counter size of RETCON predictor           | 158 |

| 9.10 | Impact of varying training ratio of RETCON predictor         | 159 |

| 9.11 | Percentage of time that RETCON structures are non-empty      | 161 |

# **List of Tables**

| 3.1 | Workloads used in this dissertation         | 42  |

|-----|---------------------------------------------|-----|

| 3.2 | Simulated machine configuration             | 45  |

| 9.1 | Simulated RETCON configuration              | 148 |

| 9.2 | Limit study of RETCON structure utilization | 155 |

| 9.3 | RETCON structure utilization                | 156 |

## **Chapter 1**

# Introduction

With shared-memory multiprocessing becoming the norm in contexts ranging from webservers to mobile devices, the task of developing high-performance parallel programs is being faced by more programmers than ever before. One key challenge in developing such programs is the need to synchronize accesses to shared memory made by different threads. Implementing synchronization that is both (1) correct and (2) not a performance bottleneck has historically been a challenging task. The focus of this dissertation is ameliorating the challenge of high-performance synchronization in shared-memory parallel programs.

Today's dominant synchronization mechanism is *locks*. Programmers associate locks with pieces of data and use locks to serialize access to their associated data. Locks present a well-known correctness/performance tradeoff: for ease of reasoning, it is desirable to associate locks with data at a *coarse granularity*, but to avoid serialization, it is typically necessary to associate locks with data at a *fine granularity*.

Partly in response to the challenges of programming with locks, Herlihy and Moss [47] proposed an alternative synchronization mechanism, *transactional memory*. *Memory transactions* are segments of code that have the semantics of executing serially with respect to each other. In reality, however, the system executes them speculatively in parallel, detecting cases where transactions access the same data in a conflicting way and rolling back to preserve the appearance of serial execution. This combination of an interface of serialization with an implementation of speculative parallelism has potential to ease the correctness/performance tension of locks. Current multiprocessors can be extended to support transactional memory in hardware with high concurrency and low overheads as long as transactions are small (*e.g.*, fit in the L1 cache) and exhibit little-to-no data contention [21]. Unfortunately, ensuring that transactions have these properties is likely to be nearly as challenging as achieving high performance using locks for non-expert developers. To help increase the utility of transactional memory as a general-purpose synchronization primitive, this dissertation has two goals. First, we seek to support unbounded transactions in hardware with high performance and low complexity. Second, we seek to increase the performance robustness of hardware transactional memory (HTM) to data conflicts, which we find to be the primary limitation to high performance. In particular, we seek to eliminate the performance impact of a commonly-occurring pattern of conflicts on auxiliary data, *i.e.* conflicts on data that is peripheral to a transaction's main computation. These conflicts can significantly degrade performance by inducing serialization into otherwise-parallel operations.

In the next section we outline the challenge of synchronization in shared-memory parallel programs, including the difficulties of programming with locks. Section 1.2 describes the promise of transactional memory and the challenges that this dissertation addresses. Section 1.3 presents our proposals for supporting unbounded transactions in hardware via the *permissions-only cache* and ONETM. Section 1.4 describes RETCON, our mechanism that increases the robustness of transactional memory to conflicts on auxiliary data. Finally, we detail the main contributions of the dissertation (Section 1.5), present the dissertation's structure (Section 1.6), and outline the differences between this dissertation and previously published versions of this work [9, 11, 12, 13] (Section 1.7).

## 1.1 The Problem of Synchronization in Shared-Memory Parallel Programs

A shared-memory parallel program is one in which multiple threads of execution operate concurrently in a single shared address space such as that provided by a shared-memory multiprocessor with the goal of accelerating performance over a sequential implementation. By default, the operations of threads are allowed to be interleaved at the granularity of individual memory accesses. However, program semantics often require that a given set of memory accesses by one thread be performed serially with respect to other threads (for example, if a thread in a banking application that moves money from one account to another, a different thread should not be able to observe the intermediate state where the money is in neither bank account). Enforcing such serialization is the role of a synchronization primitive.

For programs that access shared data in a regular fashion (*e.g.*, a scientific workload where execution is divided into phases of private computation and phases of merging results), it is often sufficient to be able to ensure that all threads have reached a certain point in the program before any thread proceeds past that point. Barriers are a mechanism that enforce this property, having the semantics that all threads must reach the barrier before any thread can proceed past the barrier.

For programs such as the banking application described above that access shared data in an *irregular fashion*, however, barriers alone are insufficient. The current dominant synchronization primitive for handling such irregular synchronization is locks. By convention, a lock is associated with a piece of data. To synchronize accesses on this data, a thread acquires the lock associated with that data before accessing the data and releases the lock only when it is finished accessing the data. In this fashion, the thread can ensure that no other thread can access the data during this time.

Locks present several programming and performance challenges. First and foremost, locks present a difficult performance/correctness tradeoff: to avoid serialization it is desirable to associate data with locks at a fine granularity, but such fine-grained locking complicates reasoning about the program and increases the likelihood of bugs. Locks also make it difficult to separate interface from implementation, as to synchronize a given object the programs using locks can deadlock if two threads acquire locks in an inconsistent order. We provide more background on shared-memory synchronization and the challenges of locks in Section 2.1.

## **1.2 Transactional Memory: Promise and Challenges**

Transactional memory [47, 57] (TM) has been proposed as an alternate synchronization primitive to locks. Memory transactions are segments of code that have the semantics of executing serially with respect to each other. In reality, the system speculatively executes transactions in parallel, rolling back when two transactions conflict to preserve transactional semantics.

Transactional memory has potential to ease the challenges of lock-based programming. By combining an interface of isolation with an implementation of parallelism, transactions can ease the

performance/correctness tension of locks. Placing code within a transaction also ensures that that code will execute in isolation regardless of how the objects being accessed are internally synchronized. Because transactions can roll back, the problem of lock ordering deadlock is eliminated.

The initial transactional memory design [47] implements transactional memory in hardware via extensions to existing on-chip structures, utilizing a multiprocessor's cache coherence protocol to detect conflicts between transactions and its on-chip memory hierarchy to buffer speculative state. This *hardware transactional memory* (HTM) design has low performance overheads and is highly concurrent in the absence of data conflicts. However, the initial HTM proposal was restricted to transactions that are *bounded in size* (do not overflow the on-chip structures) and *bounded in time* (do not execute for longer than a scheduling quantum). For many common programming idioms (*e.g.*, using transactions to synchronize tree traversals in a library data structure), bounded transactions are insufficient. **Extending hardware transactional memory to provide support for unbounded transactions is the first goal of this dissertation.**

Supporting transactions of unbounded size is not the only challenge facing transactional memory, however. Our study of naively-written transactional workloads reveals that once size is eliminated as a constraint, conflicts form the dominant remaining performance bottleneck. In particular, we find a common pattern of *conflicts on auxiliary data*. Auxiliary data is simply data that is peripheral to a transaction's main computation, such as reference counts of shared objects, occupancy fields of hashtables, or simple performance counters. Conflicts on such data can cause significant performance loss. These conflicts are especially damaging because they induce serialization of operations that are *conceptually non-conflicting*, *e.g.*, simultaneous reads of a reference-counted shared object. **Increasing the robustness of hardware transactional memory to auxiliary data conflicts is the second goal of this dissertation.**

In the next two sections we outline our proposals for supporting unbounded transactions in hardware and increasing the robustness of transactional memory to auxiliary data conflicts. In Chapter 2 we provide a more thorough overview of transactional memory, including the potential of transactional memory (Section 2.1), transactional memory semantics (Section 2.2), high-level implementation approaches (Section 2.3 and Section 2.4), and bounded hardware transactional memory (Section 2.6).

### **1.3 The Permissions-Only Cache and ONETM**

The primary challenge in designing unbounded hardware transactional memory is that because transactional workloads largely do not yet exist, it is unknown how large transactions will become. If overflows of the bounded HTM are rare, it would potentially be sufficient to provide a simple, low-performance mechanism for handling them. However, if overflows are frequent, such a mechanism would cause overall performance degradation. Unfortunately, supporting unbounded transactions with the same properties of high concurrency and low overheads provided by the bounded HTM is a challenging task (Chapter 4).

Instead, we propose a decoupled approach to the problem of supporting unbounded transactions in hardware. Our first objective is to ensure that overflows of the bounded HTM are **rare**. To do so, we introduce the *permissions-only cache*, a mechanism that efficiently extends the range of the bounded HTM from kilobytes to megabytes (Chapter 5). Our second objective is to handle overflows **simply**. To do so, we introduce ONETM, a mechanism that supports overflowed transactions via selective serialization (Chapter 6). In ONETM only one overflowed transaction is allowed to execute at a time on a per-application basis, eliminating prior proposals' need to detect conflicts between an unbounded number of unbounded transactions.

The permissions-only cache seeks to reduce the rate at which transactions overflow the bounded hardware transactional memory. To do so, it exploits the observation that to detect conflicts for a given block, the bounded HTM does not need to have the data for the block but rather only needs coherence permissions to the block and the knowledge of whether the block has been read and/or written by the transaction. The permissions-only cache thus maintains only coherence permissions for transactionally-accessed blocks. This size reduction allows it to achieve a 256:1 compression ratio; *e.g.*, a 4-KB permissions-only cache can track up to a megabyte of transactionally-accessed data.

With the knowledge that the permissions-only cache will likely make overflows rare we propose ONETM, a hardware-based approach for handling overflows by bounding concurrency among overflowed transactions. We explore two implementations. ONETM-Serialized stalls all other threads in an application when one transactions overflows. ONETM-Concurrent, by contrast, provides more concurrency than ONETM-Serialized by allowing bounded transactions and non-transactional code to execute concurrently with a single overflowed transaction. Both ONETM-Serialized and

ONETM-Concurrent avoid the complex structures required by prior proposals to track an unbounded amount of state per memory block.

## **1.4 RetCon**

As described above, we find that once transaction size is eliminated as a constraint, conflicts form the primary limitation to performance on the workloads that we study. Moreover, we find a common pattern of conflicts on *auxiliary data*, *i.e.*, data that is peripheral to a transaction's main computation such as reference counts or hashtable occupancy fields. In the final part of this dissertation we aim to provide hardware support for minimizing the performance impact of auxiliary data conflicts.

To eliminate the performance impact of conflicts on auxiliary data, we exploit the facts that (1) transactions' control-flow and dataflow is generally insensitive to the exact values of auxiliary data and (2) the computation performed on auxiliary data is usually simple. We propose RETCON<sup>1</sup>, a hardware mechanism that tracks the relationship between input and output values symbolically and uses this symbolic information to transparently repair the output state of a transaction at commit (Chapter 8). Conditionals form constraints on the acceptable range of values that an input can take when reacquired at commit. At commit time, all inputs that have been lost are reacquired, constraints are checked, and outputs are recomputed.

We tailor RETCON to fit the needs of the auxiliary data present in the workloads that we evaluate. RETCON tracks an input symbolically through a sequence of loads, simple arithmetic operations, branches, and stores, with more complex computation creating a constraint that the input value be the same at commit. To track symbolic information, RETCON adds a buffer to hold the initial values of symbolically-tracked blocks, a buffer to hold constraints, and a buffer to hold symbolically-tracked stores.

### **1.5** Contributions of this Dissertation

In our view, the most important contributions of this dissertation are as follows:

<sup>&</sup>lt;sup>1</sup>Retcon, short for *retroactive continuity*, refers to soap operas' and comic books' practice of revising past events as necessary to match current reality.

- Proposes a mechanism that extends the range of bounded hardware transactional memory. The permissions-only cache exploits the fact that the information necessary for performing conflict detection can be encoded in the coherence permissions of transactionallyaccessed cache blocks; the data is not necessary. By maintaining only coherence permissions for transactionally-accessed blocks, the permissions-only cache efficiently extends the range of bounded hardware transactional memory from kilobytes to megabytes.

- Proposes a mechanism for supporting unbounded transactions in hardware with the goal of low design complexity. ONETM bounds concurrency among unbounded transactions as a means of simplifying the implementation of the uncommon case and reducing the overhead that unbounded transactions impose on the rest of the system. By bounding concurrency among unbounded transactions, ONETM eliminates prior proposals' requirements of performing conflict detection between an unbounded number of unbounded transactions. This implementation works synergistically with the permissions-only cache to create a system in which the overall performance impact of serialization on overflow is low.

- Develops an approach to the problem of conflicts on auxiliary data that allows transactions to resolve such conflicts without rollbacks. We propose a repair-based approach to eliminating the performance impact of conflicts on auxiliary data. RETCON symbolically tracks the relationship between inputs to a transaction and outputs produced by that transaction, using this symbolic information to recover from conflicts without rollback before committing a transaction.

- Quantitatively evaluates the above proposals. We evaluate our proposed mechanisms using full-system simulation. This evaluation indicates that on a set of workloads (1) the combination of the permissions-only cache and ONETM provides the performance of an idealized, fully-concurrent unbounded hardware transactional memory, and (2) RETCON significantly increases the performance of workloads exhibiting conflicts on auxiliary data.

#### **1.6 Dissertation Structure**

We organize this dissertation into three parts: first, background on transactional memory and the challenges that we seek to address; second, our proposals for supporting unbounded transactions in

hardware; and third, our proposal for increasing the robustness of transactional memory to auxiliary data conflicts. We describe the structure of each part of the dissertation below.

- Background and related work (Chapters 2, 3, and 4). We first give an overview of transactional memory in Chapter 2. We describe our experimental infrastructure and characterize the transactional behavior of the workloads that we use in Chapter 3, illustrating the impact of auxiliary data conflicts on these workloads and examining the sizes of the transactions occurring in the workloads. We present an overview of previous proposals for unbounded hardware transactional memory in Chapter 4, concluding this chapter with a discussion of the challenges inherent in supporting an unbounded number of concurrently-executing unbounded transactions.

- Supporting unbounded transactions in hardware (Chapters 5, 6, and 7). We propose the permissions-only cache as a mechanism for reducing overflows of bounded hardware transactional memory in Chapter 5. Chapter 6 presents ONETM, our proposal for unbounded hardware transactional memory that limits the number of unbounded transactions that can be executing at a time to one. We experimentally evaluate our proposals for unbounded HTM in Chapter 7, finding that the combination of the permissions-only cache and ONETM can provide the performance of an idealized, fully-concurrent unbounded hardware transactional memory on our workloads.

- Mitigating the performance impact of auxiliary data conflicts (Chapters 8 and 9). Chapter 8 describes RETCON, our proposal to mitigate the performance impact of conflicts on auxiliary data. Chapter 9 experimentally evaluates the performance impact of RETCON on our workloads.

Finally, we conclude the dissertation by summarizing our proposals and presenting opinions on future opportunities and challenges in transactional memory in Chapter 10.

#### 1.7 Differences from Previously Published Versions of this Work

This dissertation builds on material previously published by Blundell *et al.* [9, 13]. In addition, Figure 2.13 on page 37 and the text describing the implementation of the flash-clear and flash-invalidate operations in Section 2.6 are taken from Blundell *et al.* [12].

The presentation of the permissions-only cache and ONETM extends earlier work [9] by discussing the option of cleaning as a version management mechanism in addition to a log, discussing both a read-only permissions-only cache and a read-write permissions-only cache, discussing the impact of weak atomicity on the design of ONETM, and presenting pseudocode-based algorithms of our proposals. In addition, the quantitative evaluation of these proposals in this dissertation is significantly more thorough than in that earlier work, including evaluating a broader set of workloads, evaluating the impact of weak atomicity on ONETM performance, evaluating the impact of lazy clearing on ONETM-Concurrent performance, evaluating the impact of a read-only as well as a read-write permissions-only cache, evaluating the impact of the sector cache organization of the permissions-only cache, and evaluating a permissions-only cache of various sizes.

The presentation of RETCON extends earlier work [13] by presenting code examples of conflicts that RETCON can and cannot repair, evaluating the impact of imprecise constraint representation on RETCON performance, presenting evaluation data for RETCON configured to reacquire blocks serially at transaction commit, presenting evaluation data for RETCON configured with several different structure sizes, and analyzing the sensitivity of RETCON to predictor configuration.

## Chapter 2

# **Overview of Transactional Memory**

This chapter gives an overview of the basic interface and implementation space of transactional memory and presents the bounded hardware transactional memory that this dissertation employs as a foundation. The intent of this chapter is to give a framework, background, and terminology for the rest of this dissertation, not provide a complete tutorial on transactional memory. As dozens of papers on transactional memory have been published in the last several years, we refer the reader to the book by Larus and Rajwar [57] for a general introduction to transactional memory.

We first outline our problem context of synchronization in shared-memory parallel programs. We then detail the transactional memory interface in Section 2.2. In Section 2.3, we outline the basic implementation tasks required to execute memory transactions speculatively in parallel. We present three high-level algorithms for transactional memory systems and describe the challenges in implementing these algorithms entirely in software with low overheads (Section 2.4). The remainder of the chapter provides an overview of bounded hardware transactional memory. We first review multiprocessor memory systems in Section 2.5 before describing how to layer support for executing bounded transactions speculatively in parallel on top of such a memory system in Section 2.6. Finally, we present performance and semantic challenges of this bounded hardware transactional memory in Section 2.7 and close the chapter with a brief summary.

Figure 2.1: A program that requires synchronization for correct behavior. balance is a shared variable, and r1 and r2 are registers. In order to ensure that the updates of both proc1 and proc2 are reflected in the final value of balance, the programmer must ensure that proc1 executes entirely before proc2 or vice versa. In the above example proc1 and proc2 may both perform their reads of balance before either performs its update, resulting in the final value reflecting only one of the updates (the one that occurs second).

## 2.1 Synchronization in Shared-Memory Parallel Programs

This dissertation considers *shared-memory parallel programs*, *i.e.*, programs in which (a) multiple threads of execution are created and (b) these threads communicate with each other via reads and writes in a single shared memory space. As shared-memory multiprocessors (described in Section 2.5) are appearing in a broader range of computers than ever before, the task of creating shared-memory parallel programs to run on these multiprocessors is likewise becoming more common.

By default, the system interleaves different threads' memory accesses at the granularity of individual reads and writes (as described in Section 2.5). In some cases, however, a thread must make a series of accesses to memory in isolation from other processors in order to guarantee correctness. Figure 2.1 on page 11 illustrates a program in which certain interleavings of memory accesses will result in incorrect behavior and must therefore be disallowed. Enabling isolation at a granularity coarser than a single memory access is the role of a *synchronization primitive*.

Below we first describe the current dominant synchronization primitive of locks. After outlining several challenges with using locks, we then present transactional memory and outline its potential to ease these challenges.

Figure 2.2: Synchronization via locking. In order to ensure that the updates of both proc1 and proc2 are reflected in the final value of balance, the programmer uses a lock. Each thread acquires the lock before doing its computation, releasing the lock only when its computation is complete. As the semantics of the lock dictate that only thread can acquire it at a time, the computations performed by the two threads are executed sequentially.

#### 2.1.1 Synchronization via Locks

A lock is an object that only one thread can hold at a time. A lock is typically associated with a piece (or several pieces) of data. By following the convention that a thread always *acquires* the lock associated with given data before manipulating that data and *releases* the lock only when finished manipulating the data, the programmer can ensure that different threads' accesses to that data are serialized at the desired granularity. The code between a lock acquire and its matching lock release is called a *critical section*. Figure 2.2 on page 12 shows how the programmer can prevent the undesired interleavings of Figure 2.1 on page 11 by employing a lock.

Developing parallel programs that are both correct and high-performance using locks is a challenging task. The primary reasons are that (1) locks synchronize *conservatively* and (2) locks are *associated with data*. We outline the reasons that these properties make using locks challenging below.

The granularity problem. First, the fact that locks synchronize conservatively introduces a difficult performance/correctness tension. Associating locks with data at a coarse granularity (*coarsegrained locking*) eases reasoning about program correctness by reducing the number of possible interleavings between threads. It also, however, can induce unnecessary serialization: all critical sections guarded by the same coarse-grained lock are forced to execute sequentially. Conversely,

```

Hashtable::insert(k,v){

Hashtable::insert(k,v){

acquire(lock);

Elem e = Elem(k, v);

Elem e = Elem(k, v);

index = hash(k);

index = hash(k);

bucket = buckets[index];

acquire(bucket->lock);

bucket = buckets[index];

bucket->insert(e);

bucket->insert(e);

release(lock);

release(bucket->lock);

}

}

(a)

(b)

```

Figure 2.3: **Two ways to synchronize a hashtable with locks.** In (a), a single lock guards the entire hashtable. This option enables easy correctness reasoning and facilitates the synchronization of operations on the table as a whole (*e.g.*, resize). However, it results in all inserts being serialized. In (b), a lock guards each bucket. This option enables inserts to different buckets to proceed in parallel. However, it makes correctness reasoning more difficult and makes operations on the table difficult to synchronize.

associating locks with data at a fine granularity (*fine-grained locking*) can increase performance at the cost of making programs more bug-prone, difficult to reason about, and difficult to maintain. Moreover, performing locking at *too* fine a granularity can also reduce performance by inducing overheads related to the lock acquires and releases themselves.

Figure 2.3 on page 13 provides an illustration of this granularity problem. The programmer desires to create a function that inserts an element into a hashtable in a thread-safe manner. The most natural way to implement this functionality is to associate a lock with the hashtable that is acquired before any operations are performed on the hashtable (part (a) of Figure 2.3 on page 13). Unfortunately, this synchronization policy serializes all inserts to the hashtable, even if they are inserts of distinct buckets.

An alternative way to accomplish this synchronization is to associate a lock with each bucket (part (b) of Figure 2.3 on page 13). This synchronization policy enables inserts into distinct buckets to proceed in parallel. Unfortunately, it also complicates the tasks of reasoning about the correctness of the program and maintaining the program. Furthermore, it makes operations on the entire hashtable (such as resizing the hashtable) difficult to synchronize.

**Lack of encapsulation.** A second problem with locks is lack of encapsulation, which arises due to the association of locks with data. If the programmer wishes to create a critical section protect-

ing access to multiple pieces of data guarded by different locks, she must be able to acquire the locks that guard each piece of data. Achieving this property requires exposing an object's internal synchronization to the outside world.